שליטה בתפסים של SR: סמלים, פונקציות ויישומים מעשיים

תפס SR הוא מעגל אסינכרוני הפועל ללא תלות בסימני שעון, מה שהופך אותו לכלי רב -תכליתי ביישומים שונים.הוא שומר על מצב בינארי - גבוה (1) או נמוך (0) - ויכול לאחסן מידע יחיד, שהוא מחזיק עד שאותות קלט חדשים מכתיבים שינוי.אלמנט אחסון בינארי בסיסי זה בנוי באמצעות שני שערי לוגיקה צולבים, בדרך כלל ולא שערי NAND.קלט ההגדרה מפעיל את התפס, מגדיר את הפלט (Q) לגובה, ואילו קלט האיפוס (R) מגדיר את הפלט לנמוך.עם זאת, אותות גבוהים בו זמנית בשתי התשומות מובילים למצב לא מוגדר, על מעצבי תנאי להימנע.תפסים של SR אינם רק מבנים תיאורטיים;הם מיושמים במערכות מעשיות כדי להחזיק נתונים זמניים, לתמוך בתוצאות עיבוד ביניים ואף לנהל איתור שגיאות ביישומים קריטיים כמו חלל ומכשירים רפואיים, ומציגים את חישוביהם בעיצוב המעגלים הדיגיטליים.קָטָלוֹג

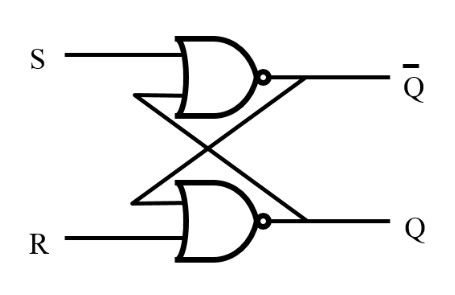

איור 1: תפס SR

מהו תפס SR?

תפס SR, או תפס סטי-סט, הוא אלמנט אחסון בינארי בסיסי השייך לקטגוריה של מעגלים אסינכרוניים.שלא כמו מעגלים סינכרוניים, תפסות SR פועלות ללא אות שעון, תוך הסתמכות אך ורק על השליטה הישירה של אותות קלט.זה מאפשר להם לתפקד באופן עצמאי בתוך מעגלים דיגיטליים.תפס SR יכול לשמור על שני מצבים יציבים: גבוה (1) ונמוך (0), ולאפשר לו לאחסן מידע יחיד עד לעדכון על ידי אותות קלט חדשים.

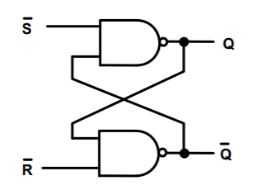

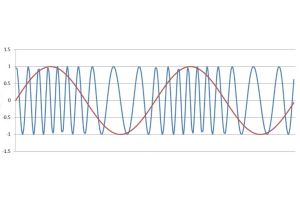

בניית תפס SR כוללת בדרך כלל שני שערי לוגיקה צולבים, בדרך כלל ולא שערים או שערי NAND.בעיצוב תפס SR באמצעות NOR NOR, הפלט של כל שער מחובר לכניסתו של האחר ויוצר לולאת משוב.תצורה זו מבטיחה כי התפס יכול לשנות במהירות מצבים בהתבסס על אותות הקלט תוך שמירה על יציבות עד שקלט חדש יבקש שינוי.

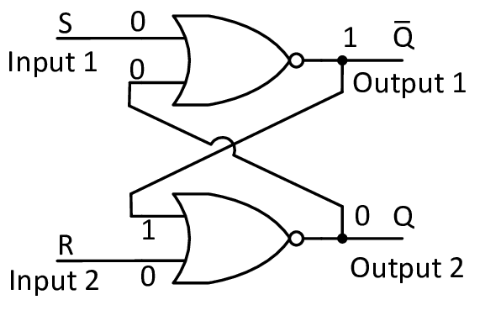

איור 2: תפס SR (2)

הגדרת קלט (ים): כאשר קלט ההגדרה מופעל (גבוה), פלט התפס (Q) עובר ל- High (1).

קלט איפוס (R): כאשר קלט האיפוס (R) מופעל (גבוה), הפלט (Q) עובר לנמוך (0).

שתי הכניסות גבוהות: אם כניסות S ו- R הן גבוהות בו זמנית, התפס נכנס למצב לא מוגדר, שיש להימנע ממנו בעיצוב.

תפסות SR חיוניות לאחסון נתונים זמני ותוצאה ביניים החזקות במערכות דיגיטליות.הם האלמנטים היסודיים במעגלים רצופים מורכבים יותר כמו רישומי משמרות מרובי סיביות, יחידות זיכרון וסוגים מסוימים של מונים.

ביישומים אלה, תפסות SR מספקות שמירת נתונים יציבה ויכולים להגיב במהירות לשינויים באותות חיצוניים, מה שמבטיח את הפעולה היעילה של המערכת האלקטרונית כולה.

יישום קריטי נוסף של תפסות SR הוא באיתור שגיאות וגיוני תיקון בתוך מעגלים דיגיטליים.בשל יכולתם להחזיק במצב יציב, הם יכולים לפקח על שינויי מצב המערכת ולחזור במהירות למצב בטוח מוגדר מראש לאחר גילוי אנומליה.תכונה זו חשובה במיוחד במערכות אמינות גבוהה כמו חלל ומכשירים רפואיים.

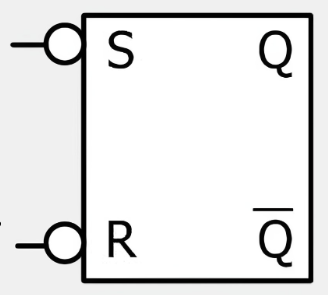

סמל תפס ה- SR

הבנת הסמל והמבנה שלו היא בסיסית לתפוס את פעולתו ושימושו המעשי.בתרשימי מעגלים, לתפס SR בדרך כלל יש שתי יציאות קלט עיקריות שכותרתו S (SET) ו- R (RESET).תשומות אלה שולטות במצב הפלט של התפס, המיוצג בדרך כלל כ- Q. כמה עיצובים כוללים גם את הפלט ההפוך, שכותרתו Q ', המספק את המצב ההפוך של Q.

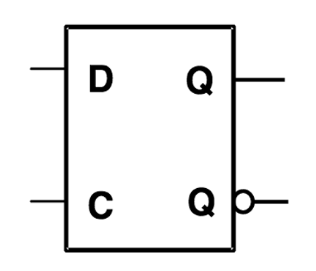

איור 3: סמל תפס ה- SR

תפס SR מיוצג לרוב על ידי סמל מלבני עם כניסות S ו- R ופלט Q. במקרים מסוימים מוצג גם Q 'הפלט.תיוג ברור זה מאפשר למעצבי מעצבים לזהות במהירות את פונקציית הרכיב ואת תפקידו במעגל הגדול יותר.

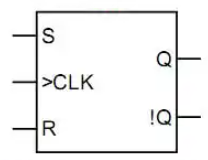

גרסה נפוצה של תפס ה- SR כוללת קלט שעון (CLK).קלט CLK מבטיח ששינויי מצב מתרחשים ב- SYNC עם אות השעון, מה שמאפשר בקרת תזמון מדויקת.במערך זה, גם אם מופעל S או R, מצב התפס מתעדכן רק כאשר אות CLK עומד בתנאים ספציפיים, בדרך כלל על הקצה העולה או הנופל.זה מונע שגיאות הנגרמות על ידי תקלות אות קלט או שינויים לא מכוונים.

איור 4: סמל תפס SR מגודר השעון

סמל התפס SR השעון כולל את כניסות ה- S, R ו- CLK בתוך מלבן.ייצוג סטנדרטי זה מסייע למעצבים להבין את הפונקציונליות של התפס ואת דרישות העיתוי שלה.לדוגמה, במערכות מחשוב בעלות ביצועים גבוהים או במערכות העברת נתונים מורכבות, בקרת CLK זהירה מבטיחה שנתונים מאוחסנים ומועברים במדויק בכל שלב עיבוד, ומיטב את ביצועי המערכת הכוללים והאמינות.

שליטה מדויקת בכניסות תפס SR חשובה, במיוחד בתכנון זיכרון מהיר וקיבולת גבוהה או מאגרי נתונים זמניים.על ידי תכנון מעגלי לוגיקה לניהול הפעלת S ו- R, ניתן להשיג פונקציות מורכבות כמו טעינת נתונים, ניקוי או איפוס מצב.בקרת אותות CLK מדויקת מבטיחה כי כל פעולות הנתונים עוקבות אחר רצף תזמון מוגדר מראש, ומשפר משמעותית את יעילות המערכת ויכולת עיבוד הנתונים.

הבנה עמוקה של סמל המבנה של תפס ה- SR מסייעת לא רק בתכנון ופתרון בעיות של מעגלים נכונים אלא גם בביצוע פעולות לוגיקה דיגיטליות מורכבות ושיפור ביצועי המערכת.זה קריטי במיוחד ביישומים הדורשים אמינות גבוהה ושליטה מדויקת, כגון תעופה וחלל ומכשירים רפואיים.

סוגי תפסים ועקרונות העבודה שלהם

תפסים הם רכיבים בסיסיים בעיצוב אלקטרוני, המציעים פונקציות מגוונות ויישומים רחבים.סוגי התפסים העיקריים הם תפסים ותפסים של SR, שלכל אחד מהם פעולות ייחודיות ומקרי שימוש.

תפס SR

תפס ה- SR, או תפס הסטים, הוא התקן אחסון בסיסי הנשלט על ידי שתי הכניסות שלו, S (SET) ו- R (RESET).

כאשר כניסת ה- S מקבלת אות גבוה, הפלט Q הופך גבוה, מה שמצביע על כך שהנתונים מוגדרים.כאשר כניסת R מקבלת אות גבוה, ה- Q הפלט הופך נמוך, מה שמצביע על כך שהנתונים מתאפסת.אם תשומות S ו- R הן גבוהות בו זמנית, התפס נכנס למצב לא מוגדר, וגורם לחוסר יציבות פוטנציאלית.יש להימנע מתנאי זה בעיצוב.התגובה הישירה של ה- SR Latch לאותות קלט הופכת אותה לשימושית במצבים הדורשים תגובה מהירה.

D Latch

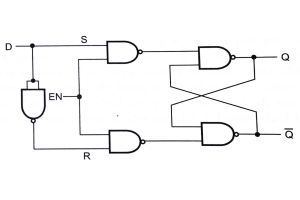

התפס D, המכונה גם תפס נתונים או תפס שקוף, מציע שליטה מורכבת יותר עם קלט נתונים D ו- CLK Skint Skint.

איור 5: D Latch

איור 6: סמל תפס D

כאשר CLK גבוה, הפלט Q עוקב אחר הקלט D, ומאפשר לנתונים לעבור את התפס בחופשיות.כאשר CLK יורד, הערך הנוכחי של D נעול, והפלט Q נשאר קבוע עד האות הגבוה הבא של CLK.מנגנון זה הופך את תפס ה- D לאידיאלי לאחסון באופן זמני של נתונים כדי לסנכרן מהירויות עיבוד שונות בתוך מערכת.

לתפסים של SR ו- D יש תפקיד שאין שני לו באחסון נתונים ובהיגיון מכונות המדינה.בשל תגובת רמת הקלט הישיר שלהם, התפסים הם חיוניים בעיצוב מעגלים אסינכרוניים.הם מספקים פונקציות חיוניות להעברות נתונים מורכבות ומערכות ניהול חשמל, ומאחסנות ביעילות מידע על מצב כדי להבטיח פעולה יציבה.שימוש נכון בתפסים אלה יכול לשפר משמעותית את אמינות ויעילות המעגלים, מה שהופך אותם לכיוניים במערכות אלקטרוניות מודרניות.

טבלת האמת של תפס SR

איור 7: SR Nand Latch

|

ג |

ר ' |

ש |

ש ' |

הערה |

|

0 |

0 |

1 |

1 |

אסור |

|

0 |

1 |

1 |

0 |

מַעֲרֶכֶת |

|

1 |

0 |

0 |

1 |

אִתחוּל |

|

1 |

1 |

ש |

ש ' |

לִשְׁמוֹר |

טבלה 1: טבלת האמת של תפס SR באמצעות שערי NAND

איור 8: SR ולא תפס

|

ג |

ר ' |

ש |

ש ' |

הערה |

|

0 |

0 |

ש |

ש ' |

לִשְׁמוֹר |

|

0 |

1 |

1 |

0 |

אִתחוּל |

|

1 |

0 |

0 |

1 |

מַעֲרֶכֶת |

|

1 |

1 |

0 |

0 |

אסור |

טבלה 2: טבלת האמת של תפס SR באמצעות שערים ולא

כעת אנו לוקחים את טבלת האמת של תפס ה- SR באמצעות NOR NOR GATE כדוגמה להבנת המשמעות של טבלת האמת של תפס ה- SR.

מצבי קלט ופלט

גם S וגם R הם 0: התפס נשאר במצבו הנוכחי.הפלט Q נשאר זהה, בין אם זה 0 או 1.

S הוא 0 ו- R הוא 1: איפוס התפס, מכריח את הפלט Q ל- 0.

S הוא 1 ו- R הוא 0: ערכות התפס, מה שהופך את הפלט Q שווה ל -1.

גם S וגם R הם 1: מצב זה אינו תקף או לא מוגדר, המכונה לעתים קרובות המדינה "האסורה" בתפס SR.במקרה זה, Q ו- Q 'שניהם שווים 0, מה שמוביל לתפוקה מעורפלת.

כאשר S ו- R הם שניהם 0, התפס לא עושה דבר ופשוט מחזיק בערכו הנוכחי.זה שימושי לשמירה על המדינה ללא שינויים.

כאשר S הוא 0 ו- R הוא 1, נאמר במפורש את התפס לאיפוס, וודא ש- Q הוא 0 ללא קשר למצבו הקודם.זוהי דרך פשוטה לפנות את התפס.

כאשר S הוא 1 ו- R הוא 0, התפס מוגדר, ומבטיח ש- Q הופך 1. כך אתה מאחסן '1' בתפס.

כאשר S ו- R הם שניהם 1, המדינה אסורה מכיוון שהיא גורמת לשני התפוקות להיות 0, וזה סותר ולא אמין.על מעצבים להימנע ממצב זה כדי להבטיח פעולה יציבה.

יתרונות וחסרונות של תפסים

תפסים נמצאים בשימוש נרחב בעיצוב מעגלים דיגיטליים בגלל הפשטות והעלות הנמוכה שלהם.מאפיינים אלה מאפשרים לתפסים לפעול במהירות גבוהה עם צריכת חשמל נמוכה, מה שהופך אותם לאידיאליים למערכות דיגיטליות במהירות גבוהה.לדוגמה, בקבצי רישום מעבדים, תפסים יכולים לאחסן ולאחזר במהירות נתונים, ולהגביר משמעותית את מהירות העיבוד והיעילות.

יתרונות תפסים

פשטות ואפקטיביות עלות: תפסים הם רכיבים פשוטים זולים ליישום במעגלים דיגיטליים.

מהירות גבוהה ועוצמה נמוכה: העיצוב שלהם מאפשר פעולה מהירה עם צריכת חשמל מינימלית, שהיא קריטית במערכות דיגיטליות במהירות גבוהה.

יעילות בטיפול בנתונים: ביישומים כמו קבצי רישום מעבדים, התפסים מספקים אחסון ושליפה מהיר של נתונים, ומשפרים את ביצועי המערכת הכוללים.

חסרונות של תפסים

למרות היתרונות שלהם, לתפסים יש מגבלות בולטות בעיצובים ויישומים מסוימים.

התנהגות בלתי צפויה בעיצובים אסינכרוניים: ללא בקרת אות שעון, תפסים יכולים להתנהג באופן בלתי צפוי.בתפסים של SR, אם כניסות ה- SET (ים) וגם האיפוס (R) גבוהות בו זמנית, הפלט הופך ללא הגדרה, מה שמוביל לחוסר יציבות.זה בעייתי בבקרה בזמן אמת או ביישומים קריטיים בטיחותיים, כאשר התפוקה האמינה היא מכריעה.

עיצוב תזמון מורכב: תכנון עם תפסים דורש שיקולי תזמון מדוקדקים.על המהנדסים להסביר עיכובים בהפצת אות ותנאי המירוץ כדי למנוע שגיאות תזמון.תכנון לא תקין יכול לגרום לשינויי נתונים לפני שהאות השעון מתייצב, וגורם לשחיתות נתונים או לכידת נתונים שגויה.זה מחייב הבנה מעמיקה של ניתוח התזמון והתנהגות המעגלים.

כדי להתמודד עם אתגרים אלה, ניתן להשתמש בטכניקות ואסטרטגיות עיצוביות ספציפיות:

מנגנוני סנכרון: הוספת מנגנוני סנכרון יכולה לעזור בניהול תשומות אסינכרוניות ולהפחית התנהגות בלתי צפויה.

ניהול שעון מותאם אישית: יישום אסטרטגיות ניהול שעון בהתאמה אישית יכול להבטיח כי הנתונים נצמדו כראוי ובזמנים הנכונים.

שימוש בכלי EDA: כלי אוטומציה של עיצוב אלקטרוני מודרני (EDA) מציעים יכולות ניתוח ואופטימיזציה מתקדמות.כלים אלה עוזרים לחזות ולפתור בעיות תזמון וסנכרון בשלב העיצוב, ומשפרות את האמינות והביצועים של מערכות דיגיטליות באמצעות תפסים.הם מסייעים למעצבים בזיהוי בעיות פוטנציאליות מוקדם, להבטיח שהתוצר הסופי פועל באופן אמין בתנאים שונים.

יישומים מעשיים של תפסות SR

תפסות SR, הידועות ביכולתם לשמור במהירות ובאמינות, בשימוש נרחב במערכות אלקטרוניות שונות.הם מצטיינים בתרחישים הדורשים אחסון נתונים זמני או שמירת מדינה.

אחסון נתונים זמני

תפסות SR משמשות לרוב בזיכרון המטמון כדי לאחסן נתונים באופן זמני.זה מאפשר למערכת לגשת במהירות לנתונים המשמשים לעתים קרובות, ולהגדיל משמעותית את יכולות עיבוד הנתונים ואת היעילות של מעבדי בקנה מידה גדול.

קבצי רישום אחסון

במעבדים, תפסות SR מאפשרות אחסון ושליפה מהירה של נתונים בקבצי רישום, משפרים את מהירות העיבוד וביצועי המערכת הכוללים.

שמירה על אותות בקרה

במערכות בקרה דיגיטליות, תפסות SR מועילות לשמירה על מצב אותות בקרה מסוימים עד שתנאים חיצוניים או לוגיקה של מערכת מכתיבים שינוי.כמו כן, הם עוזרים בשמירה על מדינות במערכת, ומבטיחים ביצועים עקביים בפעולות הדורשות דיוק ואמינות.

מעגלים מפעילים ומגזים

כפכפים מבוססי תפס SR משמשים בדרך כלל במעגלים הדורשים פעולה מסונכרנת, כגון שעונים דיגיטליים וטיימרים.הם שולטים בפולסים של ספירה, ומבטיחים שמירת זמן מדויקת וביצועים אמינים.מעגלים אלה מסתמכים על תפסים SR לשמירה על ספירות מדויקות, המאפשרות תזמון ורצף במערכות דיגיטליות.

אינטראקציות מכניות

תפסים של SR יעילים לביטול הקפצה מכנית במתגים.קפיצה מכנית מתרחשת כאשר מתג מייצר שינויי אות מהיר וחוזר על עצמו כתוצאה ממגע לקוי.תפסות SR מייצבות את אות הפלט, ומונעות שגיאות הנגרמות על ידי אותות רועשים.

כפכף SR

כפכף SR, המכונה לעתים קרובות כפכף מפלג סט-סטור המופעל על ידי קצה, מורכב משני תפסים SR הקשורים זה לזה.מבנה תפס כפול זה מאפשר לה להגיב לקצוות אותות שעון ספציפיים (עולה או נפילה) כדי לשנות את מצבו.זה מושג באמצעות בקרת היגיון מיוחדת בין התפסים.הפלט של התפס הראשון הופך לחלק מהקלט לתפס השני, ופלט התפס השני, בתורו, משפיע על התפס הראשון ויוצר לולאת משוב משתלבת.

איור 7: SR Flip-Flop

כפכפי ה- SR משנה את המצב בדיוק במדויק בקצה העולה או הנופל של אות השעון.המשוב המשתלב בין שני תפסות ה- SR מבטיח כי הכפכף משנה רק את מצבם בתגובה לקצה השעון, ומספק פלט יציב ואמין.

במעבדי מיקרו ומעבדי אותות דיגיטליים, כפכפי SR משמשים לדגימה ואחסון נתונים.הם תופסים ומייצבים נתונים בקצוות שעון שצוינו, ומבטיחים עיבוד וניתוח נתונים אמינים לאחר מכן.

מנגנון ההפעלה קצה מסייע במניעת תנאי גזע, כאשר חלקים שונים במעגל עשויים לשנות את המצב בו זמנית ללא סנכרון, מה שעלול לגרום לתפוקות לא יציבות או שגויות.כפכפי SR הם מכריעים ביישום היגיון פרוטוקול תקשורת ספציפי, כגון סנכרון מסגרת וגילוי שגיאות.היציבות וזמן התגובה המהירה שלהם עוזרים לשמור על איכות העברת נתונים ואמינות המערכת.

מדינות אסורות בתפס SR וכפכפי SR

בעת תכנון תפסים של SR וכפכפי SR באמצעות NAND ולא שערים, כולנו צריכים לשים לב לניהול והימנעות ממדינות מעוכבות.מצב אסור מתרחש כאשר כניסות הסט (ים) וגם האיפוס (R) הם גבוהים בו זמנית (עבור שערי NAND) או נמוכים (עבור Nor Nor Gates).שילוב זה מוביל למצב פלט בלתי מוגדר, שכן הפלט תלוי במצב הקודם של המעגל, מה שהופך אותו לבלתי צפוי.

מדינות אסורות בשער Nand Sr תפסים

כאשר S וגם R הם נמוכים, שתי התפוקות עולות גבוהות, מה שמפר את מאפיין התפוקה המשלים של התפס.התוצאה היא מצב בלתי מוגדר.

מדינות אסורות ב- Nor Gate Sr תפסים

כאשר שניהם ו- R הם גבוהים, שתי התפוקות יורדות, ויוצרות גם מצב בלתי מוגדר.זה יכול להוביל להתנהגות בלתי צפויה במעגל.

גישות מעשיות להימנע ממדינות אסורות

הוספת היגיון שליטה

השתמש בשערי לוגיקה נוספים כדי לפקח על מצבי S ו- R. אם שתי הכניסות מגמות למצב אסור, התאם אוטומטית קלט אחד כדי למנוע את המצב הבלתי מוגדר.זה מבטיח כי התפוקות יישארו יציבות וצפויות.יישום שער לוגיקה שמתערב כאשר S ו- R הם שניהם גבוהים (או נמוכים), ומתאמת קלט אחד לשמירה על מצב תקף.

סימולציה של תוכנה ובדיקת חומרה

ערכו הדמיות תוכנה יסודיות כדי לזהות מצבים אסורים פוטנציאליים בתנאי הפעלה שונים.זה מאפשר למעצבים לאתר ולתקן שגיאות לוגיות לפני היישום הפיזי.בצע בדיקות חומרה נרחבות כדי לאמת כי המעגל מטפל נכון בכל שילובי הקלט.שלב זה עוזר להבטיח כי התפס או הכפכף פועלים באופן אמין בתרחישים בעולם האמיתי.

סיכום

הרבגוניות והאמינות של תפס SR מדגישים את חשיבותם בעיצוב המעגלים הדיגיטליים.על ידי בחינת ההתנהגות הניואנסית של תפס SR באמצעות ייצוגי הסמל שלהם, טבלאות האמת ויישומים מעשיים, אנו מקבלים הבנה מקיפה של פעולתם וחשיבותם.למרות החסרונות הפוטנציאליים של מצבים לא מוגדרים בעיצובים אסינכרוניים, יישום אסטרטגי של היגיון בקרה והדמיה נרחבת יכולים להקל על סיכונים אלה.כלים מתקדמים לתכנון אלקטרוני אוטומציה (EDA) משפרים עוד יותר את האמינות והביצועים של מעגלים הכוללים תפסים של SR על ידי חיזוי ופתרון בעיות תזמון וסנכרון.בין אם משתמשים באחסון נתונים זמני, תחזוקת אותות בקרה או איתור שגיאות, תפס SR מוכיח כיסוד ביצירת מערכות דיגיטליות חזקות ויעילות.תפקידם בפעולות זיכרון במהירות גבוהה ועיבוד נתונים סינכרוני ביישומים מורכבים מדגים את הרלוונטיות המתמשכת שלהם.ככל שהטכנולוגיה מתקדמת, העקרונות הנוגעים לתפסים של SR ממשיכים ליידע ולעורר חידושים באלקטרוניקה דיגיטלית, ומבטיחים כי רכיבים יסודיים אלה יישארו אינטגרליים בפיתוח מכשירים אלקטרוניים מתוחכמים ואמינים.

שאלות נפוצות [שאלות נפוצות]

1. מהי תפס SR?

תפס SR, או תפס סטי-סט, הוא אלמנט אחסון בינארי בסיסי המשמש במעגלים דיגיטליים.זהו מעגל אסינכרוני, כלומר הוא פועל ללא אות שעון, תוך הסתמכות על השליטה הישירה של כניסותיו לשינוי מצבים.

2. מה הפונקציה של SR בהיגיון?

בהיגיון, כניסות ה- SR (SET-Reset) שולטות במצב התפס.

3. באיזה סוג שער לוגיקה משתמש בתפס SR?

תפס SR בדרך כלל משתמש בשערים או בשערי NAND.בתפס SR מבוסס-שער, הפלט של כל אחד ולא שער מוזן בחזרה לכניסתו של האחר, ויוצר לולאת משוב יציבה.בתפס SR מבוסס NAND, משתמשים בתצורת משוב דומה, אך רמות ההיגיון הפוכות בהשוואה לתפס מבוסס NOR.שתי התצורות משיגות את אותה פונקציונליות בסיסית של שמירה על מצב בינארי על בסיס התשומות של SET ו- RESET.

4. איך תפס עובד?

תפס פועל באמצעות משוב לשמירה על מצב הפלט שלה על סמך התשומות שסופקו.בתפס SR, הסטים (ים) ותשומות האיפוס (R) שולטים על מצב הפלט (Q).כאשר קלט ההגדרה מופעל (גבוה), הפלט מוגדר לגובה (1).כאשר כניסת האיפוס מופעלת (גבוהה), הפלט מתאפס לנמוך (0).לולאת המשוב בתכנון התפס מבטיחה כי ברגע שנקבע מצב פלט הוא נשאר יציב עד שאות קלט חדש ישנה אותו.

5. מה החיסרון עם תפס SR?

החיסרון העיקרי של תפס SR הוא המצב הבלתי מוגדר המתרחש כאשר שניהם מוגדרים (ים) וגם תשומות איפוס (R) גבוהות בו זמנית.מצב זה מוביל למצב תפוקה בלתי מוגדר, העלול לגרום לחוסר יציבות ולהתנהגות בלתי צפויה במעגלים דיגיטליים.יש להימנע ממדינה "אסורה" זו בתכנון כדי להבטיח פעולה אמינה.

תפס SR, תפס סטים, מעגל אסינכרוני, אלמנט אחסון בינארי, מעגלים דיגיטליים, לא שערים, שערי NAND, לולאת משוב, מצב גבוה, מצב נמוך, מצב לא מוגדר, אות שעון, בקרה ישירה, אחסון נתונים זמני, אחיזת תוצאה ביניים,איתור שגיאות, יישומי תעופה וחלל, מכשירים רפואיים, תכנון מעגלים, תפס SR שעון, אותות קלט, סמל ומבנה, זיכרון במהירות גבוהה, מאגרי נתונים, בקרת תזמון, בקרה מדויקת, שמירת מצב, מעבדי מיקרו, מעבדי אות דיגיטליים, דגימת נתונים, נתוניםאחסון, מופעל קצה, כפכף SR, משוב משולב, תנאי מירוץ, היגיון פרוטוקול תקשורת, סנכרון מסגרות, איתור שגיאות, תקלות אות, אוטומציה של עיצוב אלקטרוני, כלי EDA, מנגנוני סנכרון, ניהול שעון בהתאמה אישית, שגיאות תזמון, עיכובי התפשטות,תנאי מירוץ, העברות נתונים מורכבות, מערכות ניהול חשמל, כניסה מכנית, יישומים מעשיים, מערכות בקרה דיגיטליות, שערי לוגיקה, הדמיות תוכנה, בדיקות חומרה, מצבים אסורים, אמינות תפס.

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

מדריך ליסודות ה- D כפכפים - מעגלים, טבלאות אמת, סוגים, יתרונות ומגבלות

ב- 2024/05/17

מדריך השוואתי לניתוח ריאוסטט ופוטנציומטרים

ב- 2024/05/17

פוסטים פופולריים

-

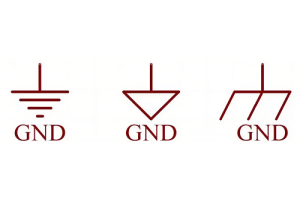

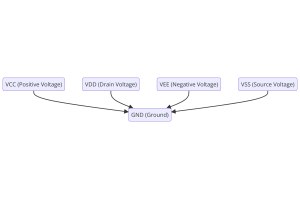

מה זה GND במעגל?

ב- 1970/01/1 2946

-

מדריך מחברים RJ-45: RJ-45 קודי צבע מחבר, תוכניות חיווט, יישומי R-J45, גיליון נתונים RJ-45

ב- 1970/01/1 2502

-

סוגי מחברי סיבים: SC לעומת LC ו- LC לעומת MTP

ב- 1970/01/1 2091

-

הבנת מתחי אספקת חשמל ב- Electronics VCC, VDD, VEE, VSS ו- GND

ב- 0400/11/9 1898

-

השוואה בין DB9 ל- RS232

ב- 1970/01/1 1765

-

מהי סוללת LR44?

חשמל, אותו כוח בכל מקום, מחלחל בשקט כל היבט בחיי היומיום שלנו, מגאדג'טים טריוויאליים ועד ציוד רפואי מסכן חיים, הוא ממלא תפקיד שקט.עם זאת, באמת לתפוס את האנרגיה הזו, במיוחד כיצד לאחסן ולהפוך אותה ביעילות, זו לא משימה קלה.זה ע...ב- 1970/01/1 1714

-

הבנת היסודות: התנגדות השראות, וציון

בריקוד המורכב של הנדסת חשמל, שלישיית אלמנטים בסיסיים עולה במרכז הבמה: השראות, התנגדות וקיבול.כל אחת מהן נושאת תכונות ייחודיות המכתיבות את המקצבים הדינמיים של מעגלים אלקטרוניים.כאן אנו יוצאים למסע לפענוח המורכבות של רכי...ב- 1970/01/1 1662

-

מדריך מקיף של CR2430 סוללה: מפרט, יישומים והשוואה לסוללות CR2032

מהי סוללת CR2430?היתרונות של סוללות CR2430נוֹרמָהיישומי סוללה CR2430CR2430 שווה ערךCR2430 לעומת CR2032גודל CR2430 סוללהמה לחפש בעת קניית CR2430 ושוויוןגיליון נתונים PDFשאלות נפוצות סוללות הן לבם של מכשירים אלקטרוניים קטנים.בין הסוגים הרבים הק...ב- 1970/01/1 1567

-

מה זה RF ולמה אנו משתמשים בזה?

טכנולוגיית תדר רדיו (RF) היא חלק מרכזי בתקשורת אלחוטית מודרנית, המאפשרת העברת נתונים למרחקים ארוכים ללא חיבורים פיזיים.מאמר זה מתעמק ביסודות ה- RF, ומסביר כיצד קרינה אלקטרומגנטית (EMR) מאפשרת תקשורת RF.נחקור את עקרונות ה- EMR, את...ב- 1970/01/1 1550

-

CR2450 לעומת CR2032: האם ניתן להשתמש בסוללה במקום זאת?

לסוללות ליתיום מנגן יש כמה קווי דמיון עם סוללות ליתיום אחרות.צפיפות אנרגיה גבוהה וחיי שירות ארוכים הם המאפיינים המשותפים להם.סוללה מסוג זה זכתה באמון ובחובם של צרכנים רבים בגלל בטיחותה הייחודית.גאדג'טים טכניים יקרים?מכ...ב- 1970/01/1 1519