XCV200-6FG456C FPGA: תכונות, מפרטים, תכנות ויישומים

ה- XCV200-6FG456C הוא FPGA חזק (מערך שער הניתן לתכנות שדה) מסדרת AMD Xilinx Virtex®.מדריך זה מסביר את תכונותיו, פריסת סיכות, שלבי תכנות ושימושים.עם כוח עיבוד גבוה, אפשרויות עיצוב גמישות ויכולות קלט/פלט חזקות (קלט/פלט), FPGA זה מסייע בבניית מערכות דיגיטליות מהירות ואמינות.בין אם אתה עובד על רשת, מערכות בקרה או אלקטרוניקה בהתאמה אישית, מדריך זה יעזור לך להבין כיצד ניתן להשתמש ב- XCV200-6FG456C בפרויקטים שלך.קָטָלוֹג

סקירה כללית של XCV200-6FG456C

THE XCV200-6FG456C הוא מודל בולט במשפחת AMD Xilinx Virtex® FPGA, שנועד לספק פתרונות לוגיים חזקים לתכנות למערכות דיגיטליות מורכבות.שבב ספציפי זה מקיף כ 236,666 שערי מערכת וכולל 1,176 בלוקי לוגיקה הניתנים להגדרה (CLBS) ו- 5,292 תאי לוגיקה.זה כולל גם 57,344 ביטים של זיכרון RAM כולל ותומך ב 284 סיכות קלט/פלט, שוכנות בחבילת מערך כדורי כדורים משובח של 456 כדור (FBGA), בגודל 23 מ"מ x 23 מ"מ.מודל זה פועל על מתח נומינלי 2.5 וולט, עם טווח של 2.375 וולט עד 2.625 וולט, ויכול לתפקד בטווח טמפרטורה של 0 מעלות צלזיוס עד 85 מעלות צלזיוס.סדרת Virtex® הרחבה יותר מתאימה למגוון יישומים עם צפיפות בין 50,000 ליותר ממיליון שערי מערכת ושיעורי שעון מערכת של עד 200 מגהרץ.זה תומך בתקני קלט/פלט רבים כולל LVTTL, LVCMOS ו- PCI, בין היתר.תכונות כמו לולאות נעילות עיכוב (DLLs), חסימות לוגיקה הניתנות להגדרה עם זיכרון משובץ, ולוגיקת נשיאה ייעודית לפעולות חשבון משפרות את הפונקציונליות שלה.משפחת Virtex® Virtex® מבטיחה ביצועים ואמינות של 0.22 מיקרומטר 5 שכבות.

אם אתה מחפש לשלב טכנולוגיית FPGA מהשורה הראשונה במוצרים או במערכות שלך, קניית XCV200-6FG456C בתפזורת איתנו היא מהלך חכם.זה עונה על תקני התעשייה ושומר עליך לפני צרכי הטכנולוגיה העתידיים.

תכונות XCV200-6FG456C

• • שערי מערכת: XCV200-6FG456C מציע כ 236,666 שערי מערכת.ספירת שער גבוהה זו מאפשרת ליישם מעגלי לוגיקה דיגיטליים משולבים מורכבים על שבב יחיד, ומשפרת הן את הביצועים והן הרבגוניות במגוון יישומים.

• • משאבי לוגיקה: הוא כולל 1,176 בלוקי לוגיקה הניתנים להגדרה (CLBS) ו- 5,292 תאי לוגיקה.משאבים אלה טובים לעיצוב מעגלים דיגיטליים גמישים וניתנים להרחבה.ניתן לתכנת CLBS לבצע מגוון רחב של פונקציות לוגיות, ואילו המספר הגדול של תאי הלוגיקה מאפשר טיפול בפעולות ותהליכים לוגיים נרחבים.

• • זֵכֶר: המכשיר מספק 57,344 פיסות זיכרון RAM, המופצות בין בלוקי ההיגיון שלו.זיכרון RAM משובץ זה משמש ליישומים הדורשים אחסון ושליפה מהירה ויעילה של נתונים, ותומכים בפעולות נתונים במהירות גבוהה אינטגרליות למערכות דיגיטליות מודרניות.

• • יכולות קלט/פלט: עם 284 סיכות קלט/פלט, XCV200-6FG456C מאפשר יכולות ממשק נרחבות.סיכות קלט/פלט אלה תומכות בתקני אות שונים ומאפשרים ל- FPGA לתקשר ביעילות עם רכיבים אחרים במערכת, כמו מכשירי זיכרון, מעבדים והיקפי ציוד היקפי.

• • טווח מתח וטמפרטורות: פועל במתח נומינלי של 2.5 וולט, עם טווח מקובל בין 2.375V ל- 2.625V, FPGA זה מיועד לצריכה בעלת כוח נמוך תוך שמירה על ביצועים חזקים.הוא יכול לפעול בטווח טמפרטורת צומת של 0 מעלות צלזיוס עד 85 מעלות צלזיוס, ולהבטיח אמינות בתנאים סביבתיים משתנים.

XCV200-6FG456C תרשים פונקצית PIN

THE XCV200-6FG456C תרשים פונקצית PIN הוא ייצוג מובנה של משימות ה- PIN של ה- FPGA, המסווג לבנקים שונים (בנק 0 לבנק 7).כל בנק מקבץ סיכות על סמך תפקידם ומיקומם הפיזי בחבילת FPGA.מערכת המספור והתווית עוקבת אחר תבנית רשת בה שורות מסומנות על ידי אותיות (A, B, C וכו '), ועמודות לפי מספרים (1, 2, 3 וכו'), המאפשר זיהוי מהיר של סיכות ספציפיות.בנקים אלה תואמים פונקציות קלט/פלט שונות, כוח, קרקע וניתוב אותות ייעודיים.סיכות מוקצות לקבוצות פונקציונליות שונות, כולל קלט/פלט לשימוש כללי (GPIO), שכותרתו לעתים קרובות "G" (קלט/פלט כללי), "V" (אספקת מתח) ו- "O" (פלט).סיכות כוח וקרקע מסומנות באופן מובהק, ומבטיחות פעולת FPGA יציבה.סיכות לשימוש מיוחד כמו כניסות שעון, איפוס ואותות בקרה מזוהים עם סמלים כמו "r" או "T."חלק מהסיכות משרתות גם תפקידי תקשורת ייעודיים, כולל תצורת JTAG ועלייה במהירות גבוהה, לתכנות ובניפוי באגים.

XCV200-6FG456C תרשים בלוק

חסימת קלט/פלט

התרשים מייצג את חסימת קלט/פלט (IOB) מבנה ה- XCV200-6FG456C FPGA, שהוא חבר במשפחת Xilinx Virtex.התרשים מציג אלמנטים מרכזיים המעורבים בפעולות קלט ופלט, ומדגיש את מנגנוני זרימת הנתונים והבקרה.בליבת התרשים משתמשים בשלושה כפכפים D כפכפים לרישום אותות לבקרת קלט, פלט ושלוש מדינות.פנקס הפלט נשלט על ידי האות OCE (שעון פלט מאפשר), שקובע מתי נתוני הפלט נצמד.באופן דומה, פנקס ה- Tri-State נשלט על ידי ה- TCE (שעון Tri-State Enable), ומאפשר או השבתת מאגר הפלט.פנקס הקלט לוכד נתונים נכנסים ומיישם עיכוב ניתן לתכנות לפני שהוא מעביר אותם ללוגיקה הפנימית של FPGA דרך ה- IBUF (חיץ קלט).ה- Obuft (חיץ פלט משולש) מבטיח כי ה- FPGA יכול להניע אות על הכרית (סיכת קלט/פלט) או למקם אותו במצב עכבה גבוה, תלוי בהיגיון הבקרה.מעגל שומר חלש כלול על הכרית לשמירה על מצב ההיגיון האחרון הידוע כאשר אין נהג פעיל, ומונע תנאים צפים לא מכוונים.מתח ההתייחסות (VREF) משמש לתקני קלט מסוימים, כגון SSTL או HSTL, הדורשים רמות מתח מדויקות להפעלה נאותה.בסך הכל, מבנה IOB זה מאפשר ל- FPGA לנהל העברת נתונים במהירות גבוהה, לתמוך בתקני קלט/פלט שונים ולספק שליטה גמישה על תזמון האות ויושרה.

מצב סידורי מאסטר/עבדים

THE מצב סידורי מאסטר/עבדים תרשים חסימה ממחיש את תהליך התצורה של FPGA של Virtex, במיוחד XCV200-6FG456C, כאשר מתוכנת בתצורת שרשרת חיננית באמצעות EEPROM סדרתי (XC1701L).בהגדרה זו, מכשיר Virtex אחד פועל כמאסטר, שולט על שעון התצורה (CCLK) ומעביר נתוני תצורה סדרתיים ל- FPGAs עבדים נוספים בשרשרת.ה- Master FPGA יוזם את תהליך התצורה על ידי קביעת אות התוכנית, מאפס את כל המכשירים בשרשרת.לאחר השלמת האתחול, אות ה- init מציין מוכנות, ונתוני התצורה זורמים מה- EEPROM הסידורי (XC1701L) ל- DIN (נתונים IN) של ה- FPGA הראשי.ה- FPGA הראשי קורא נתונים מ- EEPROM ומעביר אותם דרך DOUT (DATA OUT) ל- FPGAs עבדים לאחר מכן, מסנכרן העברת נתונים באמצעות אות CCLK.האות שנעשה משמש כדי לציין תצורה מוצלחת, כאשר נגדי משיכה אופציונלי מבטיח מצב גבוה יציב כאשר התצורה הושלמה.ה- XC1701L EEPROM נשלט על ידי ה- FPGA הראשי באמצעות CLK, Data, CE (ChIP Enable) ו- Reset/OE (פלט הפעלת), ומבטיח כי נתוני התצורה המאוחסנים יאוחזרו כראוי.שיטת תצורה זו יעילה לתכנות FPGAs מרובים באמצעות EEPROM יחיד, הפחתת מורכבות חיווט חיצונית והבטחת כל המכשירים לקבל נתוני תצורה מסונכרנים.

מפרטי XCV200-6FG456C

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

AMD XILINX

|

|

סִדרָה |

Virtex® |

|

אריזה |

מַגָשׁ |

|

סטטוס חלק |

מְיוּשָׁן |

|

מספר המעבדות/CLBs |

1176 |

|

מספר אלמנטים/תאים לוגיים |

5292 |

|

סה"כ פיסות זיכרון RAM |

57344 |

|

מספר קלט/פלט |

284 |

|

מספר השערים |

236666 |

|

מתח - אספקה |

2.375V ~ 2.625V |

|

סוג הרכבה |

הר השטח |

|

טמפרטורת הפעלה |

0 ° C ~ 85 ° C (TJ) |

|

חבילה / מקרה |

456-BBGA |

|

חבילת מכשירי ספק |

456-FBGA (23x23) |

|

מספר מוצר בסיס |

XCV200 |

יישומי XCV200-6FG456C

טלקומוניקציה ורשתות

ה- XCV200-6FG456C מצטיין ביישומי טלקומוניקציה ורשתות בגלל יכולתו להתמודד עם העברת נתונים במהירות גבוהה ומשימות עיבוד אותות מורכבות.יכולות הקלט/פלט של ספירת השערים הגבוהה ויכולות הקלט/פלט החזקות שלה מאפשרות לו לתמוך בפונקציות כמו עיבוד מנות, אפנון אות/הדמולציה ופרוטוקולי תיקון שגיאות.

עיבוד אותות דיגיטלי (DSP)

אידיאלי ליישומי DSP, FPGA זה יכול לבצע חישובים מתמטיים מהיר ומורכב הנדרש בטכנולוגיות עיבוד שמע ווידאו.בין אם זה מיועד למערכות מולטימדיה, זיהוי קולי או שירותי סטרימינג, יכולות העיבוד החזקות של XCV200-6FG456C ויכולות העיבוד החזקות של זיכרון המוטמע תומך בעיבוד אותות יעיל ואיכותי.

מערכות בקרה תעשייתיות

באוטומציה התעשייתית, XCV200-6FG456C מספק את הביצועים הדרושים לניהול מערכות בקרה ורשתות אוטומציה.היכולת שלה לבצע משימות בקרה מרובות בו זמנית תוך הבטחת זמני התגובה הופכת אותה מתאימה ליישומים בבקרת תהליכים, רובוטיקה וראיית מכונה.

מכשירים רפואיים

הדיוק והמהירות של ה- FPGA נהדרים בציוד הדמיה רפואית ואבחון, שם היא מסייעת בעיבוד אלגוריתמים מורכבים ליישומי הדמיה כמו MRI, אולטרסאונד וסריקות CT.היכולות של XCV200-6FG456C מבטיחות שהוא יכול להתמודד עם תפוקת נתונים גבוהה ועיבוד מורכב הנדרש בטכנולוגיה רפואית מודרנית.

XCV200-6FG456C חלקים דומים

• • XCV2000E-6BG560C

• • XCV200-6FG256C

• • XCV200-5FG256C

XCV200-6FG456C שלבי תכנות

שלבי תכנות עבור XCV200-6FG456C:

1. כניסה לעיצוב

השלב הראשוני של תכנות FPGA כרוך בהגדרת ההיגיון הדיגיטלי והפונקציונליות של המערכת שלך.ניתן לעשות זאת באמצעות שפות תיאור חומרה (HDLs) כגון VHDL או Verilog, שם אתה כותב קוד שמציין כיצד ה- FPGA מעבד נתונים ואינטראקציה עם חומרה אחרת.ניתן להשתמש בכלי כניסה סכמטיים זמינים בתוכנת עיצוב FPGA כמו Xilinx ISE או Vivado.שיטה זו כוללת יצירת ייצוג חזותי של ההיגיון על ידי גרירת רכיבים וירידה, אשר חלקם מוצאים אינטואיטיביים יותר מכתיבת קוד.

2. סינתזה

לאחר סיום העיצוב, השלב הבא הוא סינתזה, כאשר כלי כמו XST של Xilinx (טכנולוגיית סינתזה של Xilinx) הופך את קוד ה- HDL או העיצוב הסכמטי שלך לרשימת רשת.נטליסט זה מתאר את המעגל במונחים של רכיבים דיגיטליים גנריים, כמו שערי לוגיקה ורישומים.תהליך הסינתזה כרוך גם במיטוב העיצוב כדי לעמוד בדרישות הביצועים ולמזער את השימוש במשאבים להפעלת FPGA יעילה.

3. יישום

תהליך היישום מתחיל בתרגום, תוך שילוב העיצוב שלך עם קבצי אילוץ המפרטים פרמטרים כמו תדרי שעון ומשימות סיכות.בעקבות התרגום, שלב המיפוי מקצה את אלמנטים של ה- NetList שלך למשאבים פיזיים ספציפיים ב- FPGA, כמו טבלאות בדיקה (LUTS) וכפכפים.שלב המיקום והניתוב קובע לאחר מכן את המיקומים הפיזיים של כל רכיב בארכיטקטורת ה- FPGA ומבסס את הקשרים ביניהם באמצעות משאבים חיבוריים לתכנות.שלב זה נהדר להשגת מדדי הביצועים הרצויים, כולל תדרי שעון.

4. דור זרם בים

לאחר מיקום וניתוב מוצלח, הכלי מייצר זרם Bitstream, קובץ תצורה בינארי המכיל את כל פרטי התכנות עבור ה- FPGA.לרוב מומלץ לדמות את העיצוב הסופי לאחר מיקום כדי להבטיח שזרם ה- Bitstream יתנהג כצפוי בתנאים.שלב אימות זה עוזר להימנע מבעיות פוטנציאליות במהלך הפעולה בפועל.

5. תצורה

השלב האחרון כולל העמסת הזרם Bitstream ל- FPGA בשיטות תצורה שונות.מצב העבדים-שריר, אפשרות פשוטה וחסכונית, מגדיר את התצורה של ה- FPGA באמצעות התקן אב חיצוני ששולח נתונים באופן סדרתי.במצב סריאלי, ה- FPGA קורא באופן אוטונומי את הזרם של Bitstream מנשף סדרתי מצורף.עבור תצורות במהירות גבוהה, מצב SelectMap מאפשר למעבד חיצוני לטעון נתונים ל- FPGA במהירות.בנוסף, מצב JTAG משמש לא רק לתכנות אלא גם לבדיקה וניפוי באגים, תוך שימוש בממשק סטנדרטי לתכנות במערכת ובדיקת סריקת גבול.

יתרונות XCV200-6FG456C

ביצועים

סדרת ה- Xilinx Virtex, שאליה שייכת ה- XCV200-6FG456C, מותאמת לביצועים במהירות גבוהה, ומציעה שיעורי שעון מערכת של עד 200 מגהרץ.זה הופך אותו למתאים היטב ליישומים הדורשים עיבוד נתונים מהיר, ומבטיח טיפול יעיל באלגוריתמים מורכבים ופעולות במהירות גבוהה כמו טלקומוניקציה, עיבוד ומולטימדיה.

תמיכה בתקני קלט/פלט

FPGA זה תומך במגוון רחב של תקני קלט/פלט, כולל LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT ו- AGP.תמיכה בתקני קלט/פלט נרחבים כאלה מאפשרת ל- XCV200-6FG456C להשתלב בצורה חלקה עם רכיבי מערכת שונים, ולשפר את התועלת שלה במערכות אקולוגיות דיגיטליות מגוונות.גמישות זו מאפשרת להתאים את ה- FPGA לתנאי ממשק שונים ללא שינויים במערכת.

ניהול שעון

ה- XCV200-6FG456C משלב לולאות מרובות נעילות עיכוב (DLLs) להפצת שעון וניהול במערכת.DLLs אלה מסייעים בשיפור תזמון המערכת ואמינות המערכת על ידי מתן אותות שעון מדויקים הנחוצים לפעולות סינכרוניות.תכונה זו חשובה בהפחתת שגיאות מערכת ושיפור הביצועים הכוללים, במיוחד בעיצובים מורכבים הדורשים תזמון וסנכרון מדויקים.

עיצוב גמישות

עם 1,176 חסימות לוגיקה הניתנות להגדרה ו -5,292 תאי לוגיקה, XCV200-6FG456C מציע משאבי לוגיקה משמעותיים עם יכולת ליישם מגוון פונקציונליות מגוון.החל מהיגיון דבק פשוט למערכות דיגיטליות מורכבות, FPGA זה תומך בדרישות עיצוב מורכבות, מה שהופך אותו לאידיאלי ליישומים במחשוב מותאם אישית, עיבוד אותות דיגיטלי ואבות -טיפוס.

אבות -טיפוס מהיר

FPGAs כמו XCV200-6FG456C ידועים ביכולתם לתמוך באב-טיפוס מהיר.מכשיר זה מאפשר איטרציות עיצוביות מהירות וניתן להגדיר אותו מחדש בשדה, וזה יתרון למחזורי פיתוח מכיוון שהוא מקטין זמן לשוק.זה גם מסתגל ביעילות לשינוי דרישות או עדכונים במפרט הפרויקט, ומבטיח כי המוצרים הסופיים מעודכנים עם הסטנדרטים הטכנולוגיים העדכניים ביותר.

יכולת אינטגרציה

יכולות האינטגרציה של XCV200-6FG456C מאפשרות איחוד רכיבים נפרדים מרובים לשבב יחיד.שילוב זה יכול להוביל להפחתת מורכבות המערכת, צריכת חשמל נמוכה יותר וחיסכון בעלויות.על ידי צמצום מספר הרכיבים הנפרדים הדרושים, FPGA זה מפשט תהליכי תכנון ומשפר את האמינות והקומפקטיות של המערכת הכוללת.

XCV200-6FG456C מידות אריזה

ה- XCV200-6FG456C הוא מערך שער הניתן לתכנות שדה (FPGA) מסדרת Virtex® של AMD, ששוכנה בחבילה של 456 כדור רשת מערך כדורי מערך (FBGA).

• • סוג חבילה: 456-FBGA

• • גודל החבילה: 23 מ"מ x 23 מ"מ

• • מגרש כדור: 1.0 מ"מ

יצרן XCV200-6FG456C

ה- XCV200-6FG456C הוא מערך שער לתכנות שדה (FPGA) שפותח במקור על ידי Xilinx, חברה הידועה במכשירי ההיגיון המתוכננים לביצועים גבוהים.בעקבות הרכישה של Xilinx על ידי AMD, XCV200-6FG456C משויך כעת ל- AMD כיצרנית הנוכחית שלו.עם זאת, מודל ה- FPGA הזה מיושן ואינו יותר בייצור.AMD ממשיכה לתמוך בארכיטקטורות FPGA חדשות יותר עם ביצועים משופרים, יעילות כוח ואריכות חיים מורחבת, מה שהופך את האלטרנטיבות המודרניות לעדיפות לעיצובים חדשים.

מַסְקָנָה

ה- XCV200-6FG456C הוא FPGA רב-תכליתי ומהיר, שימושי ליישומי טכנולוגיה רבים.אמנם זה כבר לא מתבצע, אך זו עדיין בחירה טובה עבור מערכות ישנות הזקוקות לביצועים אמינים.מדריך זה כיסה את העיצוב, שלבי התכנות והשימושים המעשיים שלו, מה שמקל על הבנת אופן הפעולה שלו וכיצד ניתן להשתמש בו.ככל ש- FPGAs חדשים יותר הופכים לזמינים, אתה יכול להשתמש בידע זה כדי לבחור את ה- FPGA המתאים לצרכים שלך ולשפר את העיצובים הדיגיטליים.

גיליון נתונים PDF

XCV200-6FG456C גיליונות נתונים:

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. מהי צריכת החשמל של XCV200-6FG456C?

ה- XCV200-6FG456C פועל במהירות 2.5 וולט, עם טווח מתח של 2.375V עד 2.625V.צריכת החשמל תלויה בניצול ההיגיון ותדירות השעון, אך כ- FPGA ישן יותר, היא עשויה להיות פחות חסכונית בהשוואה למכשירי Xilinx חדשים יותר.יש לקחת בחשבון ניהול כוח ופיזור חום נכון.

2. כיצד ה- XCV200-6FG456C השווה ל- XCV200-6FG256C?

ל- XCV200-6FG456C יש חבילה גדולה יותר (FBGA 456-כדור) בהשוואה ל- XCV200-6FG256C (FBGA של 256 כדור), ומציעים סיכות קלט/פלט יותר (284 לעומת 172) וביצועים פוטנציאליים טובים יותר ליישומים הדורשים ממשק נרחב.אם העיצוב שלך מסתמך על יכולות קלט/פלט נוספות, XCV200-6FG456C הוא הבחירה הטובה יותר.

3. האם אוכל לתכנת מחדש את ה- XCV200-6FG456C מספר פעמים?

כן, XCV200-6FG456C הוא FPGA מבוסס SRAM, כלומר ניתן לתכנת מחדש מספר בלתי מוגבל של פעמים כל עוד מסופק כוח.עם זאת, תזדקק לזיכרון חיצוני שאינו נדיף (EEPROM או Flash) כדי לשמור על הזרם Bitstream לאחר מחזור כוח.

האם ה- XCV200-6FG456C תומך בתקשורת סדרתית במהירות גבוהה?

ה- XCV200-6FG456C תומך בתקני קלט/פלט מרובים כמו LVTTL, LVCMOS, PCI, GTL, HSTL ו- SSTL, אך אין לו SERDEs במהירות גבוהה (Serializer/Deserializer) או משדרים כמו FPGAs מודרניים.ליישומים הדורשים קישורים טוריים במהירות גבוהה (למשל, PCIE, Gigabit Ethernet או HDMI), שקול דגמי FPGA חדשים יותר.

5. כיצד XCV200-6FG456C משווים לדגמי FPGA חדשים יותר?

ה- XCV200-6FG456C שייך לדור מבוגר של FPGAs.בהשוואה ל- FPGAs המודרניים של Virtex, יש לו ספירת שער נמוכה יותר, מהירויות שעון איטיות יותר ויעילות כוח מוגבלת.דגמים חדשים יותר מציעים צפיפות לוגית גבוהה יותר, זיכרון משובץ יותר, בלוקים DSP מתקדמים וצריכת חשמל נמוכה יותר, מה שהופך אותם לטובים יותר עבור יישומים מודרניים.

AD73322AR PINOUT, תכונות ופרטים טכניים שהוסברו

ב- 2025/03/21

EP20K100EFC324-1X FPGA: תכונות, מפרטים, יישומים ומדריך תכנות

ב- 2025/03/20

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/18 147778

-

Pinout USB-C ותכונות

ב- 2000/04/18 112029

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/18 111351

-

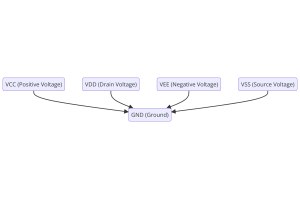

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/18 83780

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79579

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66972

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63107

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63041

-

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54097

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52193