EP20K100EFC324-1X FPGA: תכונות, מפרטים, יישומים ומדריך תכנות

ה- EP20K100EFC324-1X הוא שבב ניתן לתכנות (FPGA) מסדרת Altera Apex-20ke® של אינטל.הוא נועד לטפל במעגלים דיגיטליים מורכבים ותומך בעיבוד נתונים במהירות גבוהה.מדריך זה מסביר את התכונות, המפרט שלו, כיצד לתכנת אותו ואת היתרונות שלו, מה שהופך אותו למשאב מועיל לכולם.קָטָלוֹג

סקירה כללית של EP20K100EFC324-1X

THE EP20K100EFC324-1X הוא חלק מסדרת Altera Apex-20ke® של אינטל, מערך שער הניתן לתכנות שדה (FPGA) המותאם ליישומי לוגיקה ניתנים לתכנות בעלי צפיפות גבוהה המחייבים שילוב מתוחכם של מערכת-על-תכנות (SOPC).מכשיר זה נבדל על ידי שילובו של 4,160 אלמנטים או תאים לוגיים ו 416 חסימות מערך לוגיקה (מעבדות), המאפשרות תצורה משמעותית לעיצובים שונים של מעגלים דיגיטליים.זה גם מתגאה בכמות ניכרת של זיכרון משובץ המאכלס דרישות אחסון נתונים תובעניות בתוך ה- FPGA.עוד יותר שיפור הרבגוניות של היישום שלו, EP20K100EFC324-1X תומך ב -246 סיכות קלט/פלט ומציע ספירת שער משמעותית של כ- 263,000 שערים שווים, הפועלים ביעילות בין 1.71V ל- 1.89V.הוא ארוז במערך רשת כדורים משובח 324 כדור (FBGA), המסייע בשילוב פיזי חזק במכלולים אלקטרוניים.

ה- EP20K100EFC324-1X הוא הבחירה המושלמת כשאתה מוכן לבצע איתנו הזמנות בתפזורת לפרויקטים או לקווי המוצרים שלך.

דגמי CAD של EP20K100EFC324-1X

EP20K100EFC324-1X סמל

טביעת רגל EP20K100EFC324-1X

EP20K100EFC324-1X 3D דגם

תכונות EP20K100EFC324-1X

• • צפיפות היגיון גבוהה: ה- FPGA מצויד ב -4,160 אלמנטים לוגיים (LES) ו- 416 חסימות מערך לוגיקה (מעבדות).צפיפות גבוהה זו של תאי לוגיקה מאפשרת תכנון וביצוע של מעגלים ומערכות דיגיטליות מורכבות בתוך שבב יחיד, מה שהופך אותו לאידיאלי ליישומים הדורשים יכולות עיבוד לוגיקה חזקות.

• • זיכרון משובץ: מציע 53,248 ביטים של זיכרון RAM, FPGA זה מספק משאבי זיכרון משובצים משמעותיים.תכונה זו טובה ליישומים הדורשים אחסון ושליפה מהירה של נתונים, ומאפשר טיפול יעיל במשימות עתירות נתונים.

• • יכולות קלט/פלט נרחבות: עם 246 סיכות קלט/פלט, EP20K100EFC324-1X מבטיח אפשרויות קישוריות וממשק מקיפות.מגוון רחב זה של יכולות קלט/פלט מאפשר לו להתחבר בקלות לשלל מכשירים ומערכות חיצוניות, ולשפר את התועלת שלה במכלולים אלקטרוניים מורכבים.

• • תמיכה רב מתח: המכשיר תומך בטווח מתח ליבה של 1.71V עד 1.89V וכולל ממשק קלט/פלט Multivolt ™.זה מאפשר ל- FPGA להיות תואם לרכיבים אלקטרוניים אחרים הפועלים ברמות לוגיות שונות, כולל 1.8 וולט, 2.5 וולט, 3.3 וולט ו -5.0 וולט, ומספק גמישות רבה בתכנון המערכת.

תרשים חסימת EP20K100EFC324-1X

THE תרשים חסימת EP20K100EFC324-1X מייצג את המבנה הפנימי של מכשיר FPGA (מערך שער הניתן לתכנות), המציג את היחידות הפונקציונליות השונות שלו.התרשים מורכב מבלוקי לוגיקה הקשורים זה לזה, אלמנטים של זיכרון, ניהול שעון ורכיבי קלט/פלט.בבסיס העיצוב הם חסימות מערך לוגיקה (מעבדות), המכילות שולחנות מבט (LUTS) והיגיון מבוסס מונח מוצר.אלמנטים אלה מאפשרים יישום לוגיקה גמיש, מה שהופך את ה- FPGA המתאים להגיון בקרה במהירות גבוהה, מכונות מדינה ופונקציות DSP.THE חיבור FastTrack מספק מסלול תקשורת במהירות גבוהה בין אלמנטים לוגיים, ומבטיח ניתוב אות יעיל בכל המכשיר.THE מעגלי ניהול שעון כולל תכונת נעילת השעון, מבטיחה פעולה אמינה ומסונכרנת על ידי ייצוב והפצת אותות שעון ברחבי ה- FPGA.THE רכיבי קלט/פלט (IOES), ממוקם סביב בד FPGA, משמש כממשקים לתקשורת חיצונית.IOEs אלה תומכים בפרוטוקולים מרובים סטנדרטיים בתעשייה כמו PCI- GTL+- SSTL-3, ו LVDs, מה שמאפשר ל- FPGA להתממשק למגוון מערכות חיצוניות.IOEs אלה מבטיחים תאימות לרמות מתח שונות ותקני איתות, ומשפרים את הרבגוניות של ה- FPGA ביישומים משובצים. חסימות זיכרון משובצות ספק פתרונות אחסון גמישים בתוך ה- FPGA.אלמנטים זיכרון אלה יכולים לתפקד כ- זיכרון הניתן להתייחסות לתוכן (פִּקָה), זיכרון גישה אקראית (אַיִל), זיכרון לקריאה בלבד (רום), ראשית ראשונה (FIFO) מאגרים ומבני זיכרון אחרים.היכולת לשלב זיכרון ישירות בתוך בד FPGA משפרת את יעילות עיבוד הנתונים, ומפחיתה תלות זיכרון חיצוני ואביסת חביון.

מפרטי EP20K100EFC324-1X

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

אינטל |

|

סִדרָה |

Apex-20ke® |

|

אריזה |

מַגָשׁ |

|

סטטוס חלק |

מְיוּשָׁן |

|

מספר המעבדות/CLBs |

416 |

|

מספר אלמנטים/תאים לוגיים |

4160 |

|

סה"כ פיסות זיכרון RAM |

53248 |

|

מספר קלט/פלט |

246 |

|

מספר השערים |

263000 |

|

מתח - אספקה |

1.71V ~ 1.89V |

|

סוג הרכבה |

הר השטח |

|

טמפרטורת הפעלה |

0 ° C ~ 85 ° C (TJ) |

|

חבילה / מקרה |

324-BGA |

|

חבילת מכשירי ספק |

324-FBGA (19x19) |

|

מספר מוצר בסיס |

EP20K100 |

יישומי EP20K100EFC324-1X

רשת ותקשורת

FPGA זה אידיאלי לציוד רשת כמו נתבים ומתגים, שם היא מנהלת ניתוב נתונים, עיבוד אותות וטיפול בפרוטוקול.צפיפות ההיגיון הגבוהה ויכולות הקלט/פלט הנרחבות שלה מאפשרות לו לתמוך בפעולות הנתונים המורכבות והמהירות הנדרשות בתשתית תקשורת מודרנית.

מערכות בקרה תעשייתיות

במגזר התעשייתי, EP20K100EFC324-1X מצטיין במערכות אוטומציה.יכולת התכנות ויכולות העיבוד החזקות שלה מאפשרות שליטה ומעקב מדויקת לשיפור היעילות התפעולית והאמינות בתהליכי הייצור.

אלקטרוניקה לרכב

ה- FPGA משמש כרכיב ביישומי רכב, במיוחד במערכות סיוע לנהגים מתקדמים (ADAS) ובמערכות אינפוטינציה ברכב.הוא מספק את כוח העיבוד והסתגלות הדרושים לטיפול בנתונים ולתמוך בפונקציונליות המתוחכמת הנדרשת ברכבים מודרניים.

אלקטרוניקה צרכנית

בשל הגמישות והביצועים הגבוהים שלו, EP20K100EFC324-1X נמצא גם באלקטרוניקה צרכנית כמו טלוויזיות בהבחנה גבוהה וקונסולות משחק.הוא תומך בפונקציות מורכבות ואיידס בקיצור מחזורי פיתוח מוצרים, ועומד בביקוש המהיר של שוק האלקטרוניקה הצרכנית.

מכשירים רפואיים

בתחום הרפואי, FPGA זה תורם לפונקציונליות של ציוד הדמיה רפואית וכלי אבחון.היכולת שלה לעבד נתונים במהירות גבוהה מבטיחה כי מכשירים אלה יוכלו לספק תוצאות אבחון מדויקות ומתוזמנות לטיפול רפואי יעיל והדמיה.

EP20K100EFC324-1X חלקים דומים

• • EP20K100EFC144-3

• • EP20K100EFC144-2

• • EP20K100EFC324-2

EP20K100EFC324-1X שלבי תכנות

כדי לתכנת ביעילות את EP20K100EFC324-1X, חבר בסדרת ה- FPGA של Apex-20Ke® של Altera, חשוב לעקוב אחר רצף של צעדים מובנים.תהליך זה מבטיח כי העיצוב שלך יתורגם ביעילות לפורמט שה- FPGA יכול לבצע.להלן, אני מתווה גישה מפורטת לתכנות מודל FPGA זה, תוך שילוב שלבים ושינויים ספציפיים למכשיר זה.

1. כניסה לעיצוב

התחל ביצירת עיצוב ההיגיון הדיגיטלי שלך.השתמש בשפות תיאור חומרה (HDLs) כגון VHDL או Verilog, המאפשרים לך לתאר את הפונקציונליות וההיגיון של החומרה של המערכת שלך.כלים כמו הקווארטוס II של Altera מציעים סביבה מקיפה לכתיבה, בדיקה והרכבת קוד HDL שלך.ודא שהעיצוב שלך הוא מודולרי, מה שמקל על ניפוי באגים וקנה מידה.

2. סינתזה

לאחר השלמת כניסת העיצוב שלך, השלב הבא הוא סינתזה, שם קוד HDL מתורגם לרשימת Net.NetList זה מייצג את הרשימה המחוברת בין השערים, הכפכפים ואלמנטים חומרה אחרים המרכיבים את העיצוב שלך.במהלך הסינתזה, הקוד מותאם לארכיטקטורה הספציפית של EP20K100EFC324-1X, ומבטיח כי העיצוב ישתמש ביעילות במשאבי ה- FPGA.ניתן להשתמש בכלים כמו Synplify Pro או כלי הסינתזה בתוך Quartus II למטרה זו.חשוב להתמקד במיטוב העיצוב שלך כדי לעמוד באילוצי תזמון ומשאבים.

3. יישום

בעקבות הסינתזה, יישום מתרחש.שלב זה כרוך במיפוי ה- NetList לחומרת ה- FPGA בפועל.זה כולל מיקום אלמנטים ההיגיוניים בתוך ה- FPGA וניתוב החיבורים ביניהם.תוכנת קווארטוס II מאפשרת תהליך זה באמצעות כלי היישום שלה, המנהלים את המיקום והניתוב כדי לעמוד במהירויות השעון והמדדים הרצויים.במהלך היישום, ייתכן שתצטרך לחזור על העיצוב שלך על סמך המשוב מכלי ניתוח תזמון כדי להבטיח כי כל דרישות הביצועים מתקיימות.

4. דור זרם בים

לאחר יישום מוצלח, השלב הבא הוא מייצר את הזרם Bit.זהו הקובץ הבינארי שייטען על ה- FPGA.הזרם Bitstream מכיל נתונים מוגדרים עבור כל אלמנט הניתן לתכנות ב- FPGA, ומגדיר את המכשיר לביצוע הפונקציות לפי העיצוב שלך.תוכנת Quartus II יכולה לייצר את הזרם הזה, אשר אז מוכנה להורדה ל- FPGA.

5. תכנות ה- FPGA

השלב האחרון הוא לתכנת את ה- FPGA עם הזרם שנוצר.ניתן לעשות זאת באמצעות מתכנת חומרה התואם ל- EP20K100EFC324-1X, כמו ה- USB Blaster.חבר את המתכנת ללוח הפיתוח שלך בו מותקן ה- FPGA והשתמש בכלי המתכנת Quartus II כדי להעביר את הזרם Bitstream ל- FPGA.שלב זה יטען את העיצוב שלך על ה- FPGA, והוא יתחיל לפעול על פי ההיגיון המוגדר בקוד ה- HDL שלך.

יתרונות EP20K100EFC324-1X

שילוב גבוה

ה- EP20K100EFC324-1X מציע יכולות אינטגרציה גבוהות בגלל מספרם הגדול של אלמנטים לוגיים וזיכרון משובץ.שילוב זה מאפשר איחוד פונקציות מרובות במכשיר יחיד.כתוצאה מכך ניתן לפשט מערכות, להפחית את ספירת הרכיבים הכוללת, המרחב הפיזי הנדרש ונקודות כישלון פוטנציאליות בעיצובים אלקטרוניים.

יישום לוגיקה גמיש

הארכיטקטורה של ה- EP20K100EFC324-1X תומכת הן בטבלת בדיקות (LUT) והן בהיגיון מבוסס מונח מוצר.גמישות זו ביישום ההיגיון מאפשרת לייעל את ה- FPGA למגוון רחב של יישומים, החל משערי לוגיקה פשוטים ועד מעגלי שילוב מורכבים.זה מספק יתרון מבחינת צדדיות עיצובית ויכול להכיל קשת רחבה של פונקציות דיגיטליות.

מבנה חיבורי מתקדם

ה- FPGA כולל מבנה בין חיבורי היררכי, כולל חיבורים מקומיים, Megalab ™ ו- FastTrack®.משאבי ניתוב מיוחדים אלה משפרים את יעילות ניתוב האות ומשפרים את הביצועים הכוללים של המכשיר.מבנה חיבורי מתקדם זה טוב לעיצובים הדורשים העברת נתונים במהירות גבוהה וחביון נמוך, מה שהופך את ה- FPGA לאידיאלי למחשוב ותקשורת בעלת ביצועים גבוהים.

ניהול שעון

EP20K100EFC324-1X משלב טכנולוגיית שעון ושעון, המסייעת בניהול שעון יעיל.תכונות אלה מסייעות בשמירה על שלמות האות השעון ברחבי ה- FPGA, הפחתת ריצוד ושיפור אמינות האות.יש צורך בניהול שעון יעיל למעגלים דיגיטליים סינכרוניים, ומבטיח פעולה יציבה וצפויה בתנאים סביבתיים שונים.

עיצוב גמישות

האופי הניתן לתכנות של EP20K100EFC324-1X מאפשר להתאים חומרה לצרכים ספציפיים ולהגדיר מחדש את ה- FPGA ליישומים או עדכונים שונים.גמישות זו פירושה שניתן להשתמש ב- FPGA יחיד על פני מספר פרויקטים, המועילים בנוף טכנולוגי דינמי בו הדרישות יכולות להשתנות במהירות.

אבות -טיפוס מהיר

FPGAs כמו EP20K100EFC324-1X מאפשרים אבות-טיפוס מהיר של מעגלים דיגיטליים.אתה יכול לפתח ולחזור עיצובים במהירות ללא זמני ההובלה הארוכים הקשורים לפיתוח ASIC בהתאמה אישית.יכולת זו לדגמן ולבדוק במהירות עיצובים חדשים מאיצה את תהליך הפיתוח, מה שמוביל לחדשנות מהירה יותר וקיצר זמן לשוק.

יעילות עלות

שילוב פונקציות מרובות בתוך FPGA יחיד מצמצם את הצורך ברכיבים נפרדים נוספים, שיכולים להוביל לחיסכון בעלויות הן ברכש והן בהרכבה.אינטגרציה זו מפשטת גם את תהליך הייצור ויכול להפחית את מורכבות המערכת הכוללת, מה שמוביל לתחזוקה נמוכה יותר עלויות עלויות על מחזור החיים של המוצר.

תמיכה לטווח הארוך

ההיבט הניתן להגדרה מחדש של ה- EP20K100EFC324-1X מבטיח שניתן לעדכן חומרה כדי לתקן באגים, לשפר את הביצועים או להוסיף תכונות חדשות מבלי לדרוש שינויים בחומרה פיזית.תמיכה ויכולת הסתגלות ארוכת טווח זו מגנים על השקעות ומאפשרים למכשירים להישאר רלוונטיים ככל שמתעוררים סטנדרטים וטכנולוגיות חדשות.

EP20K100EFC324-1X מידות אריזה

EP20K100EFC324-1X הוא FPGA מסדרת Apex-20Ke® של Altera, ששוכנה ב- A 324-כדור מערך רשת כדורים משובח (FBGA) חֲבִילָה.מידות האריזה שלה הן כדלקמן:

• • פְּסִיעָה: 1 מ"מ

• • אורך × רוחב: 19 מ"מ × 19 מ"מ

• • אֵזוֹר: 361 מ"מ²

יצרן EP20K100EFC324-1X

EP20K100EFC324-1X הוא דגם מסדרת Apex-20KE® של מערכי שער הניתנים לתכנות שדה (FPGAs) שפותחו במקור על ידי Altera.לאחר הרכישה של אינטל של אלטרה בשנת 2015, FPGA ומוצרי אלטרה אחרים הפכו לחלק מתיק הפתרונות התכנותיים הנרחב של אינטל.כתוצאה מכך, אינטל ממשיך לתמוך בקווי המוצרים של Altera תוך שילובם עם הצעות טכנולוגיה מתקדמות משלהם.אף על פי ש- EP20K100EFC324-1X סווג כמיושן ואינו עוד בייצור, מורשתו נשמרת תחת אינטל, מה שממליץ על דגמי FPGA חדשים יותר ליישומים נוכחיים כדי להבטיח תמיכה וזמינות לטווח הארוך.

מַסְקָנָה

EP20K100EFC324-1X הוא FPGA חזק וגמיש המאפשר ליצור ולבדוק מעגלים דיגיטליים מותאמים אישית.הוא מציע ביצועים גבוהים, זיכרון מובנה ותמיכה רב מתח, מה שהופך אותו לשימושי בענפים רבים.מדריך זה העביר אותך דרך התכונות העיקריות, העיצוב והצעדים לתכנת FPGA זו בצורה פשוטה, כך שתוכל להבין אותו ולהשתמש בו בקלות.

גיליון נתונים PDF

EP20K100EFC324-1X גיליונות נתונים:

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. כיצד EP20K100EFC324-1X משווים לדגמי FPGA חדשים יותר?

ה- EP20K100EFC324-1X נותר FPGA חזק למערכות מדור קודם ויישומים תעשייתיים הדורשים צפיפות לוגית גבוהה ויכולות קלט/פלט גמישות.עם זאת, בהשוואה לסדרת FPGAs מודרניים כמו ציקלון, Arria או Stratix של אינטל, היא חסרה יעילות כוח מתקדמת, משדרים במהירות גבוהה ותאוצה מונעת AI.אם אתה מעצב מערכת חדשה, אנו יכולים להציע דגמים שווים או משודרגים.

2. האם EP20K100EFC324-1X תומך בממשקי זיכרון חיצוניים כמו DDR או SRAM?

כן, EP20K100EFC324-1X תומך בממשקי זיכרון חיצוניים, כולל SRAM ו- SDRAM.עם זאת, הוא אינו תומך באופן טבעי ב- DDR2/DDR3.אם יש צורך בממשקי זיכרון במהירות גבוהה, יתכן שיהיה צורך בהיגיון חיצוני נוסף או FPGA חדש יותר.

3. האם אוכל להגדיר מחדש את ה- EP20K100EFC324-1X מספר פעמים?

כן, כמו כל ה- FPGA, המכשיר הזה ניתן לתכנת מחדש לחלוטין.עם זאת, אם משתמשים בתצורה נדיפה, תזדקק לזיכרון חיצוני (כגון PROM סדרתי) כדי לשמור על העיצוב לאחר רכיבה על אופניים.

האם אני יכול לתכנת את EP20K100EFC324-1X באמצעות תוכנת אינטל קווארטוס?

כן, אתה יכול לתכנת את EP20K100EFC324-1X באמצעות Intel Quartus II (גרסאות מדור קודם), מכיוון ש- FPGA זה שייך למשפחת Apex-20Ke®.וודא כי גרסת ה- Quartus II שלך תומכת במכשיר זה, שכן המהדורות החדשות של קווארטוס פריים אינן תומכות ב- FPGAs מדור קודם.

5. אילו דרישות אספקת חשמל עלי לקחת בחשבון בעת שימוש ב- EP20K100EFC324-1X?

EP20K100EFC324-1X פועל עם טווח מתח ליבה של 1.71V עד 1.89 וולט.הוא כולל גם טכנולוגיית קלט/פלט של Multivolt ™, התומכת ברמת ההיגיון של 1.8 וולט, 2.5V, 3.3V ו- 5.0V.ודא שאספקת החשמל שלך עומדת בדרישות המתח הללו לביצועים יציבים.

XCV200-6FG456C FPGA: תכונות, מפרטים, תכנות ויישומים

ב- 2025/03/20

מדוע רכיבים 0603 פופולריים באלקטרוניקה מודרנית

ב- 2025/03/20

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/18 147770

-

Pinout USB-C ותכונות

ב- 2000/04/18 112006

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/18 111351

-

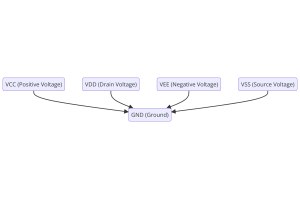

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/18 83768

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79562

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66959

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63098

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63040

-

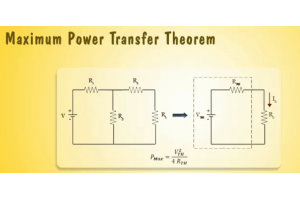

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54095

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52182