XC4VLX100-10FFG1148C FPGA: תכונות, מפרטים, יישומים ומדריך תכנות

אם אתה עובד עם עיצובים דיגיטליים מורכבים, XC4VLX100-10FFG1148C מעניק לך את הכוח והגמישות הדרושה לך.FPGA זה אורז קיבולת לוגיקה גבוהה, זיכרון מובנה ומספר גדול של סיכות קלט/פלט, מה שהופך אותו לאידיאלי ליישומים תובעניים.במדריך זה תלמד על התכונות, הביצועים שלו, פרמטרי התזמון, היישומים, שלבי התכנות, היתרונות והחסרונות, פרטי האריזה ורקע היצרן.קָטָלוֹג

מהו XC4VLX100-10FFG1148C?

THE XC4VLX100-10FFG1148C הוא FPGA בעל ביצועים גבוהים מ- Xilinx (כיום AMD), השייך למשפחת Virtex-4 LX, שנבנתה בתהליך נחושת של 90 ננומטר.מכשיר זה מיועד ליישומי לוגיקה דיגיטלית מורכבים והוא חלק מסדרת LX המדגישה משאבי לוגיקה וזיכרון ללא משדרים סדרתיים במהירות גבוהה.היא מזוהה על ידי חבילת ה- FCBGA של 1148 כדור FCBGA ודירוג הטמפרטורה המסחרית, היא מייצגת את אחת האפשרויות בעלות קיבולת גבוהה יותר במערך LX.

מחפש XC4VLX100-10FFG1148C?צרו קשר כדי לבדוק את המלאי הנוכחי, זמן ההובלה והתמחור.

XC4VLX100-10FFG1148C תכונות

• • יכולת היגיון גבוהה

ה- XC4VLX100-10FFG1148C מספק 110,592 תאי לוגיקה, ומאפשר יישום של עיצובים דיגיטליים מורכבים במכשיר יחיד.קיבולת היגיון גדולה זו הופכת אותה למתאימה לפונקציות עיבוד ובקרה בצפיפות גבוהה.

• • זיכרון משובץ ומופץ

זה משתלב כ -4.22 מגה -אביט של זיכרון כולל, המשלב RAM בלוק ואיל מופץ.ארכיטקטורת זיכרון זו תומכת באחסון נתונים יעיל, חיץ ועיבוד על השבב ללא צורך בזיכרון חיצוני נרחב.

• • משאבי קלט/פלט נרחבים

המכשיר מציע 768 סיכות קלט/פלט של משתמש, מה שמאפשר גמישות להתממשק עם רכיבים ומערכות חיצוניות שונות.I/OS אלה תומכים במגוון רחב של סטנדרטים דרך תכונת Selectio ™, ומשפרים את הקישוריות ברמת הלוח.

• • גרעין בעל ביצועים גבוהים

ה- FPGA פועל במתח ליבה של 1.2 וולט, ותומך בפנים פנימיות עד 500 מגה הרץ, ומספק ביצועי לוגיקה מהירים.זה מבטיח פעולה אמינה בדרישת יישומים במהירות גבוהה.

• • טווח טמפרטורות מסחרי

המכשיר מדורג ל -0 מעלות צלזיוס ל- +85 מעלות צלזיוס, ומיועד לסביבות בדרגה מסחרית.היא שומרת על ביצועים יציבים על פני תנאי הפעלה אופייניים למערכות תעשייתיות ומוטמעות.

פרמטרים לתזמון שעון הפניה

התרשים מראה את מדידות עליית השעון ונפילה עבור XC4VLX100-10FFG1148C, ומתמקד ב- TRCLK (זמן עלייה) ו- tFCLK (זמן סתיו) בין רמות המתח של 20% ל- 80% של אות השעון.זה ממחיש כמה מהר מעברי השעון נמוך לגבוה וגבוה לנמוך, וזה נהדר לשמירה על שלמות תזמון ותפעול אמין של ה- FPGA.שליטה מדויקת בקצוות אלה מבטיחה סנכרון מדויק של היגיון פנימי וממשקים חיצוניים.ב- XC4VLX100-10FFG1148C, שמירה על זמני עלייה ונפילה נאותים חשובה לביצועים היציבים במהירות גבוהה ולמזעור עיוות האות.

הגדרת מבחן כללית

התרשים ממחיש את מערך הבדיקה הכללי המשמש למדידת עיכובים בפלט ומאפייני האות של XC4VLX100-10FFG1148C FPGA.נגד התייחסות (RRef) וקבל (גRef) מחוברים לפלט FPGA, עם Vמדידה המייצג את רמת המתח בה נלקחים מדידות תזמון.הגדרה סטנדרטית זו מבטיחה מדידה עקבית ומדויקת של עיכובי מעבר אותות בסביבות בדיקה שונות.עבור XC4VLX100-10FFG1148C, זה חשוב לאימות ביצועי קלט/פלט במהירות גבוהה ולהבטיח שהמכשיר עומד במפרטי התזמון ביישומים אמיתיים.

מפרטים XC4VLX100-10FFG1148C

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

AMD/XILINX |

|

סִדרָה |

Virtex®-4 LX |

|

אריזה |

מַגָשׁ |

|

סטטוס חלק |

פָּעִיל |

|

מספר המעבדות/CLBs |

12288 |

|

מספר אלמנטים/תאים לוגיים |

110592 |

|

סה"כ פיסות זיכרון RAM |

4423680 |

|

מספר קלט/פלט |

768 |

|

מתח - אספקה |

1.14 V ~ 1.26 V |

|

סוג הרכבה |

הר השטח |

|

טמפרטורת הפעלה |

0 ° C ~ 85 ° C (TJ) |

|

חבילה / מקרה |

1148-BBGA, FCBGA |

|

חבילת מכשירי ספק |

1148-FCPBGA (35 × 35) |

|

מספר מוצר בסיס |

XC4VLX100 |

יישומי XC4VLX100-10FFG1148C

1. מערכות עיבוד אותות דיגיטליות (DSP)

ה- XC4VLX100-10FFG1148C מתאים היטב ליישום אלגוריתמי DSP בעלי ביצועים גבוהים בזכות יכולת ההיגיון הגדולה והזיכרון המשובץ שלו.אתה יכול לבנות צינורות עיבוד מותאמים אישית המטפלים בחישובים אינטנסיביים בזמן.זה הופך אותו לאידיאלי ליישומים כמו עיבוד תמונה, מערכות מכ"ם וסינון מתקדם.

2. תאוצה של מערכת משובצת

בעזרת הארכיטקטורה הגמישה שלו, המכשיר נמצא בשימוש נרחב כדי להאיץ פונקציות מערכת משובצות כמו טיפול בפרוטוקול, ניהול אוטובוס והעומס חומרה.על ידי העברת משימות מתוכנה לבד FPGA, היא משפרת את היענות המערכת.זה מאפשר לייעל את הביצועים תוך שמירה על גמישות עיצובית.

3. ציוד תקשורת ורשתות

יכולות הספירת והעיבוד הגבוהות של ה- FPGA והעיבוד הופכות אותו למתאים לתשתיות תקשורת, כולל מתגים, נתבים וגשרים ממשקיים.זה יכול לנהל פרוטוקולי רשת מורכבים וזרמי נתוני רוחב פס גבוה עם חביון נמוך.זה הופך אותו לבחירה אמינה עבור מערכות רשת עמוד השדרה ומערכות מרכז הנתונים.

4. רכישת ועיבוד נתונים במהירות גבוהה

XC4VLX100-10FFG1148C מצטיין ביישומים הדורשים לכידת ועיבוד נתונים מהירה, כגון מכשור וציוד מדעי.משאבי הזיכרון המשובצים והלוגיים שלו מאפשרים חיץ מהיר ומניפולציה של נתונים מקבילים.זה מבטיח טיפול יעיל בנפחי נתונים גדולים בסביבות.

XC4VLX100-10FFG1148C חלקים דומים

|

מִפרָט |

XC4VLX100-10FFG1148C |

XC4VLX100-10FFG1148I |

XC4VLX100-11FFG1148C |

Xc4vlx100-10ff1148c |

XC4VLX100-10FFG1513C |

XC4VLX100-12FFG1148C |

|

יַצרָן |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

|

מִשׁפָּחָה |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

|

יכולת היגיון |

110,592 תאים |

110,592 תאים |

110,592 תאים |

110,592 תאים |

110,592 תאים |

110,592 תאים |

|

סוג חבילה |

FCBGA |

FCBGA |

FCBGA |

FCBGA |

FCBGA |

FCBGA |

|

ספירת כדור |

1148 |

1148 |

1148 |

1148 |

1513 |

1148 |

|

ציון מהירות |

–10 |

–10 |

–11 |

–10 |

–10 |

–12 |

|

ציון טמפרטורה |

מסחרי (ג) |

תעשייתי (i) |

מסחרי (ג) |

מסחרי (ג) |

מסחרי (ג) |

מסחרי (ג) |

|

מתח ליבה |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

|

טווח טמפרטורות הפעלה |

0 ° C עד +85 מעלות צלזיוס |

–40 מעלות צלזיוס ל- +100 מעלות צלזיוס |

0 ° C עד +85 מעלות צלזיוס |

0 ° C עד +85 מעלות צלזיוס |

0 ° C עד +85 מעלות צלזיוס |

0 ° C עד +85 מעלות צלזיוס |

|

הֶבדֵל |

חלק בסיס, PKG רגיל |

תמיכה זמנית תעשייתית |

ציון מהירות גבוהה יותר |

חסר ייעוד "G" |

חבילה גדולה יותר, יותר קלט/פלט |

ציון המהירות המהיר ביותר בסדרה |

XC4VLX100-10FFG1148C שלבי תכנות

לפני שתכנת את XC4VLX100-10FFG1148C, עליך להבטיח כי סביבת הפיתוח שלך ותצורת הקבצים שלך יוגדרו כראוי.המכשיר תומך במצבי תצורה מרובים, ולכן בחירתו המוקדמת הנכונה מבטיחה תהליך תכנות חלק ומוצלח.

1. הפעל את המכשיר

התחל על ידי יישום כוח על ה- FPGA באמצעות מסילות המתח הנדרשות (VCCINT, VCCAUX ו- VCC_CONFIG).עליכם לוודא כי המתחים הללו מגיעים לרמות יציבות לפני תחילת תצורה כלשהי.רצף כוח נכון טוב כדי למנוע שגיאות אתחול.

2. בחר מצב תצורה

בשלב הבא, ה- FPGA מדגמת את סיכות המצב שלה בקצה העולה של init_b כדי לקבוע באיזו שיטת תצורה להשתמש.אתה יכול לבחור בין JTAG, סדרתי עבדים, סדרת מאסטר או SelectMap, תלוי בהגדרה שלך.וודא שסיכות המצב מוגדרות כראוי, מכיוון שהם שולטים כיצד יועבר זרם ה- Bitstream.

3. אתחול המכשיר

ה- FPGA מנקה את זיכרון התצורה שלו ומתכונן לטעינה של זרם ביטים במהלך האתחול.בשלב זה, אותות כמו init_b, GWE ו- GTS משמשים להגדרת המכשיר למצב ידוע.עליכם להבטיח כי כל אותות האתחול יתנהגו כצפוי לפני שתמשיכו.

4. טען את הזרם

בעזרת הממשק שבחרת, כעת תזרם את הזרם התצורה ל- FPGA.לדוגמה, אם משתמשים ב- JTAG, הזרם Bitstream מועבר באופן סדרתי לזיכרון התצורה של המכשיר.יש צורך בהעברה מדויקת ומלאה של זרם Bitstream לתכנות מוצלחת.

5. התחל את תהליך התצורה

ברגע שזרם ה- Bitstream נטען במלואו, ה- FPGA יוצא ממצב Shift ומתחיל ברצף ההפעלה.פקודה JSTART או תהליך שווה ערך מפעילים את המכשיר לסיום התצורה.עליכם לאפשר ל- FPGA להשלים שלב זה ללא הפרעות.

6. מלא תצורה והזן את מצב המשתמש

ה- FPGA בודק אוטומטית את שלמות הזרם של Bitstream באמצעות CRC, ואם תקף, טוען את האות שנעשה.ברגע שזה קורה, היגיון המשתמש הופך לפעיל והמכשיר פועל על פי העיצוב שלך.בשלב זה, תהליך התצורה הושלם, וה- FPGA פונקציונלי לחלוטין.

7. אימות אופציונלי

לבסוף, אתה יכול לבצע שלב קריאה או אימות כדי להבטיח שהתצורה הייתה מוצלחת.ניתן לעשות זאת באמצעות JTAG או SelectMap, תלוי במצב בו השתמשת.למרות אופציונלי, מומלץ מאוד למערכות לאישור תכנות נאותות.

XC4VLX100-10FFG1148C יתרונות וחסרונות

יתרונות

• צריכת החשמל הכוללת הורידה בהשוואה ל- FPGAs רבים של 90 ננומטר.

• נתמך על ידי מערכת אקולוגית בוגרת ויציבה.

• יחס ביצועים לעלות חזקה לדורו.

• ארכיטקטורת ASMBL מודולרית משפרת את יעילות העיצוב.

• פלטפורמה אמינה ומוכחת לעיצובים מבוססים.

חסרונות

• מבוסס על טכנולוגיית מדור קודם עם תמיכה עתידית מוגבלת.

• חסר משדרים סדרתיים במהירות גבוהה שנמצאים במשפחות חדשות יותר.

• מדרגיות וגמישות נמוכה יותר בהשוואה ל- FPGAs מודרניים.

• אתגרי המקור הפוטנציאליים עקב גיל המוצר.

• דורש כוח זהיר וניהול תרמי עם ניצול גבוה.

XC4VLX100-10FFG1148C מידות אריזה

|

פָּרָמֶטֶר |

מידות |

|

סוג חבילה |

FFG1148 (BGA-Flip-Chip, BGA משובח) |

|

מגרש כדור |

1.00 מ"מ |

|

גודל גוף החבילה (L × W) |

35.00 מ"מ × 35.00 מ"מ |

|

גודל גוף החבילה (L × W, אינץ ') |

1.378 ב × 1.378 ב |

|

גובה החבילה הכולל (א) |

3.40 מ"מ (טיפוסי) |

|

גובה החבילה הכולל (A, אינץ ') |

0.134 אינץ '(טיפוסי) |

|

סובלנות בגודל הגוף |

± 0.20 מ"מ |

|

מערך כדור |

34 × 34 (1.00 מ"מ רשת המגרש) |

|

ספירת כדור |

1,148 כדורים |

|

קוטר הכדור (נומינלי) |

0.60 מ"מ |

|

עובי מצע (ב) |

~ 1.00 מ"מ |

|

גובה עומד (A1) |

0.40 מ"מ (נומינלי) |

|

גודל שבלול חום / כובע מתכת |

~ 32 מ"מ ריבוע (שטח מתכת עליון טיפוסי) |

|

סוג הרכבה |

הר השטח |

XC4VLX100-10FFG1148C יצרן

ה- XC4VLX100-10FFG1148C מיוצר על ידי Xilinx, חלוץ בתחום מכשירי לוגיקה הניתנים לתכנות.בשנת 2022, קסילינקס הפך לחלק מ AMD (מכשירי מיקרו מתקדמים), חיזוק עוד יותר את מעמדה בטכנולוגיות מחשוב וטכנולוגיות אדפטיביות בעלות ביצועים גבוהים.מיזוג זה משלב את מומחיות ה- FPGA של Xilinx עם מנהיגות העיבוד של AMD, ומבטיח תמיכה וחדשנות חזקה לטווח הארוך למוצרים כמו XC4VLX100-10FFG1148C.

מַסְקָנָה

XC4VLX100-10FFG1148C בולט בספירת תאי ההיגיון הגדולים שלו, ארכיטקטורת הזיכרון הגמישה, יכולות הקלט/פלט רחבות וביצועים מוצקים בייצורו.הוא תומך בכיבוי במהירות גבוהה ושלמות איתות אמינה, מה שהופך אותו למתאים היטב ליישומים תובעניים במערכות DSP, רשת ומערכות משובצות.אמנם היא מציעה יציבות מוכחת ומערכת אקולוגית בוגרת, אך היא משקפת טכנולוגיית מדור קודם עם מגבלות מדרגיות ומיקור מסוימות, מה שהופך את השיקול הקפדני לחשוב לעיצובים מודרניים.

גיליון נתונים PDF

XC4VLX100-10FFG1148C גיליונות נתונים:

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. כיצד משווה XC4VLX100-10FFG1148C למשפחות FPGA חדשות יותר?

משפחות חדשות יותר כמו Virtex-6, 7-Series או Ultrascale מציעות מהירויות גבוהות יותר, כוח נמוך יותר ומשדרים סדרתיים משולבים.עם זאת, XC4VLX100-10FFG1148C מספק ערך מצוין למערכות מדור קודם שאינן דורשות את התכונות העדכניות ביותר.

2. אילו כלי פיתוח תואמים ל- XC4VLX100-10FFG1148C?

אתה יכול להשתמש ב- Xilinx ISE Design Suite לסינתזה, יישום וייצור Bitstream.מכיוון שמדובר במשפחת FPGA ישנה יותר, כלים חדשים יותר כמו Vivado אינם תומכים בה, אז וודאו שיש לכם סביבת פיתוח תואמת.

3. האם אתה יכול להשתמש בסביבות רגישות ל- XC4VLX100-10FFG1148C בסביבות רגישות לטמפרטורה?

מכשיר זה מדורג לטווח טמפרטורות מסחרי של 0 מעלות צלזיוס ל- +85 מעלות צלזיוס, מה שהופך אותו מתאים לרוב התנאים התעשייתיים והמשובצים הסטנדרטיים.לסביבות קשות יותר, יתכן שתידרש גרסה עם טווח טמפרטורות מורחב.

4. האם ניתן להשתמש ב- XC4VLX100-10FFG1148C ליישומי עיבוד נתונים במהירות גבוהה?

כֵּן.עם שעון פנימי של 500 מגה הרץ ויכולת לוגיקה גדולה, הוא מטפל ביעילות בעיבוד אותות במהירות גבוהה.עם זאת, תצטרך לתכנן אילוצי תזמון מתאימים ופריסות ברמת הלוח כדי למקסם את הביצועים.

5. האם XC4VLX100-10FFG1148C דורש קירור מיוחד או ניהול תרמי?

בניצול גבוה, FPGA זה יכול לייצר חום משמעותי.עליכם לספק זרימת אוויר נאותה, קשיחות חימום או תכנון תרמי ברמת הלוח כדי לשמור על ביצועים ולהימנע ממצב או נזק לטווח הארוך.

BCM5221KPB Ethernet PHY: תכונות, תרשים חסימה, יישומים וגליון נתונים

ב- 2025/10/12

כיצד לבחור נתיכי מכה מהירה ומפוצצים איטיים כדי להגן על מעגלי חשמל

ב- 2025/10/11

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/17 147713

-

Pinout USB-C ותכונות

ב- 2000/04/17 111722

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/17 111322

-

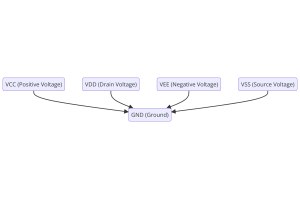

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/17 83606

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79257

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66775

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 62946

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 62820

-

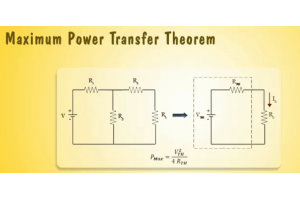

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54028

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 51986