XC2C256-7TQ144C CPLD: PINOUT, תכונות, מדריך לתכנות וגליון נתונים

במדריך זה תקבלו מבט ברור על XC2C256-7TQ144C, CPLD בעל עוצמה נמוכה ממשפחת CoolRunner-II של Xilinx (כיום AMD).תלמד על תצורת ה- PIN שלה, דגמי CAD ותכונות עיקריות כמו קיבולת לוגיקה, אפשרויות קלט/פלט, תמיכה במתח ופונקציות חיסכון בחשמל.אנו נלך גם בארכיטקטורה, עקומת I/V ומפרטים, ואחריהם יישומים, חלקים דומים, שלבי תכנות, יתרונות וחסרונות, פרטי אריזה ומידע על יצרן, כך שתוכלו להבין בדיוק כיצד מכשיר זה מתאים לפרויקטים שלכם.קָטָלוֹג

מהו XC2C256-7TQ144C?

THE XC2C256-7TQ144C הוא CPLD בעל עוצמה נמוכה (מכשיר לוגיקה מורכב לתכנות) ממשפחת CoolRunner-II של Xilinx, כיום חלק מ- AMD.הוא כולל 256 תאי מקרו ומגיע בחבילת TQFP בת 144 פינים, המיועדת להפעלה מהירה ודטרמיניסטית עם צריכת חשמל מינימלית.הוא פועל על ליבת 1.8 וולט, והוא מציע ביצועים אמינים בגורם צורה קומפקטי ומתאים היטב לעיצובים הדורשים יכולת מיידית ויישום לוגיקה יעיל.כחלק מסדרת CoolRunner-II המגוונת, היא נהנית מארכיטקטורה מוכחת ותאימות עיצוב רחבה.

מחפש XC2C256-7TQ144C?צרו קשר כדי לבדוק את המלאי הנוכחי, זמן ההובלה והתמחור.

XC2C256-7TQ144C תרשים פין-אאוט

תרשים ה- XC2C256-7TQ144C PIN-OUT מראה כיצד מסודרים 144 הסיכות לפונקציות קלט/פלט מתוכנתות על כוח, קרקע, jtag ופונקציות קלט/פלט.רוב הסיכות הן קלט/פלט, אשר ניתן להגדיר ככניסות או תפוקות, ומופצות באופן שווה לתמיכה בניתוב גמיש.סיכות VCC, VCCIO1, VCCIO2, VAUX ו- GND ממוקמות סביב החבילה כדי לספק חלוקת כוח יציבה ואפשרויות מתח קלט/פלט מרובות.סיכות JTAG (TDI, TDO, TMS, TCK) מקובצות זו לזו לתכנות ובדיקות קלות במערכת.

דגמי CAD של XC2C256-7TQ1444C

XC2C256-7TQ144C סמל

XC2C256-7TQ144C טביעת רגל

XC2C256-7TQ144C דגם 3D

תכונות XC2C256-7TQ144C

• • סוג מכשירים ומשפחה

ה- XC2C256-7TQ1444C הוא מכשיר לוגיקה מורכב לתכנות (CPLD) השייך למשפחת CoolRunner-II שפותחה על ידי Xilinx (כיום AMD).הוא מיועד לצריכת חשמל נמוכה תוך שמירה על ביצועי לוגיקה מהיר ודטרמיניסטי, מה שהופך אותו לאידיאלי עבור היגיון בקרה ומיישומי ממשק.

• • יכולת היגיון

מכשיר זה מכיל 256 תאי מקרו, שהם משאבי ההיגיון הניתנים לתכנות ב- CPLD.ניתן להגדיר תאי מקרו אלה ליישום פונקציות לוגיות משולבות ורציפות שונות, מה שמאפשר יכולת בינונית לבקרה, לוגיקה של דבק וממשקי אוטובוס.

• • חסימות לוגיקה (חסימות פונקציות)

זה משלב 16 חסימות פונקציות המארגנות ומנהלות קבוצות של תאי מקרו.כל בלוק מספק משאבים מקומיים של חיבורים מקומיים וטווח המוצר, ומאפשר יישום לוגיקה גמיש וניתוב יעיל בתוך המכשיר.

• • סיכות קלט/פלט של משתמש

XC2C256-7TQ144C מציעה עד 118 סיכות קלט/פלט הניתנות להגדרה של המשתמש בחבילת TQFP-144 שלה.ספירת סיכות גבוהה זו מאפשרת למכשיר להתממשק עם מערכות משנה מרובות בו זמנית, מה שהופך אותו למתאים לעיצובים מורכבים ברמת הלוח.

• • מתח ליבה (VCC)

הליבה פועלת בטווח 1.8 וולט נומינלי (1.7 וולט עד 1.9 וולט), המסייע בהפחתת צריכת החשמל בהשוואה ל- CPLDs ישנים יותר של 5 וולט.מתח נמוך יותר זה שימושי במערכות דיגיטליות מודרניות במתח מעורב.

• • תמיכה בקלט/פלט רב מתח

בנקי הקלט/פלט תומכים בתקני מתח מרובים הכוללים 1.5 וולט, 1.8 וולט, 2.5 וולט ו -3.3 V. גמישות זו מאפשרת ל- CPLD להתממשק ישירות עם רכיבים הפועלים ברמות מתח שונות ללא מעברי רמה חיצונית.

• • פעולה במהירות גבוהה

עם עיכוב התפשטות סיכה לסיכה טיפוסית של כ- 5.7 NS (דרגה מהירות "-7"), המכשיר מספק ביצועים מהירים ודטרמיניסטיים.זה הופך אותו למתאים ליישומים קריטיים לתזמון כמו פענוח כתובות, בוררות באוטובוס ובקרה.

• • צריכת חשמל נמוכה

סדרת CoolRunner-II ידועה בזרמי המתנה נמוכים במיוחד, לרוב בטווח המיקרו-אמפר.כוח סטטי נמוך זה, בשילוב עם תכונות חיסכון בחשמל דינאמי, מאפשר לשימוש ביעילות במערכות המונעות על סוללה או תמיד תמיד.

• • טכנולוגיית Datagate

תכונה זו מאפשרת לשחרר תשומות שאינן בשימוש, למנוע מיתוג מיותר והפחתת צריכת החשמל הדינמית.זה חשוב ביישומים שבהם אותות מסוימים אינם פעילים לתקופות ארוכות.

• • תכנות JTAG במערכת

המכשיר תומך ב- IEEE 1149.1 (JTAG) ו- IEEE 1532 לתכנות במערכת.המשמעות היא שניתן להגדיר, לבדוק ולתכנת מחדש את CPLD מבלי להסיר אותו מהלוח, לפשט את הפיתוח והעדכונים.

• • מבנה מתקדם לענג

XC2C256-7TQ144C כולל שעונים גלובליים מרובים, מחלקות שעון ורישומים מופעלים כפולים.זה גם מספק סט/איפוס גלובלי ועליקה מקומית לכל תאי מקרו, ומעניק שליטה גמישה על תזמון וסנכרון.

• • כניסות Schmitt-Trigger

ניתן להגדיר סיכות קלט שנבחרו כמפעילות שמיט לשיפור חסינות הרעש.זה שימושי לטיפול באותות קלט איטי או רועש מבלי להוסיף מעגלי מיזוג חיצוניים.

• • תכונות פלט גמישות

התפוקות תומכות בפעולה בת שלוש מדינות, בקרת קצב ההרג, אחיזת האוטובוס, תצורות ניקוז פתוח ומשיכות אופציונליות.אפשרויות אלה מקלות על התאמת ה- CPLD לתקני אוטובוס שונים ותנאי עומס חיצוניים.

• • מטריצה מתקדמת (AIM) מתקדמת (AIM)

מטריצה מתקדמת של חיבור מקשר ביעילות קושרת חסימות פונקציות, ומספקת ניתוב מלא לטווח המוצר על פני המכשיר.זה משפר את גמישות מיקום ההיגיון ועוזר לשמור על ביצועי תזמון צפויים.

ארכיטקטורת CoolRunner-II CPLD

ארכיטקטורת CPLD של CoolRunner-II של ה- XC2C256-7TQ144C בנוי סביב בלוקי פונקציות, בלוקי קלט/פלט ומטריצה מתקדמת של חיבור (AIM).כל בלוק פונקציות מכיל תאי מקרו ומערך לוגיקה הניתן לתכנות (PLA) המיישמים היגיון מוגדר על ידי המשתמש, בעוד שהמטרה מסללת ביעילות את האותות בין בלוקים.חסימות הקלט/פלט ממשק את ההיגיון הפנימי עם סיכות חיצוניות, ומעגלי JTAG ייעודיים ו- BSC/ISP תומכים בתכנות ובבדיקה במערכת.ארכיטקטורה מובנית ומחוברת זו בזו מאפשרת ביצועים מהירים ודטרמיניסטיים עם צריכת חשמל נמוכה, מה שהופך אותה לאידיאלית לשליטה, ממשק והדבקת היגיון במערכות דיגיטליות.

עקומת I/V אופיינית עבור XC2C256

עקומת ה- I/V האופיינית עבור XC2C256-7TQ144C ממחישה את הקשר בין מתח יציאה (VO) לזרם פלט (IO) למתחי אספקת קלט/פלט שונים (1.5 וולט, 1.8 וולט, 2.5 וולט ו -3.3 וולט).ככל שמתח האספקה גדל, המכשיר יכול למקם או לשקוע זרמים גבוהים יותר לפני שמתח הפלט מתחיל לרדת משמעותית.התנהגות זו חשובה להבנת יכולת הכונן של ה- CPLD כאשר מתממשקים לרכיבים חיצוניים, מה שמבטיח שרמות האות יישארו תקפות בעומס.רבים משתמשים בעקומה זו כדי לבחור מתחי קלט/פלט מתאימים ולהבטיח פעולה אמינה ביישומים הדורשים חוזקות לנהיגה זרם ספציפית.

מפרטים XC2C256-7TQ144C

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

AMD/XILINX |

|

סִדרָה |

Coolrunner II |

|

אריזה |

מַגָשׁ |

|

סטטוס חלק |

מְיוּשָׁן |

|

סוג הניתן לתכנות |

במערכת הניתנת לתכנות |

|

זמן עיכוב TPD (1) מקסימום |

6.7 נ.ס. |

|

אספקת מתח - פנימית |

1.7 V ~ 1.9 V |

|

מספר אלמנטים/בלוקים לוגיים |

16 |

|

מספר תאי מקרו |

256 |

|

מספר השערים |

6000 |

|

מספר קלט/פלט |

118 |

|

טמפרטורת הפעלה |

0 ° C ~ 70 ° C (Ta) |

|

סוג הרכבה |

הר השטח |

|

חבילה / מקרה |

144-LQFP

|

|

חבילת מכשירי ספק |

144-TQFP (20 × 20) |

|

מספר מוצר בסיס |

XC2C256 |

יישומי XC2C256-7TQ144C

1. היגיון דבק וגישור ממשק

ה- XC2C256-7TQ1444C אידיאלי ליישום היגיון דבק, המחבר ומתאם אותות בין רכיבים דיגיטליים שונים.זה יכול להתמודד עם פונקציות כמו פענוח כתובות, בוררות אוטובוס ותרגום פרוטוקול, מה שמאפשר תקשורת חלקה בין מיקרו -בקרי, זיכרון, חיישנים, וציוד היקפי אחרים.העיתוי הצפוי והעיכובים המהירים של סיכות לסיכות מבטיחים ממשק אמין אפילו בעיצובים של לוח מורכבים.

2. מכשירים בעלי עוצמה נמוכה ומופעלים על סוללות

הודות לטכנולוגיית ה- Fast Zero Power (FZP) וזרם המתנה נמוך מאוד, CPLD זה מתאים מאוד לאלקטרוניקה ניידת ומונעת סוללות.זה יכול להישאר מופעל ברציפות תוך צריכת אנרגיה מינימלית, מה שהופך אותה למושלמת לבקרה או מעגלים מעקב תמיד.אתה יכול להפחית את השימוש בחשמל עוד יותר עם תכונות כמו Datagate, שממזער את המיתוג הדינאמי כאשר הכניסות אינן פעילות.

3. היגיון בקרה ורצף

המכשיר מצטיין ביישום מכונות מצב סופיות, בקרת תזמון ורצף איתות הנדרש במערכות משובצות רבות.הארכיטקטורה הדטרמיניסטית והלא נדיפה שלה מאפשרת להיגיון הבקרה להיות פעיל מיד לאחר ההפעלה ללא עיכובים בתצורה.זה הופך את זה לבחירה חזקה עבור איפוס לוגיקה, מעגלי לחיצת יד ומשימות בקרה קריטיות בזמן.

4. תמיכה במערכת משובצת והיגיון היקפי

בעיצובים משובצים, XC2C256-7TQ144C יכול לשמש כשבב תמיכה הניתן להתאמה אישית, ליישם ממשקים מיוחדים או להרחיב יכולות של בקר מיקרו.זה יכול להתמודד עם פרוטוקולי תקשורת כמו SPI, I²C או UART, ליצור בחירת שבבים או לנהל ניתוב הפרעות.על ידי הפסקת פונקציות אלה מהמעבד, היא מפשטת את פיתוח הקושחה ומשפרת את ביצועי המערכת הכוללים.

XC2C256-7TQ144C חלקים דומים

|

מִפרָט |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

XC2C256-7TQG144I |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

משפחת מכשירים |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

|

צפיפות לוגיקה (תאי מקרו) |

256 |

256 |

256 |

256 |

256 |

256 |

|

סוג חבילה |

TQFP-144 |

TQFP-144 |

TQFP-144 (PB-Free) |

VQFP-100 |

VQFP-100 (ללא PB) |

TQFP-144 |

|

ציון מהירות |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (מהיר יותר) |

|

טווח טמפרטורות |

מסחרי (0 - 70 מעלות צלזיוס) |

תעשייתי (-40-85 מעלות צלזיוס) |

תעשייתי (-40-85 מעלות צלזיוס) |

מסחרי (0 - 70 מעלות צלזיוס) |

מסחרי (0 - 70 מעלות צלזיוס) |

מסחרי (0 - 70 מעלות צלזיוס) |

|

ספירת סיכות קלט/פלט |

118 |

118 |

118 |

80 |

80 |

118 |

|

מתח ליבה (VCC) |

1.8 וולט |

1.8 וולט |

1.8 וולט |

1.8 וולט |

1.8 וולט |

1.8 וולט |

|

תמיכה במתח קלט/פלט |

1.5 V - 3.3 וולט |

1.5 V - 3.3 וולט |

1.5 V - 3.3 וולט |

1.5 V - 3.3 וולט |

1.5 V - 3.3 וולט |

1.5 V - 3.3 וולט |

|

ציות / PB ללא |

תֶקֶן |

תֶקֶן |

PB-Free / ROHS |

תֶקֶן |

PB-Free / ROHS |

תֶקֶן |

|

הבדלים |

גרסה מסחרית בסיסית |

גרסת טמפ 'תעשייתית |

גרסה תעשייתית + PB ללא PB |

חבילה קטנה יותר, פחות קלט/פלט |

גרסה קטנה יותר ללא PB |

גרסת תזמון מהירה יותר |

XC2C256-7TQ144C שלבי תכנות

תכנות ה- XC2C256-7TQ144C הוא תהליך פשוט הכולל הכנת העיצוב שלך, יצירת קובץ התכנות והטענתו ל- CPLD דרך JTAG.על ידי ביצוע כל שלב בזהירות, באפשרותך להבטיח תצורה מוצלחת ופעולת התקנים מתאימה בלוח שלך.

1. עיצוב וסינתזה

אתה מתחיל בכתיבת עיצוב ההיגיון שלך באמצעות HDL (VHDL או Verilog) או כניסה סכמטית.לאחר השלמת העיצוב, אתה מפעיל את תהליך הסינתזה, שממיר את ההיגיון שלך למבנה הפנימי של המכשיר של תאי מקרו וקשרי חיבורים.שלב זה מבטיח שהעיצוב שלך תואם לארכיטקטורת XC2C256 ומוכן ליישום.

2. מקום ומסלול / יישום (מתאים)

בשלב הבא, אתה מבצע מקום ונתיב, הידוע גם בשם התאמה, שמקצה את ההיגיון המסונתז שלך לתאי מקרו פיזיים ומשאבי ניתוב בתוך ה- CPLD.הכלים בודק את אילוצי העיתוי, פותר שימוש במשאבים ומייעל נתיבים כדי לעמוד בביצועי העיצוב שלך.זה מבטיח שהמעגל יפעל באופן אמין לאחר שתוכנת למכשיר.

3. צור קובץ תכנות

לאחר השלמת היישום, אתה מייצר את קובץ התכנות (פורמט סיביות, ריבה או SVF) המכיל את נתוני התצורה המדויקים עבור המכשיר.קובץ זה מייצג את האופן בו כל מקרו -תאי, Interconnect ו- I/O מוגדרים ליישום ההיגיון שלך.יש צורך בהכנת קובץ זה לפני שתעבור לתכנות המכשירים בפועל.

4. JTAG / תכנות במערכת

לבסוף, אתה מחבר את המכשיר למחשב שלך באמצעות כבל תכנות JTAG ופותח את כלי ה- Xilinx Impact (או שווה ערך).לאחר מכן אתה טוען את קובץ התכנות שנוצר ומוריד אותו ל- XC2C256-7TQ144C דרך סיכות JTAG (TDI, TDO, TCK, TMS).לאחר השלמת התהליך, ה- CPLD מתחיל מיד לפעול עם ההיגיון המתוכנת שלך, מבלי לדרוש מחזור כוח או זיכרון תצורה חיצוני.

XC2C256-7TQ144C יתרונות וחסרונות

יתרונות

• כוח המתנה נמוך מאוד, אידיאלי לעיצובים המונעים על סוללות.

• פעולה מיידית ללא עיכוב תצורה.

• תזמון צפוי לסגירת עיצוב קלה יותר.

• מחליף שבבי לוגיקה נפרדים מרובים, חיסכון בשטח ועלות.

• תומך במתחי קלט/פלט מרובים ללא מעברי רמה חיצונית.

חסרונות

• יכולת היגיון מוגבלת בהשוואה ל- CPLDs או FPGAs גדולים יותר.

• אין משדרים מובנים DSP, RAM או משדרים במהירות גבוהה.

• להיות מיושן, מה שמקשה על המקור העתידי.

• תקרת ביצועים נמוכה יותר ליישומים במהירות גבוהה.

• פחות גמישות ניתוב לעיצובים מורכבים או לא סדירים.

XC2C256-7TQ144C מידות אריזה

|

סוּג |

פָּרָמֶטֶר |

|

סוג חבילה |

TQFP-144 |

|

גודל גוף החבילה |

20 מ"מ × 20 מ"מ |

|

מגרש עופרת |

0.5 מ"מ |

|

מספר הסיכות |

144 |

|

גובה החבילה (מקסימום) |

1.4 מ"מ |

|

עובי החבילה (נומינלי) |

1.0 מ"מ |

|

אורך עופרת |

0.45 מ"מ ~ 0.75 מ"מ |

|

רוחב עופרת |

0.17 מ"מ ~ 0.27 מ"מ |

|

סוג הרכבה |

הר השטח |

|

חבילת מכשירי ספק |

144-TQFP (20 × 20) |

XC2C256-7TQ144C יצרן

XC2C256-7TQ144C מיוצר על ידי Xilinx, חברה מובילה בפתרונות לוגיים הניתנים לתכנות.Xilinx מוכר באופן נרחב בטכנולוגיות FPGA ו- CPLD חלוציות, ומספק מכשירים אמינים וביצועים גבוהים ליישומים תעשייתיים, מסחריים וצרכניים.כיום, Xilinx פועל כחלק מ AMD, ממשיכים לספק מוצרי לוגיקה מתקדמים לתכנות עם תמיכה וחדשנות חזקים לטווח הארוך.

מַסְקָנָה

XC2C256-7TQ1444C בולט בצריכת החשמל הנמוכה שלו, ביצועים דטרמיניסטיים מהירים וגמישות קלט/פלט רב מתח, מה שהופך אותו לבחירה אמינה עבור עיצובים דיגיטליים מודרניים.השילוב המאוזן שלו של 256 תאי מקרו, 118 סיכות קלט/פלט ואדריכלות קשרים מתקדמת תומך במגוון רחב של פונקציות בקרה, ממשק והדבק.עם תמיכה בתכנות במערכת, תכונות חיסכון בכוח של נתונים, ותצורות קלט/פלט חזקות, היא משתלבת בצורה חלקה במערכות משובצות וסביבות מתח מעורב.

גיליון נתונים PDF

XC2C256-7TQ144C גיליונות נתונים:

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. האם XC2C256-7TQ144C דורש זיכרון תצורה חיצוני?

לא. אחד היתרונות שלה הוא פעולה מיידית.התצורה מאוחסנת באופן פנימי, ולכן היא מעצמת מוכנה להפעלה ללא כל זיכרון נשף או פלאש חיצוני.

2. אילו כלי תכנות תואמים ל- XC2C256-7TQ144C?

באפשרותך לתכנת את המכשיר באמצעות תוכנת אימפקט Xilinx באמצעות כבל תכנות JTAG.רבים משתמשים גם במתכנתי JTAG של צד שלישי תואם, אך וודאו שהם תומכים בתקני IEEE 1149.1/1532.

3. האם XC2C256-7TQ144C יכול להחליף ICS לוגיקה דיסקרטית בעיצוב שלך?

כֵּן.עם 256 תאי מקרו וקלט/פלט גמישים, CPLD זה יכול לשלב מספר פונקציות לוגיקה ובקרה של דבק במכשיר אחד, ולסייע לך להפחית את שטח הלוח וספירת הרכיבים.

4. האם XC2C256-7TQ144C מתאים ליישומי סוללה בעלת עוצמה נמוכה?

כֵּן.הודות לטכנולוגיית ה- Fast Zero Power (FZP) וזרם המתנה נמוך מאוד, זה אידיאלי למעגלים תמיד, מכשירים ניידים ומערכות משובצות רגישות לחשמל.

5. האם אתה יכול להשתמש ב- XC2C256-7TQ144C לצורך עיבוד אותות במהירות גבוהה?

זה לא מיועד למשימות DSP או משדר במהירות גבוהה.אמנם הוא מספק עיכובים מהירים לפינים, אך הוא מתאים ביותר לשליטה, ממשק וליגיון תזמון, ולא לעיבוד נתונים מורכב.

EP2S60F672C4 FPGA: תכונות, יישומים, מדריך לתכנות ומדריך לנתונים

ב- 2025/10/4

EPM3256AFC256-7 סקירה כללית של CPLD: תכונות, פינאוט, תכנות ויישומים

ב- 2025/10/3

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/19 147781

-

Pinout USB-C ותכונות

ב- 2000/04/19 112051

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/19 111352

-

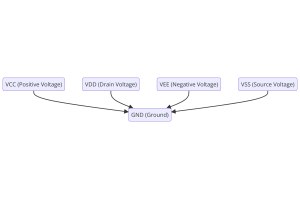

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/19 83806

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79610

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66991

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63113

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63051

-

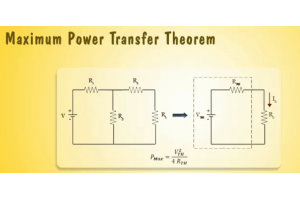

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54097

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52200