EP2S60F672C4 FPGA: תכונות, יישומים, מדריך לתכנות ומדריך לנתונים

במדריך זה תקבלו סקירה ברורה של ה- EP2S60F672C4, FPGA חזק ממשפחת סטרטיקס II של אינטל.תלמד על התכונות העיקריות שלה, הארכיטקטורה, מבנה החסימה והמפרט הטכני שלה כדי להבין כיצד היא מתאימה לעיצובים דיגיטליים מתקדמים.זה גם מעביר אותך בשלבי התכנות, היישומים, היתרונות והחסרונות שלו, כך שתוכל לראות בדיוק היכן וכיצד ניתן להשתמש במכשיר זה.קָטָלוֹג

מהו EP2S60F672C4?

THE EP2S60F672C4 הוא FPGA בצפיפות גבוהה של אינטל (לשעבר אלטרה), השייך למשפחת סטרטיקס II.הוא בנוי על תהליך SRAM של 90 ננומטר, 1.2 וולט נחושת, הוא מספק יכולת לוגיקה משמעותית בתוך חבילת FBGA של 672 כדור, מה שהופך אותו לאידיאלי למערכות דיגיטליות מורכבות.כחלק מסדרת ה- EP2S, מכשיר "60" יושב בטווח האמצע-עליון של מערך סטרטיקס II, ומציע איזון חזק של צפיפות ההיגיון, זיכרון משובץ ומשאבי קלט/פלט.FPGA זו ידועה בזכות הארכיטקטורה החזקה והאמינות שלה, נותרה בחירה מהימנה בעיצובים מתקדמים רבים.

מחפש EP2S60F672C4?צרו קשר כדי לבדוק את המלאי הנוכחי, זמן ההובלה והתמחור.

דגמי CAD של EP2S60F672C4

סמל EP2S60F672C4

טביעת רגל EP2S60F672C4

EP2S60F672C4 דגם 3D

תכונות EP2S60F672C4

• • תהליך מתקדם של 90 ננומטר, 1.2 וולט CMOS

EP2S60F672C4 מפוברק בתהליך CMOS של 90 ננומטר של CMOS הנחושת של 90 ננומטר הפועל במתח ליבה של 1.2 וולט.טכנולוגיה זו מאפשרת מהירות גבוהה, צריכת חשמל מופחתת וצפיפות לוגית גדולה יותר בהשוואה לדורות FPGA ישנים יותר.

• • ארכיטקטורת מודול לוגיקה אדפטיבית (ALM)

המכשיר משתמש ב- ALMS כאבן הבניין הלוגיקה שלו במקום אלמנטים לוגיים מסורתיים.ארכיטקטורה זו משפרת את השימוש במשאבים, ומאפשרת ליישם פונקציות לוגיות מורכבות יותר ביעילות באותו אזור סיליקון.

• • צפיפות היגיון גבוהה

עם כ- 60,440 אלמנטים לוגיים (24,176 ALMS), ה- FPGA תומך בעיצובים דיגיטליים גדולים ומתוחכמים.קיבולת גבוהה זו הופכת אותו למתאים ליישומים כמו עיבוד אותות, תקשורת ומערכות בקרה משובצות.

• • זיכרון ™ Trimatrix ™ שבב

EP2S60F672C4 משלב שלושה סוגים של בלוקים RAM, (M512, M4K ו- M-RAM) כדי לספק סך של כ -2.4 מגה-ביטים של זיכרון משובץ.תערובת זו מאפשרת ליישם ביעילות FIFOs קטנים, מאגרים בינוניים וזיכרונות גדולים של יציאה כפולה.

• • חסימות DSP ייעודיות

המכשיר כולל 36 בלוקים DSP ייעודיים המיועדים לפעולות חשבון כמו כפל, הצטברות וסינון FIR.חסימות אלה מגבירות את הביצועים במשימות אינטנסיביות לחישוב תוך שמירה על משאבי לוגיקה כלליים.

• • קלט/פלט במהירות גבוהה ושלמות איתות

הוא תומך בתקני קלט/פלט שונים עם דיפרנציאל יחד עם מעגלי יישור פאזה דינאמי (DPA).תכונות אלה מאפשרות להעביר נתונים יציבים במהירות גבוהה עד 1 ג'יגה-ביט לשנייה, ומבטיחים תקשורת אמינה עם רכיבים חיצוניים.

• • תמיכה בממשק זיכרון חיצוני עשיר

ה- FPGA תואם ל- DDR, DDR2, QDR II, RLDRAM II ותקני זיכרון אחרים.תמיכה בממשק מובנה מפשטת את תכנון הלוח ומשיג תפוקת נתונים גבוהה ליישומים עתירי זיכרון.

• • ניהול שעון גמיש

עד 12 PLLs על השבב מאפשרים כפל שעון, חלוקה, העברת פאזות ומעבר ללא תקלות.אתה יכול לכוונן תחומי שעון ולהקטין את הריצוד, ולתמוך בתדרי שעון פנימיים של עד 500–550 מגה הרץ.

• • הצפנה ותצורה מחדש של Bitstream

EP2S60F672C4 תומך בהצפנת Bittream מבוסס AES כדי להבטיח קניין רוחני.הוא מציע גם יכולת תצורה מחדש מרחוק, ומאפשרת עדכונים בשדה מבלי להחליף את המכשיר.

תרשים בלוק סטרטיקס II

תרשים החסימה של Stratix II, כפי שמוצג עבור EP2S60F672C4, ממחיש את הסידור הפנימי של משאבי ההיגיון, הזיכרון וה- DSP המהווים את ליבת ה- FPGA.חסימות מערך לוגיות (מעבדות) מסודרות ברשת רגילה, מוקפים בעמודי זיכרון RAM ועמודי DSP משובצים, המספקים יכולות אחסון מהירות אריתמטיות ושבב.רכיבי קלט/פלט היקפיים ורשתות שעון מסגרים מבנה זה, ומאפשרים העברת נתונים יעילה ובקרת תזמון בין ה- FPGA למכשירים חיצוניים.תרשים זה חשוב מכיוון שהוא עוזר להבין כיצד חסימות פונקציונליות שונות מאורגנות פיזית, ומאפשרות להם לייעל את ביצועי המיקום, הניתוב וביצועי המערכת הכוללים.

סטרטיקס II I/O תרשים בנקים

דיאגרמת בנקים של סטרטיקס II II II ממחישה כיצד מקובצים סיכות הקלט/פלט של EP2S60F672C4 ואילו תקנים חשמליים כל קבוצה תומכת.כל בנק קלט/פלט נועד לטפל ברמות מתח ספציפיות, סוגי איתות ופונקציות כמו LVTTL, SSTL, LVDs או תקני כניסה לשעון.הפריסה מראה כיצד בנקים שונים (למשל, 1, 2, 5, 6 לעומת 3, 4, 7, 8 וכו ') מותאמים לאופטימיזציה של קלט/פלט כללי או לאיתות דיפרנציאלי במהירות גבוהה, כולל תמיכה בכניסות שעון LVD/LVPECL בקצוות.הבנת מבנה זה חשובה בעת הקצאת סיכות, מכיוון שבחירה נכונה בבנק מבטיחה תאימות חשמלית, מפשטת את ניתוב הלוח וממקסמת את ביצועי ה- FPGA בעיצובים במהירות גבוהה.

מפרטי EP2S60F672C4

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

Altera/Intel |

|

סִדרָה |

Stratix® II |

|

אריזה |

מַגָשׁ |

|

סטטוס חלק |

מְיוּשָׁן |

|

מספר המעבדות/CLBs |

3022 |

|

מספר אלמנטים/תאים לוגיים |

60,440 |

|

סה"כ פיסות זיכרון RAM |

2,544,192 |

|

מספר קלט/פלט |

492 |

|

מתח - אספקה |

1.15 V ~ 1.25 V |

|

סוג הרכבה |

הר השטח |

|

טמפרטורת הפעלה |

0 ° C ~ 85 ° C (TJ) |

|

חבילה / מקרה |

672-BBGA |

|

חבילת מכשירי ספק |

672-FBGA (27 × 27) |

|

מספר מוצר בסיס |

EP2S60 |

יישומי EP2S60F672C4

1. עיבוד אות דיגיטלי (DSP) וסינון

EP2S60F672C4 מתאים היטב ליישום פונקציות DSP בעלות ביצועים גבוהים כמו מסנני FIR ו- IIR, עיבוד FFT ופעולות חשבון מורכבות.בלוקי ה- DSP הייעודיים שלה מטפלים בכפל וצבירה ביעילות, ומשחררים משאבי לוגיקה כלליים למשימות אחרות.הזיכרון ™ Trimatrix ™ On-Chip מאפשר חיץ וצנרת נתונים חלקים, וזה נהדר לעיבוד בזמן אמת בשיעורי מדגם גבוהים.זה הופך את המכשיר לאידיאלי ליישומי אודיו, וידאו ורדאר מתקדמים.

2. תקשורת ורשתות במהירות גבוהה

ממשקי הקלט/פלט במהירות גבוהה של ה- FPGA ומעגלי יישור פאזה דינאמי (DPA) תומכים בהעברת נתונים אמינה וברמת ג'יגה.זה יכול ליישם פרוטוקולי תקשורת ופונקציות שכבה פיזית עבור מערכות כמו נתבים, מתגים וקשרי חיבורים של מטוס אחורי.עם יכולת ההיגיון הגדולה וה- PLLs הגמישים שלו, היא יכולה לנהל המרות תזמון מורכבות ופרוטוקול בין ממשקים במהירות גבוהה.יכולות אלה הופכות אותו להתאמה חזקה לתשתיות טלקום וציוד רשת רוחב פס גבוה.

3. בקרי זיכרון ומערכות עיבוד נתונים

EP2S60F672C4 תומך בממשקי זיכרון חיצוניים שונים הכוללים DDR, DDR2, RLDRAM II ו- QDR II, מה שהופך אותו לאידיאלי לעיצוב בקרי זיכרון רוחב פס גבוה.זה יכול להתמודד עם חציצות נתונים, ייצור כתובת ובוררות במהירות גבוהה עם חביון מינימלי.השילוב של רשתות שעון מהירות וחסימות זיכרון RAM משובצות מאפשר ניהול יעיל של זרמי נתונים גדולים.זה הופך את ה- FPGA המתאים לעיבוד תמונות, הזרמת וידאו ופלטפורמות חישוב מדעיות המסתמכות על תפוקת נתונים כבדה.

4. היגיון מותאם אישית ותאוצה משובצת

עם למעלה מ- 60,000 אלמנטים לוגיים וניהול שעון עשיר, ה- FPGA יכול לארח מאיצים חומרה מותאמים אישית לאלגוריתמים ספציפיים.לעיתים קרובות מעצבים משתמשים בו כדי להוריד משימות אינטנסיביות חישובית ממעבדים, כמו הצפנה, ניתוח פרוטוקול או לולאות בקרה בזמן אמת.זה יכול גם לשלב בלוקים פונקציונליים מרובים, מה שהופך אותו מתאים לעיצובים מורכבים כמו SOC.גמישות זו הופכת אותו ליקר ביישומים כמו אוטומציה תעשייתית, מערכות אבטחה ויחידות לבקרת תעופה וחלל.

5. פלטפורמות אבות -טיפוס ופיתוח חינוכי

מכשיר ה- EP2S60 נמצא בדרך כלל על ערכות פיתוח FPGA המשמשות לטיפוס, בדיקות ומחקר אקדמי.איזון יכולות ההיגיון, ספירת הקלט/פלט ויכולות ה- DSP מאפשר למהנדסים וסטודנטים ליישם ולאמת מערכות מלאות על שבב יחיד.הוא תומך באיטרציה מהירה של עיצובים דיגיטליים, ומאפשר אימות חומרה לפני שמתחייב לפיתוח ASIC.אוניברסיטאות ומעבדות מו"פ רבות משתמשים בה כדי ללמד מושגי תכנון דיגיטלי ועיבוד אותות מתקדמים.

EP2S60F672C4 חלקים דומים

|

מִפרָט |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

משפחה / סדרה |

סטרטיקס II |

סטרטיקס II |

סטרטיקס II |

סטרטיקס II |

סטרטיקס II |

סטרטיקס II |

|

אלמנטים לוגיים (LE) |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

|

נְדָבָה |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

|

חֲבִילָה |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

ציון מהירות |

C4 (STD) |

C3 (מהיר יותר) |

C5 (מהיר יותר) |

C5 (מהיר יותר) |

I4 (std) |

I3 (מהיר יותר) |

|

ציון טמפרטורה |

מסחרי (0 ~ 70 מעלות צלזיוס) |

מִסְחָרִי |

מִסְחָרִי |

מִסְחָרִי |

תעשייתי (−40 ~ 100 מעלות צלזיוס) |

תעשייתי (−40 ~ 100 מעלות צלזיוס) |

|

סיכות קלט/פלט |

492 |

492 |

492 |

492 |

492 |

492 |

|

זיכרון על השבב |

2.4 מגהביט |

2.4 מגהביט |

2.4 מגהביט |

2.4 מגהביט |

2.4 מגהביט |

2.4 מגהביט |

|

מתח ליבה |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

|

הפרש מפתח |

מהירות מסחרית בסיסית |

C3 Speed Bin, "N" נטולת עופרת |

סל מהירות גבוה יותר |

גרסת מהירות גבוהה יותר, "N" |

טמפרטורה תעשייתית, אותה צפיפות |

מהירות תעשייתית, מהירה יותר, ללא עופרת |

EP2S60F672C4 שלבי תכנות

לפני שתוכל להשתמש ב- EP2S60F672C4 FPGA בעיצוב שלך, עליך להגדיר אותו כראוי עם הזרם המוערך שלך.תהליך זה כרוך בהכנת קובץ התכנות, הגדרת ממשק החומרה והבטחת התצורה נטענת כראוי בהפעלה.

שלב 1: צור והרכיב את העיצוב שלך

אתה מתחיל בפיתוח עיצוב ההיגיון שלך באמצעות תוכנת אינטל קווארטוס II.לאחר השלמת העיצוב, אתה אוסף אותו לייצר את קובץ התכנות (.sof או .pof) במיוחד עבור מכשיר EP2S60F672C4.תהליך ההדרכה בודק את העיתוי, הקצאות סיכות ושימוש במשאבים כדי להבטיח שהעיצוב שלך יתאים לארכיטקטורה של ה- FPGA.לאחר ההרכבה, זרם ה- Bitstream שלך מוכן לתצורת המכשירים.

שלב 2: הגדר את חומרת התכנות

בשלב הבא אתה מכין את ממשק התכנות הפיזי בין המחשב שלך ללוח FPGA.בדרך כלל, זה כרוך בחיבור כבל USB-Blaster או כבל JTAG תואם ליציאת JTAG של המכשיר.עליך לוודא ש- Quartus II מזהה את המתכנת וכי מכשיר היעד מתגלה כראוי.שלב זה מבטיח תקשורת יציבה לפני שתתחיל בתהליך התצורה.

שלב 3: טען את קובץ התכנות למכשיר

בעזרת הכלי המתכנת Quartus II, אתה מוסיף את קובץ ה- .sof או .pof.לאחר מכן אתה יוזם את רצף התכנות, שבמהלכו מועבר הזרם Bitstream ונטען לתאי התצורה של ה- SRAM של ה- FPGA.עליך לפקח על סרגל ההתקדמות והודעות הסטטוס כדי לאשר תצורה מוצלחת.לאחר השלמתו, ה- FPGA מתחיל לבצע את ההיגיון המתוכנת מייד.

שלב 4: אמת את התצורה והתפעול

לאחר התכנות, אתה מוודא שהמכשיר פועל כמתוכנן.Quartus II מספק אפשרות אימות לבדיקת אותות CRC ותצורה של CRC, ומבטיח כי העיצוב נטען כראוי.אתה יכול גם לבדוק את פונקציות הקלט/פלט שלך או להריץ סימולציה פונקציונלית כדי לאשר את התנהגות המערכת.שלב אחרון זה מבטיח שהעיצוב שלך פועל לחלוטין ויציב בחומרה.

EP2S60F672C4 יתרונות וחסרונות

יתרונות

• צפיפות היגיון גבוהה לעיצובים מורכבים

• יחס ביצועים טוב לעלות

• הגירה קלה בתוך אותה משפחה

• כלי פיתוח יציבים ובוגרים

• אמינות מוכחת בשימוש תעשייתי

חסרונות

• מיושן וקשה יותר למקור

• צריכת חשמל גבוהה יותר מאשר FPGAs חדשים יותר

• אין משדרים מודרניים במהירות גבוהה

• סגירת תזמון קשה יותר עם ניצול גבוה

• מדרגיות מוגבלת לפרוטוקולים עתידיים

EP2S60F672C4 מידות אריזה

|

סוּג |

פָּרָמֶטֶר |

|

סוג חבילה |

672-FBGA (Fineline BGA) |

|

גודל גוף (l × w) |

27.00 מ"מ × 27.00 מ"מ |

|

גובה החבילה הכולל (א) |

מקסימום 3.50 מ"מ |

|

גובה עומד (A1) |

דקות 0.30 מ"מ |

|

עובי מצע (A2) |

מקסימום 3.00 מ"מ |

|

קוטר הכדור (ב) |

0.50 מ"מ - 0.70 מ"מ |

|

מגרש כדור (ה) |

1.00 מ"מ |

|

מספר הכדורים |

672 |

|

סגנון הרכבה |

הר השטח |

|

תיאור החבילה |

FBGA, רשת 27 × 27 מ"מ |

יצרן EP2S60F672C4

ה- EP2S60F672C4 FPGA מיוצר על ידי תאגיד אלתרה, חלוץ מוביל במכשירי לוגיקה הניתנים לתכנות.בשנת 2015 נרכשה אלתרה על ידי אינטלוהמוצר נופל כעת תחת קבוצת הפתרונות הניתנים לתכנות של אינטל (PSG), שממשיכה לתמוך ולספק את משפחות ה- FPGA המבוססות של Altera.אינטל שומרת על קו Stratix II כחלק מתיק המוצרים Legacy שלה, ומבטיח תיעוד, תמיכה בכלי וזמינות לטווח הארוך ליישומי תעשייה ותקשורת.

מַסְקָנָה

ה- EP2S60F672C4 משלב צפיפות לוגית גבוהה, ארכיטקטורת זיכרון גמישה ותכונות קלט/פלט חזקות לתמיכה במערכות דיגיטליות מורכבות.התכנון מבוסס ALM, זיכרון Trimatrix ™, חסימות DSP ותכונות ניהול שעון מאפשר יישום יעיל של יישומים תובעניים.למרות שהיא מציעה אמינות מוכחת ותמיכה בפיתוח בוגר, היא עומדת בפני מגבלות כמו התיישנות והיעדר משדרים מודרניים בהשוואה לדורות חדשים יותר של FPGA.בסך הכל, הביצועים המאוזנים והגמישות שלו הופכים אותה לבחירה מוצקה עבור יישומי עיבוד אותות, תקשורת, טיפול בנתונים ואב -טיפוס.

גיליון נתונים PDF

EP2S60F672C4 גיליונות נתונים:

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. האם EP2S60F672C4 יכול לעבוד עם ממשקי זיכרון DDR מודרניים?

כן, הוא תומך בממשקי DDR, DDR2, QDR II ו- RLDRAM II, המכסים תקני זיכרון חיצוניים נפוצים רבים.זה הופך אותו למתאים ליישומי עיבוד נתונים ברוחב רוחב גבוה.

2. האם EP2S60F672C4 דורשים טיפול או אחסון מיוחד?

כן, כמו רכיבים אחרים הארוזים של BGA, יש לאחסן אותו באריזה מבוקרת לחות ולטפל בה בהגנת ESD.ביצוע נוהלי אחסון נאותים מסייע בשמירה על יכולת הלחמה ואמינות המכשירים במהלך ההרכבה.

3. כיצד תוכלו להפחית את צריכת החשמל בעיצובים EP2S60F672C4?

אתה יכול לייעל את השימוש בהיגיון, שעונים ללא שימוש בשער, מתחי קלט/פלט נמוכים יותר במידת האפשר, ולמנף אפשרויות סינתזת מודעות להפעלה ב- Quartus II כדי למזער את משיכת ההספק הכוללת.

4. אילו כלי תכנות נדרשים ל- EP2S60F672C4?

תזדקק לתוכנת אינטל קווארטוס II לצורך תכנון, אוסף ותכנות, יחד עם כבל USB-Blaster או כבל JTAG תואם כדי להגדיר את המכשיר.

5. האם EP2S60F672C4 תומך בעדכונים בשטח או בתצורה מחדש מרחוק?

כן, הוא תומך בהצפנת Bitstream מבוסס AES ותצורה מחדש מרחוק, ומאפשר לך לעדכן את המערכת שלך בצורה מאובטחת מבלי להחליף פיזית את ה- FPGA.

הכל על LFXP6C-3FN256C סריג מוליך למחצה

ב- 2025/10/6

XC2C256-7TQ144C CPLD: PINOUT, תכונות, מדריך לתכנות וגליון נתונים

ב- 2025/10/3

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/19 147783

-

Pinout USB-C ותכונות

ב- 2000/04/19 112073

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/19 111352

-

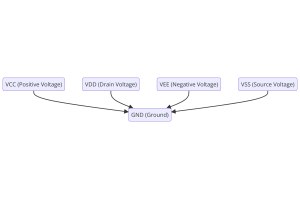

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/19 83833

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79646

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 67013

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63136

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63067

-

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54099

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52229