הבנת הארכיטקטורה והיישומים של XC2S200-5FG256I FPGA

ייתכן שאתה מחפש התקן לוגי הניתן לתכנות המאפשר לך לעצב חומרה דיגיטלית בדיוק כפי שהמערכת שלך זקוקה לה.XC2S200-5FG256I FPGA נותן לך בלוקים לוגיים גמישים, זיכרון פנימי וחיבורי קלט ופלט רבים, כך שתוכל לבנות פונקציות דיגיטליות מותאמות אישית בתוך התקן אחד.הארכיטקטורה שלו תומכת בניתוב אותות, בקרת תזמון וטיפול בממשק על פני סוגים רבים של ציוד אלקטרוני.עם ניתוב ניתנים לתכנות ומשאבי זיכרון זמינים בשבב, אתה יכול להתאים אותו למשימות בקרה שונות, נתיבי תקשורת ופונקציות מערכת משובצות מבלי לשנות את החומרה הפיזית.קטלוג

סקירה כללית של XC2S200-5FG256I

ה XC2S200-5FG256I הוא התקן לוגי הניתן לתכנות הבנוי על ארכיטקטורת Spartan II FPGA ומיועד למערכות דיגיטליות הניתנות להגדרה.הוא מספק כ-200,000 שערים לוגיים המסודרים באמצעות בלוקים לוגיים הניתנים להגדרה שניתן לתכנת ליישם פונקציות דיגיטליות מותאמות אישית.זיכרון RAM בלוק משולב תומך באחסון נתונים זמני, בעוד שמספר רב של פיני קלט ופלט מאפשרים תקשורת גמישה עם רכיבים חיצוניים.המכשיר פועל מאספקת ליבה במתח נמוך ותומך בתנאי טמפרטורה תעשייתיים.הארכיטקטורה שלו תומכת ביצירת אב טיפוס של חומרה, בקרת ממשק ומשימות עיבוד דיגיטלי בציוד אלקטרוני משובץ.

מחפש XC2S200-5FG256I?צור איתנו קשר כדי לבדוק מלאי עדכני, זמן אספקה ותמחור.

XC2S200-5FG256I ב

מבנה הקלט/פלט מחלק את היקף המכשיר לשמונה גדות הממוקמות לאורך כל ארבעת הצדדים של חבילת ה-FPGA.כל בנק מקבץ קבוצה של פיני קלט ויציאה שחולקים את אותו אספקת VCCO, מה שמאפשר להחיל רמת מתח עקבית על כל הפינים באותו אזור.כניסות שעון גלובליות שכותרתן GCLK0 עד GCLK3 ממוקמות ליד החלק התחתון והעליון של הפריסה כדי להפיץ אותות שעון באופן שווה על פני המערך הלוגי הפנימי.הסדר זה מאפשר למספר תקני איתות לפעול בו זמנית על ידי הקצאת רמות מתח שונות לבנקים נפרדים תוך שמירה על ניתוב מאורגן בין פינים חיצוניים והלוגיקה הפנימית הניתנת לתכנות.

XC2S200-5FG256I דגם CAD

סמל XC2S200-5FG256I

XC2S200-5FG256I טביעת רגל

XC2S200-5FG256I דגם תלת מימד

תכונות של XC2S200-5FG256I

ארכיטקטורת לוגיקה FPGA הניתנת לתכנות

ההתקן משתמש במבנה לוגי הניתן להגדרה המאפשר להגדיר מעגלים דיגיטליים באמצעות בלוקים לוגיים ניתנים לתכנות ונתיבי ניתוב.מבנה זה מאפשר למעצבים ליישם התנהגות חומרה מותאמת אישית מבלי לשנות את המכשיר הפיזי, תמיכה בפיתוח מערכות דיגיטליות גמישות ובאב-טיפוס לחומרה.

משאבי זיכרון בלוקים משולבים

זיכרון RAM בלוק פנימי מספק אחסון זיכרון ייעודי בתוך הבד הניתן לתכנות.בלוקי זיכרון אלה תומכים באגירת נתונים, טבלאות חיפוש ופעולות אחסון זמניות, ומפחיתים את הצורך ברכיבי זיכרון חיצוניים ביישומי עיבוד דיגיטלי רבים.

ממשק קלט ופלט ניתן להגדרה

עד 176 פיני קלט ופלט של משתמש מספקים קישוריות גמישה עם התקנים חיצוניים.ניתן להגדיר כל סיכה עבור פונקציות קלט, פלט או דו-כיווניות שונות, מה שמאפשר למכשיר ליצור אינטראקציה עם חיישנים, ממשקי תקשורת ומערכות בקרה.

רשת ניתוב ניתנת לתכנות

רשת חיבור הניתנת לתכנות מקשרת בלוקים לוגיים, רכיבי זיכרון וממשקי פלט קלט.ניתן לנתב אותות דרך נתיבים הניתנים להגדרה, המאפשרים זרימת אותות מותאמת אישית בין משאבים פנימיים תוך שמירה על התנהגות דיגיטלית צפויה.

ניהול שעון באמצעות Delay Locked Loops

מעגלי לולאה נעולה עיכוב משולבים תומכים בהפצת שעון ויישור תזמון בתוך המכשיר.מעגלים אלה עוזרים לשמור על יחסי תזמון יציבים בין קטעי לוגיקה פנימיים ומקורות שעון חיצוניים.

יכולת תפעול בטמפרטורה תעשייתית

המכשיר תומך בפעולה על פני טווח טמפרטורות מורחב המתאים לסביבות תעשייתיות.זה מאפשר ביצועים יציבים במערכות החשופות לתנאי סביבה משתנים כגון ציוד מפעל או מתקנים חיצוניים.

חבילת BGA קומפקטית משטחית

המכשיר ארוז בפורמט מערך רשת 256 כדורים המאפשר מספר גבוה של חיבורים בטביעת רגל קומפקטית.סגנון אריזה זה תומך בפריסות מעגלים מודפסים צפופים תוך שמירה על אמינות חשמלית עבור התקנים עם ספירת פינים גבוהה.

מפרט טכני של XC2S200-5FG256I

| מאפיין מוצר | ערך תכונה |

| יצרן | AMD Xilinx |

| מתח - אספקה | 2.375V ~ 2.625V |

| סך סיביות RAM | 57344 |

| חבילת מכשירי ספק | 256-FBGA (17x17) |

| סדרה | Spartan®-II |

| חבילה / מארז | 256-BGA |

| חבילה | מגש |

| טמפרטורת הפעלה | -40°C ~ 100°C (TJ) |

| מספר אלמנטים/תאים לוגיים | 5292 |

| מספר LABs/CLBs | 1176 |

| מספר קלט/פלט | 176 |

| מספר שערים | 200000 |

| סוג הרכבה | מתקן משטח |

| מספר מוצר בסיס | XC2S200 |

| סטטוס RoHs | לא תואם RoHS |

| רמת רגישות לחות (MSL) | 3 (168 שעות) |

| מצב REACH | REACH לא מושפע |

| ECCN | EAR99 |

| HTSUS | 8542.39.0001 |

תרשים בלוקים של XC2S200-5FG256I

רשת מרכזית של בלוקים לוגיים ניתנים להגדרה מהווה את מארג ההיגיון הניתן לתכנות שבו מיושמות פונקציות דיגיטליות באמצעות טבלאות חיפוש וכפכפים.עמודות אנכיות המסומנות בלוק RAM מספקות משאבי זיכרון משובצים המוצבים לצד המערך הלוגי לפעולות אחסון ואחסון נתונים.בלוקים לוגיים קלט ופלט מצפים את הקצוות החיצוניים של המכשיר ומחברים את רשת הניתוב הפנימית לפינים חיצוניים.יחידות לולאה נעולה של השהיה הממוקמות בפינות תומכות ביישור שעון ובקרת תזמון על פני המבנה הלוגי הפנימי.נתיבי חיבור בין מערך CLB, עמודות זיכרון, יחידות שעון ובלוקים I O יוצרים את רשת הניתוב הניתנת לתכנות המאפשרת חיבורי אותות גמישים בכל המכשיר.

בלוק קלט/פלט (IOB) של XC2S200-5FG256I

מבנה בלוק קלט/פלט פנימי מחבר פיני אריזה חיצוניים למארג הלוגי הניתן לתכנות באמצעות נתיבי קלט ופלט הניתנים להגדרה.נתוני פלט עוברים דרך כפכפי אצבע שכותרתו OFF עם שעון ומאפשר שליטה, ואחריו מאגר פלט הניתן לתכנות שמניע את הפין החיצוני בזמן שהוא פועל מאספקת VCCO המשויכת לבנק I O.אותות קלט מפין החבילה נכנסים דרך מאגר כניסה הניתן לתכנות ושלב השהיה אופציונלי שניתן לתכנות לפני שהם מגיעים לכפכפי כניסה שכותרתו IFF המסנכרן את האות עם השעון הפנימי.רכיבי בקרה נוספים כוללים בקרת תלת מצב דרך אוגר ה-TFF, אותות הפעלת שעון וכניסות איפוס הגדרת המנהלות את תזמון האות ובקרת המצב.רשת הגנת ESD הניתנת לתכנות שומרת על ממשק הפינים, בעוד שהפניה פנימית וחיבורי VREF תומכים בתקני I O המוזכרים במתח המשותפים על פני הבנק.

יישומים של XC2S200-5FG256I

מערכות ניתוב אותות דיגיטליות

משאבי לוגיקה ניתנים לתכנות מאפשרים למכשיר לנהל ניתוב ועיבוד אותות דיגיטליים בציוד תקשורת.בלוקי הלוגיקה הניתנים להגדרה יכולים ליישם נתיבים לוגיים מותאמים אישית המטפלים בהעברת נתונים בין רכיבי מערכת תוך שמירה על התנהגות תזמון יציבה.

יחידות בקרת אוטומציה תעשייתית

מערכות בקרה תעשייתיות דורשות לרוב לוגיקה דיגיטלית גמישה שיכולה להסתגל לתהליכי מכונה שונים.ההתקן יכול לנהל אותות בקרה, כניסות חיישנים ויציאות מפעילים, לתמוך בפעולה אמינה בסביבות ייצור אוטומטיות.

פלטפורמות אב טיפוס של חומרה משובצת

פלטפורמות פיתוח משתמשות לעתים קרובות בהתקני לוגיקה ניתנים לתכנות כדי לבדוק עיצובים דיגיטליים לפני ייצור חומרה סופי.המכשיר מאפשר למעצבים ליישם ולשנות מבנים לוגיים במהלך הפיתוח, מה שמאפשר בדיקה יעילה של פונקציות בקרה דיגיטלית.

גישור ממשק תקשורת

מערכות המחברים פרוטוקולי תקשורת מרובים יכולות להשתמש במכשיר כדי לתרגם או לנתב אותות דיגיטליים בין ממשקים.ההיגיון הניתן לתכנות מאפשר נתיבי נתונים מותאמים אישית המקשרים בין מעבדים, התקני זיכרון ובקרי תקשורת.

תתי מערכות אלקטרוניות לרכב

יחידות בקרה אלקטרוניות בכלי רכב דורשות לוגיקה ניתנת לתכנות לניהול אותות ותיאום מערכת.המכשיר יכול להתמודד עם משימות בקרה דיגיטליות, ממשקי תקשורת ופונקציות תזמון בתוך אלקטרוניקה לרכב.

לוגיקה בקרה אלקטרונית לצרכן

התקני צרכן דיגיטליים דורשים לרוב לוגיקה קומפקטית הניתנת לתכנות לניהול פונקציות המערכת.המכשיר יכול לתאם אותות ממשק משתמש, בקרת תזמון ותקשורת פנימית בין רכיבים בתוך מוצרים אלקטרוניים.

XC2S200-5FG256I יתרונות וחסרונות

יתרונות

• מבנה לוגי הניתן לתכנות מאפשר להגדיר מחדש מעגלים דיגיטליים לאחר ההתקנה

• זיכרון בלוק משולב תומך באחסון נתונים ללא זיכרון חיצוני בחלק מהעיצובים

• מספר רב של פיני קלט ופלט תומך בקישוריות גמישה למערכת

• פעולה יציבה על פני תנאי טמפרטורה תעשייתיים

• חבילת BGA קומפקטית תומכת בפריסות מעגלים מודפסים צפופים

• מעגלי יישור שעון פנימיים עוזרים לשמור על התנהגות תזמון עקבית

חסרונות

• קיבולת הלוגיקה נמוכה מזו של מכשירים ניתנים לתכנות עדכניים יותר

• גודל הזיכרון בשבב מוגבל בהשוואה למשפחות לוגיקה מודרניות הניתנות לתכנות

• צריכת החשמל יכולה להיות גבוהה יותר מארכיטקטורות מתח נמוך חדשות יותר

• אינו כולל משאבי עיבוד אותות משולבים מתקדמים

• דורש זיכרון תצורה חיצוני עבור תכנות ההתקן

חלופות XC2S200-5FG256I

| מספר חלק | יצרן | תכונות עיקריות | השתמש במקרה/הערות |

| XC2S200-5FGG256I | AMD | Spartan-II FPGA עם בלוקים לוגיים הניתנים להגדרה, זיכרון RAM מבוזר ומשאבי ניתוב ניתנים לתכנות.הוא פועל סביב אספקת ליבה של 2.5 וולט ומספק אלפי תאים לוגיים להטמעת מעגלים דיגיטליים מותאמים אישית. | משמש בעיבוד משובץ, בקרה תעשייתית וחומרה לתקשורת שבהם נדרשות לוגיקה ניתנת לתכנות ופעולה אמינה בטווחי טמפרטורות תעשייתיים. |

| XC2S200-5FGG256C | AMD | מכשיר FPGA ממשפחת Spartan-II המשלב אלמנטים לוגיים הניתנים לתכנות, בלוקי זיכרון פנימיים וחיבורי I/O הניתנים להגדרה לעיצוב דיגיטלי גמיש. | מתאים לאלקטרוניקה לצרכן, מודולי תקשורת ופלטפורמות יצירת אב טיפוס בהן נדרשת צפיפות לוגית מתונה ותצורת חומרה גמישה. |

| XC2S200-5FG256C | AMD | התקן FPGA הניתן לתכנות המציע תאים לוגיים הניתנים להגדרה, משאבי זיכרון פנימיים ומספר פיני קלט/פלט הניתנים להגדרה על ידי המשתמש למימוש מעגלים דיגיטליים מורכבים בשבב בודד. | מיושם במערכות רכישת נתונים, פלטפורמות עיבוד אותות ועיצובים משובצים הזקוקים לחומרה דיגיטלית ניתנת לתכנות. |

| XC2S200-5FGG456I | AMD | Spartan-II FPGA בעל ספירת פינים גבוהה המספק בלוקים לוגיים ניתנים לתכנות, זיכרון משובץ ומספר רב של חיבורי I/O עבור מערכות דיגיטליות מורכבות. | משמש באוטומציה תעשייתית, ציוד תקשורת מתקדם ומערכות משובצות גבוהות I/O הדורשות לוגיקה גמישה הניתנת לתכנות ותמיכה מורחבת בטמפרטורה. |

על AMD Xilinx

AMD Xilinx היא חברת טכנולוגיית מוליכים למחצה הידועה בפיתוח של התקני לוגיקה ניתנים לתכנות ופלטפורמות מחשוב אדפטיביות.החברה מקורה בשם Xilinx ומאוחר יותר הפכה לחלק מ-Advanced Micro Devices.עבודתה מתמקדת במערכי שערים ניתנים לתכנות בשטח, מערכת אדפטיבית על התקני שבבים, ופלטפורמות האצה ניתנות לתכנות המשמשות במחשוב, תקשורת, אלקטרוניקה לרכב ומערכות תעשייתיות.החברה פיתחה ארכיטקטורות לוגיות ניתנות לתכנות במשך כמה עשורים, התומכות בתכנון חומרה דיגיטלית באמצעות התקנים הניתנים להגדרה המאפשרים להגדיר מעגלים לאחר הייצור.מוצריה נמצאים בשימוש נרחב במערכות משובצות, תשתית רשת, ציוד לעיבוד אותות ומערכות בקרה אלקטרוניות.

מסקנה

XC2S200-5FG256I FPGA נותן לך דרך גמישה לבנות לוגיקה דיגיטלית ישירות בחומרה.אתה יכול להגדיר את בלוקי הלוגיקה שלו, משאבי הזיכרון וחיבורי הקלט והפלט כדי לתמוך במשימות מערכת שונות.המבנה הפנימי שלו מאפשר ניתוב אותות, בקרת תזמון ואחסון נתונים בתוך התקן יחיד שניתן לתכנות.עם הבנת הארכיטקטורה והיישומים של XC2S200-5FG256I FPGA הניתנת להגדרה, ההתקן יכול לתמוך באלקטרוניקה משובצת, ממשקי תקשורת ומערכות בקרה.הבנת הפריסה, התכונות והיישומים שלו עוזרת לך לראות כיצד התקני לוגיקה הניתנים לתכנות תומכים בציוד דיגיטלי מודרני.זה מקל עליך להעריך אם ה-XC2S200-5FG256I מתאים לצרכים של העיצוב האלקטרוני שלך.

גיליון נתונים PDF

גיליון נתונים XC2S200-5FG256I:

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. איזה סוג מכשיר הוא XC2S200-5FG256I

XC2S200-5FG256I הוא מערך שערים שניתן לתכנות בשטח.זה א התקן לוגי ניתן לתכנות המאפשר להגדיר מעגלים דיגיטליים באמצעות תוכנה ולא עיצוב חומרה קבועה.

2. כמה פיני קלט ופלט מספק XC2S200-5FG256I

התקן XC2S200-5FG256I תומך בעד 176 קלט שניתן להגדרה ופיני פלט, המאפשרים לו להתחבר לרכיבים חיצוניים רבים וממשקי תקשורת.

3. מה המטרה של בלוק RAM ב-XC2S200 FPGA

Block RAM מספק זיכרון פנימי המשמש לאחסון נתונים זמני, חציצה, טבלאות חיפוש ומשימות אחרות לטיפול בנתונים בתוך מערכת לוגית ניתנת לתכנות.

4. איפה ה-XC2S200-5FG256I נמצא בשימוש נפוץ

מכשיר זה משמש לעתים קרובות באלקטרוניקה משובצת, תקשורת מערכות, ציוד אוטומציה תעשייתי ומערכות בקרה דיגיטליות שדורשים לוגיקת חומרה ניתנת לתכנות.

5. באיזה סוג חבילה משתמש ה-XC2S200-5FG256I

ה-XC2S200-5FG256I ארוז בפורמט של מערך רשת של 256 כדורים, מה שמאפשר מספר רב של חיבורים בטביעת רגל קומפקטית מתאים לפריסות מעגלים צפופים.

הבנת מחברי DVI: כל מה שאתה צריך לדעת

ב- 2026/03/9

ADM560JRS מדריך שבב ממשק, תכונות ויישומים

ב- 2026/03/5

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/18 147760

-

Pinout USB-C ותכונות

ב- 2000/04/18 111969

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/18 111351

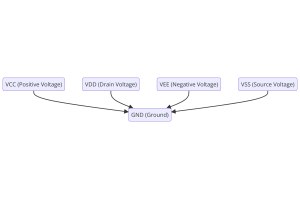

-

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/18 83733

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79520

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66930

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63082

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63024

-

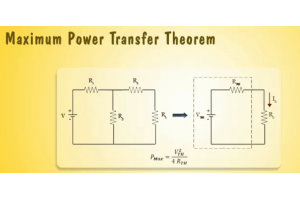

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54090

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52163