XC2S50-5TQG144I FPGA: תכונות, מפרטים, יישומים ומדריך תכנות

ה- XC2S50-5TQG144I הוא FPGA גמיש וחזק (מערך שער לתכנות שדה) ממשפחת ספרטנית II של AMD Xilinx.זה מיועד לפרויקטים דיגיטליים הזקוקים להתאמה אישית, מהירות ואמינות.מדריך זה מסביר את התכונות, המפרט, תהליך התכנות והשימושים ב- FPGA זה כדי לעזור לך להבין כיצד להפיק את המרב ממנו.קָטָלוֹג

סקירה כללית של XC2S50-5TQG1444

THE XC2S50-5TQG144I הוא FPGA Spartan-II מ- AMD Xilinx, המיועד לפרויקטים דיגיטליים הזקוקים לגמישות וביצועים.יש לו 50,000 שערי מערכת ו -1,728 תאי לוגיקה, המאפשרים לו להתמודד עם משימות מורכבות.השבב כולל 384 בלוקי לוגיקה הניתנים להגדרה (CLBS) ו- 32,768 חתיכות זיכרון RAM, ומעניקים לו זיכרון טוב וכוח עיבוד.עם 92 סיכות קלט/פלט (קלט/פלט), הוא יכול להתחבר בקלות לרכיבים אחרים.הוא מגיע בחבילה של ארבעה דק של 144 פינים (TQFP), שהוא קומפקטי ונוח לשימוש.ה- FPGA פועל על 2.5 וולט (עם טווח בטוח של 2.375 וולט עד 2.625 וולט) ועובד היטב בטמפרטורות בין -40 מעלות צלזיוס ל- +100 מעלות צלזיוס.FPGA ספרטני II זה מיוצר עם טכנולוגיית 0.18 מיקרון, מה שהופך אותו ליעיל ואמין.ניתן לתכנות, כלומר אתה יכול לעדכן את הפונקציות שלה לפי הצורך.

עבור פיתרון חסכוני, בעל ביצועים גבוהים, הצבת הזמנה בתפזורת איתנו היא הבחירה האופטימלית, ומבטיחה איכות מעולה.

דגמי XC2S50-5TQG144I CAD

XC2S50-5TQG144I סמל

XC2S50-5TQG144I טביעת רגל

XC2S50-5TQG144I דגם 3D

תכונות XC2S50-5TQG144I

• • שערי מערכת: XC2S50-5TQG144I FPGA מציע כ- 50,000 שערי מערכת.זה מאפשר לו לתמוך בעיצובים ויישומים דיגיטליים מורכבים הדורשים כמות משמעותית של יכולות עיבוד לוגיות.

• • תאי לוגיקה: מכשיר זה כולל 1,728 תאי לוגיקה, המאפשרים יישום תצורות לוגיקה מורכבות ויצירת פונקציות דיגיטליות שונות בתוך ה- FPGA.

• • חסימות לוגיקה הניתנות להגדרה (CLBS): הוא כולל 384 חסימות לוגיקה הניתנות להגדרה (CLBS), המספקות את הבסיס להיגיון ה- FPGA.ניתן לתכנת בלוקים אלה ולהגדיר מחדש כדי לעמוד בדרישות עיצוב ספציפיות, ולשפר את הרבגוניות הכוללת של המכשיר.

• • אַיִל: ה- FPGA מצויד ב -32,768 פיטים של זיכרון RAM פנימי, ומציע יכולות אחסון ושליפה יעילות של נתונים למשימות הכרוכות במניפולציה של נתונים ואחסון נתונים זמני.

• • סיכות קלט/פלט: עם 92 סיכות קלט/פלט, XC2S50-5TQG144I מבטיח קישוריות חיצונית בשפע, ומאפשר לו להתממשק עם מכשירים ורכיבים אחרים במערכת לשילוב מערכת מקיף.

• • מתח הפעלה: המכשיר פועל במתח נומינלי של 2.5 וולט, עם טווח מקובל בין 2.375V ל- 2.625V.טווח מתח זה מסייע להבטיח פעולה יציבה וביצועים אמינים בתנאים חשמליים שונים.

• • טווח טמפרטורות: XC2S50-5TQG144I נועד לפעול ביעילות בטווח טמפרטורות רחב, בין -40 מעלות צלזיוס ל +100 מעלות צלזיוס, מה שהופך אותו מתאים לפריסה בסביבות עם תנאים תרמיים מאתגרים.

XC2S50-5TQG144I תרשים בלוק

התרשים מראה כיצד אותות נעים אל תוך כדי XC2S50-5TQG144I FPGAוזה מסביר כיצד השבב מטפל באותות קלט ופלט כדי לתקשר עם רכיבים אחרים.על צד פלט , אותות מגיעים מתוך ה- FPGA ועוברים על יחידות אחסון הנקראות Flip-Flops.כפכפים אלה מחזיקים נתונים וודא שהאותות משתנים בזמן הנכון.לאחר מכן האותות עוברים דרך חיץ פלט הניתן לתכנות, המתאים עד כמה האות חזק ושולט כמה מהר הוא משתנה.יש גם מתג (בקרת OE) שמחליט אם הפלט צריך להיות פעיל או להישאר כבוי.מעגל הגנה מונע נזק מחשמל סטטי לפני שהאות יגיע לסיכות הקלט/פלט, המתחברים למכשירים אחרים.על צד קלט, אותות מבחוץ נכנסים דרך מאגר הקלט הניתן לתכנות, המעבד אותם לפני שהם שולחים אותם אל ה- FPGA.יחידת עיכוב הניתנת לתכנות מסייעת בהתאם לתזמון האות כך שהכל יישאר בסנכרון.ה- FPGA יכול להשתמש גם במתח עזר פנימי (VREF) כדי להתאים לרמות מתח שונות, מה שמקל על העבודה עם סוגים שונים של מעגלים.כמה סיכות קלט/פלט חולקות הפניה למתח זה כדי לשמור על יציבות איתותים.תכנון זה מסייע ל- FPGA לנהל אותות ביעילות, ומבטיח תזמון, הגנה ותאימות נאותים עם רכיבים אלקטרוניים שונים.

מפרט XC2S50-5TQG144I

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

AMD XILINX |

|

סִדרָה |

Spartan®-II |

|

אריזה |

מַגָשׁ |

|

סטטוס חלק |

מְיוּשָׁן |

|

מספר המעבדות/CLBs |

384 |

|

מספר אלמנטים/תאים לוגיים |

1728 |

|

סה"כ פיסות זיכרון RAM |

32,768 |

|

מספר קלט/פלט |

92 |

|

מספר השערים |

50,000 |

|

מתח - אספקה |

2.375V ~ 2.625V |

|

סוג הרכבה |

הר השטח |

|

טמפרטורת הפעלה |

-40 ° C ~ 100 ° C (TJ) |

|

חבילה / מקרה |

144-LQFP |

|

חבילת מכשירי ספק |

144-TQFP (20X20) |

|

מספר מוצר בסיס |

XC2S50 |

יישומי XC2S50-5TQG144I

מערכות משובצות

במערכות משובצות, ה- XC2S50-5TQG144I מספק את ההיגיון הדרוש ליישומים מבוססי מיקרו-בקר.הוא משמש בהרחבה באלקטרוניקה לרכב, מכשירים ניידים ורובוטיקה בקנה מידה קטן כדי לשפר את הפונקציונליות וההיענות.

עיבוד אותות

ה- FPGA מצטיין במשימות לעיבוד אותות, בהן נדרשת יכולתו לבצע עיבוד מקביל.זה אידיאלי לעיבוד שמע ווידאו, טלקומוניקציה וניתוח נתונים, ומספק לכוח הסוס לטפל באלגוריתמים מורכבים וזרמי נתונים במהירות גבוהה.

מערכות בקרה תעשייתיות

מערכות בקרה תעשייתיות נהנות מהחוסן והתכנות של FPGA זה, מה שהופך אותה מתאימה ליישומים כמו בקרת תהליכים, אוטומציה של מכונות וניטור מערכות.אמינותה מבטיחה ביצועים עקביים בסביבות הדורשות יציבות דיוקתית ויציבות תפעולית.

מערכות תקשורת

במערכות תקשורת, XC2S50-5TQG144I מסייע בניהול העברת נתונים וקליטה, תמיכה בפעילויות כמו אפנון איתות ודמודולציה, המרת פרוטוקול וניתוב רשת.יכולת ההסתגלות שלה היא המפתח בהתפתחות תשתיות טלקומוניקציה וטכנולוגיות אלחוטיות מתעוררות.

אבות -טיפוס ופיתוח

ה- FPGA משמש גם בהרחבה לאבות -טיפוס מעגלים דיגיטליים.רבים משתמשים בו כדי לבדוק ולשכלל את רעיונותיהם לפני הייצור הסופי, במיוחד בפרויקטים מורכבים של ASIC ועיצוב שבבים בהתאמה אישית.יכולת זו מקטינה את זמן הפיתוח ועלויות, ומאיצה את הדרך מהקונספט לשוק.

XC2S50-5TQG144I חלקים דומים

• • XC2S50-5TQ144I

• • XC2S50-5PQ208C

• • XC2S50-6PQ208C

יתרונות XC2S50-5TQG1444

יעילות עלות

ה- XC2S50-5TQG144I בולט בזכות הזכות שלו, ומספק יותר תכונות לדולר מאשר FPGAs רבים מתחרים.יעילות עלות זו מושגת באמצעות טכנולוגיית תהליכים מתקדמת ואדריכלות יעילה, המאפשרת פריסה רחבה יותר בשווקים רגישים בעלויות.

קלט/פלט בעל ביצועים גבוהים ואריזה

FPGA זה תומך במגוון רחב של תקני קלט/פלט וזמין באפשרויות אריזה חסכוניות שונות.תכונות אלה מבטיחות כי ניתן לשלב את המכשיר ביישומים מרובים מבלי להקריב את הביצועים, מה שהופך אותו לאידיאלי הן לשווקים מתקדמים והן למונע נפח שבהם הרבגוניות ממשק ואילוצים פיזיים הם גורמים.

תכונות ברמת מערכת

מצויד בתכונות ניהול זיכרון מתקדמות כגון זיכרון RAM מופץ ו- RAM של בלוק הניתן להגדרה, XC2S50-5TQG144I משפר את יעילות הטיפול בנתונים.תכונות אלה מאפשרות משימות אחסון ועיבוד נתונים מורכבות, מה שמגביר את הביצועים הכוללים של המערכת ואת יכולת המדרגיות של המערכת.

תכנות מחדש

התכנות מחדש של XC2S50-5TQG144I מאפשרת שינויים בלתי מוגבלים לתצורה שלו, מה שמועיל בשלב הפיתוח.גמישות זו מאפשרת לשכלל עיצובים באמצעות עדכונים איטרטיביים ללא עלויות חומרה נוספות, לטפח חדשנות ולהפחית את הזמן למוצר סופי.

XC2S50-5TQG144I שלבי תכנות

תכנות ה- XC2S50-5TQG144I FPGA מסדרת ספרטאן II של AMD XILINX כוללת סדרה מובנית של צעדים שנועדו לתרגם ביעילות עיצוב דיגיטלי לתצורת FPGA פונקציונלית.להלן מדריך משולב ומפורט שיעזור לך בתהליך התכנות:

1. כניסה לעיצוב

התחל עם שלב הזנת העיצוב, בו אתה יוצר את ההיגיון הדיגיטלי שלך באמצעות שפת תיאור חומרה (HDL), כגון VHDL או Verilog.שלב ראשוני זה כרוך בפירוט הפונקציונליות וההיגיון שברצונך ליישם ב- FPGA.נדרש שהעיצוב שלך יהיה מדויק ומייצג במדויק את הפעולות המיועדות כדי להבטיח סינתזה ויישום מוצלח.

2. סינתזה

בשלב הסינתזה, השתמש בכלי סינתזה כדי להמיר את קוד ה- HDL שלך ל- NetList.NetList הוא פירוט העיצוב שלך לפורמט הכולל אלמנטים לוגיים שונים הקשורים זה לזה כמו שערים וכפכפים.תהליך זה מתרגם את העיצוב התיאורטי שלך לתכנית מעשית שה- FPGA יכול להבין וליישם.

3. יישום

יישום כולל מספר שלבי משנה: מיפוי, מיקום וניתוב.מיפוי מקצה את האלמנטים של ה- NetList שלך לחסימות לוגיות ספציפיות בתוך ה- FPGA.מיקום קובע את המיקומים הפיזיים של בלוקים אלה בשבב ה- FPGA כדי לייעל את הביצועים וניצול המשאבים.הניתוב מחבר בין חסימות אלה דרך המשאבים הקשורים לתכנות של ה- FPGA.שלב זה מבטיח שהעיצוב עומד בכל אילוצי הפיזיים והביצועים.

4. הגדרת אילוץ

בתהליך העיצוב יש צורך בהגדרת אילוצים.אילוצים מדריכים את כלי היישום על ידי ציון דרישות כגון תזמון (כמה מהר ה- FPGA צריך לפעול), והקצאות סיכות (שמסיכות על ה- FPGA יחברו לחלקים שונים בחומרה שלך).אלה מנוסחים בקובץ אילוצי משתמשים (UCF), המסייע בכוונון עדין של העיצוב לעמוד בסטנדרטים תפעוליים ספציפיים.

5. דור זרם בים

ברגע שהעיצוב שלך עובר בהצלחה בשלב היישום, השלב הבא הוא לייצר קובץ Bittream.קובץ זה מכיל את כל נתוני התצורה הדרושים על ידי ה- FPGA כדי לבצע את העיצוב.הזרם Bitstream הוא התפוקה הסופית של תהליך התכנות, המייצג את המצב המלא והתכנתו של ה- FPGA.

6. תכנות מכשירים

השלב האחרון הוא לטעון את הזרם BitStream ל- XC2S50-5TQG144I FPGA, שניתן לבצע באמצעות מצבי תצורה שונים בהתאם להגדרתך.ב Master Mode Serial, ה- FPGA קורא באופן אוטונומי את נתוני התצורה מ- PROM סדרתי מצורף (זיכרון לקריאה בלבד לתכנות). מצב סידורי עבדים מאפשר למכשיר אב חיצוני, כגון בקר מיקרו, להאכיל את נתוני התצורה של FPGA באופן סדרתי. מצב מקביל עבדים מאפשר תכנות במהירות גבוהה על ידי אספקת נתוני תצורה במקביל ממכשיר אב חיצוני.לבסוף, מצב סריקת גבול (JTAG) משתמש בממשק JTAG הן לתכנות והן לבדיקה, מה שהופך אותו לשימושי במהלך הפיתוח לבגדים איטרטיביים ואימות.

XC2S50-5TQG144I מידות אריזה

THE XC2S50-5TQG144I הוא מערך שער לתכנות שדה (FPGA) ממשפחת ספרטנית II של Xilinx, ששוכנה ב חבילת חבילה של ארבעה דק של 144 פינים (TQFP)וחבילה זו נמדדת 20 מ"מ x 20 מ"מו

יצרן XC2S50-5TQG144I

ה- XC2S50-5TQG144I הוא FPGA ממשפחת ספרטאן II, המיוצר על ידי AMD XILINX.Xilinx, עכשיו חלק מ AMD, היא חברת מוליכים למחצה מובילה המתמחה ב- FPGAs, SOCs אדפטיביים ומכשירי לוגיקה אחרים הניתנים לתכנות.ה- XC2S50-5TQG144I פותח במקור תחת סדרת Xilinx Spartan-II, והציע 50,000 שערי מערכת ו -1,728 תאי לוגיקה, המיועדים ליישומים בעלי ביצועים גבוהים ועם זאת חסכוניים.עם הרכישה של Xilinx על ידי AMD, החברה ממשיכה לתמוך במוצרי מדור קודם כמו סדרת ספרטאן II תוך קידום ארכיטקטורות FPGA חדשות יותר.עם זאת, XC2S50-5TQG144I הוא FPGA מהדור הישן ועשוי להתמודד עם התיישנות בסופו של דבר כאשר AMD Xilinx משמרת מתמקדת למשפחות FPGA מתקדמות יותר.

מַסְקָנָה

ה- XC2S50-5TQG144I FPGA הוא שבב חסכוני וניתן לתכנות מחדש המציע ביצועים וגמישות נהדרים.הוא נמצא בשימוש נרחב במערכות משובצות, מכונות תעשייתיות ורשתות תקשורת בגלל אפשרויות העיבוד המהירות שלה ואפשרויות קישוריות חזקות.עם היכולת שלה להיות מתוכנתת ולעדכן, FPGA זה מסייע בבדיקה ופיתוח רעיונות חדשים לפני ההפקה הסופית.למרות ש- FPGAs חדשים יותר זמינים, מודל זה נותר בחירה איתנה לפרויקטים הזקוקים לפיתרון FPGA אמין ובמחיר סביר.מדריך זה מספק סקירה ברורה ופשוטה של התכונות, השימושים ותהליך התכנות של ה- FPGA, מה שהופך אותו למשאב חשוב לכולם.

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. האם אוכל להשתמש ב- XC2S50-5TQG144I ליישומים במהירות גבוהה?

ה- XC2S50-5TQG144I תומך במהירויות של עד 200 מגה הרץ, מה שהופך אותו למתאים ביותר ליישומים המוטמעים והתעשייתיים ביותר.עם זאת, אם הפרויקט שלך דורש ממשקים במהירות גבוהה כמו PCIE או זיכרון DDR, יתכן שתזדקק ל- FPGA מתקדם יותר כמו סדרת ספרטאן -6 או Artix-7.

2. כיצד XC2S50-5TQG144I משווים ל- FPGAs Spartan-3 או Spartan-6?

בעוד ש- FPGAs חדשים יותר כמו ספרטאן -3 או ספרטאן -6 מציעים ביצועים משופרים, צפיפות לוגית גבוהה יותר ותכונות נוספות, XC2S50-5TQG144I נותר בחירה מועדפת לפרויקטים רגישים בעלויות עם מורכבות בינונית.אם אתה זקוק לתאימות מדור קודם או לשרשרת אספקה יציבה, XC2S50-5TQG144I היא אפשרות נהדרת.

3. אילו כלי תכנות תואמים ל- XC2S50-5TQG144I FPGA?

ה- XC2S50-5TQG144I מתוכנת באמצעות Xilinx ISE (סביבת תוכנה משולבת).בעוד שכלי Xilinx חדשים יותר כמו Vivado אינם תומכים במשפחת Spartan-II, ISE מספקת את כל הפונקציות העיצוביות, הסינתזה והתכנות הנדרשות עבור FPGA זה.

4 האם אוכל להעביר עיצוב קיים-II קיים ל- FPGA חדש יותר?

כן, אבל זה דורש שינויים.המשפחות החדשות יותר ספרטניות -3 וספרטאן -6 משתמשות בארכיטקטורה שונה, רמות מתח ושיטות תצורה.אם אתה שוקל הגירה, אנו יכולים לסייע בבחירת אלטרנטיבות מתאימות ולמזער שינויים בעיצוב.

5. האם XC2S50-5TQG144I תומך בתכנות JTAG?

ת: כן, ה- FPGA תומך בתכנות סריקת גבול של JTAG (IEEE 1149.1), המאפשר ניפוי באגים ותצורה קלים באמצעות ממשק JTAG רגיל.זה שימושי הן לתכנות ראשונית והן לתצורה מחדש ללא זיכרון חיצוני.

XC4013XL-3PQ240C FPGA: אלטרנטיבות, מפרטים, יישומים וגיליון נתונים

ב- 2025/03/18

מגברי כוח RF: איך הם עובדים, איזה סוג יעיל יותר

ב- 2025/03/18

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/19 147783

-

Pinout USB-C ותכונות

ב- 2000/04/19 112073

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/19 111352

-

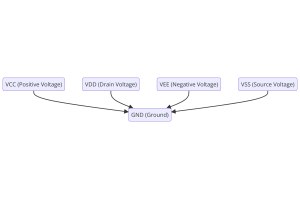

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/19 83833

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79646

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 67013

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63136

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63067

-

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54099

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52229