LFEC3E-3Q208C סקירה כללית של FPGA: תכונות, יישומים, תכנות ומפרטים

במאמר זה תלמד על LFEC3E-3Q208C, FPGA ממוליך למחצה של סריג.תוכלו לראות מה זה, את התכונות העיקריות שהיא מציעה, ומדוע זה שימושי לעיצובים רבים של אמצע טווח.התוכן גם מעביר אותך דרך המפרט, היישומים ותהליך התכנות שלב אחר שלב, יחד עם פרטי היתרונות, חסרונות ופרטי היצרן.קָטָלוֹג

מהו LFEC3E-3Q208C?

THE LFEC3E-3Q208C הוא מערך שער מתוכנת שדה חסכוני (FPGA) ממוליך למחצה סריג, שתוכנן כחלק ממשפחת Latticeec (כלכלה).משפחה זו פותחה כדי לספק פתרונות לוגיים הניתנים לתכנות המאזנים את האפשרות הזמינות עם ביצועים אמינים לעיצובים מיינסטרים.במסגרת ההיררכיה של Latticeec, היא יושבת בטווח הבינוני, ומציעה כ -3,000 אלמנטים לוגיים ושימוש ביעילות כוח, ומגשר בין הפער בין מכשירי כניסה קטנים יותר לדגמים גדולים יותר ועתירי משאבים.סדרת Latticeecp/EC רחבה יותר מדגישה תכנות בעלות נמוכה, מדרגיות וגמישות על פני גדלי מכשירים מרובים, כאשר גרסת ה- EC מתמקדת בביצועים מונעי כלכלה.

מחפש LFEC3E-3Q208C?צרו קשר כדי לבדוק את המלאי הנוכחי, זמן ההובלה והתמחור.

תכונות LFEC3E-3Q208C

• • משאבי לוגיקה

המכשיר משלב כ -3,100 אלמנטים לוגיים המאורגנים ב 384 בלוקים, ומעניק לו מספיק יכולת לעיצובים בינוניים.מאזן המשאבים הזה הופך אותו למתאים להגיון בקרה, עיבוד אותות ויישומים משובצים ללא עלות מוגזמת.

• • קלט/פלט לתכנות

עם עד 145 סיכות קלט/פלט לתכנות, הוא תומך במגוון רחב של אפשרויות קישוריות.I/OS אלה תואמים לתקנים מרובים כמו LVCMOS, LVTTL, LVDs, PCI ו- SSTL, המאפשרים שילוב מערכת גמיש.

• • זיכרון משובץ

ה- FPGA כולל זיכרון RAM ייעודי (EBR) ומשאבי זיכרון RAM מבוזרים, ומספק אחסון יעיל על השבב.זה מאפשר ליישם חיץ נתונים, טבלאות בדיקה או זיכרונות משובצים קטנים ישירות בתוך המכשיר.

• • ניהול שעון

הוא כולל עד ארבעה PLLs משולבים, ומציעים כפל תדרים, חלוקה והסרת שלב.זה מאפשר בקרת תזמון מדויקת וסנכרון עיצובים במהירות גבוהה.

• • תמיכה בזיכרון DDR

המכשיר כולל תמיכה בחומרה בממשקי DDR, המסוגלים להפעיל DDR400 (200 מגה הרץ).זה הופך את זה למעשי עבור עיצובים הדורשים גישה חיצונית במהירות גבוהה בזיכרון.

• • יעילות כוח

ה- FPGA, המופעל עם אספקת ליבה של 1.2 וולט, ממזער את צריכת החשמל הכוללת של המערכת.העיצוב הנמוך שלו הוא אידיאלי ליישומים ניידים או רגישים לאנרגיה.

• • תכונות ברמת מערכת

פונקציות מובנות כמו סריקת גבול IEEE 1149.1, ניתוח לוגיקה על שבב (ISPTRACY) וממשק פלאש SPI BOOT מפשטים את הבדיקה והבאת באגים.תכונות אלה מצמצמות את זמן הפיתוח ומשפרות את אמינות העיצוב.

• • תמיכה בפיתוח

המכשיר נתמך על ידי Suite Design Design, נהנה מסינתזה אוטומטית, מסלול מקום וכלי אימות.אתה יכול גם להשתמש בלוקי IP של iSplevercore כדי להאיץ פונקציות נפוצות ולקצר זמן לשוק.

דיאגרמת חסימת משפחתית של Latticeecp/EC

תרשים החסימה של משפחת Latticeecp/EC (כולל LFEC3E-3Q208C) מראה כיצד בנוי ה- FPGA ואיך החלקים שלו עובדים יחד.תאי הקלט/פלט הניתנים לתכנות (תמונות) ממוקמים סביב הקצוות כדי לחבר את השבב למכשירים חיצוניים, ותומכים בתקני אות רבים.בפנים, היחידות הפונקציונליות הניתנות לתכנות (PFUS) מטפלות בפעולות לוגיות, כאשר חלקן מזווגות ל- RAM בלוק משובץ (EBR) לאחסון נתונים ואחרים המתמקדים רק בהיגיון.ה- Sysclock PLLS מנהל אותות שעון כך שהעיצוב יכול לרוץ במהירות ובתזמון הנכון.יציאת Sysconfig ויציאת JTAG מאפשרים לך לתכנת, לבדוק ולבצע באגים ב- FPGA בקלות.פריסה זו מעניקה לגמישות LFEC3E-3Q208C, ביצועים אמינים ושילוב פשוט בעיצובים רגישים בעלויות.

תרשים פרוסת Latticeecp/EC

הפרוסה במשפחת Latticeecp/EC, כמו ב- LFEC3E-3Q208C, היא יחידת ההיגיון הליבה המשלבת חסימות LUT4 ונשיאה לביצוע פעולות לוגיקה וחשבון.כל פרוסה כוללת גם כפכפים/תפסים לאחסון נתונים ולאפשר היגיון רצף, כאשר מרבבים לנתב אותות באופן גמיש באמצעות רישומים או ישירות.מבנה זה חשוב מכיוון שהוא נותן את מהירות ה- FPGA, הגמישות והיעילות כדי להתמודד עם עיצובים דיגיטליים פשוטים ומורכבים כאחד.הטבלה הבאה מסכמת את תיאורי האותות של הפרוסה, כולל הפונקציות, סוגים, שמות האותות והמטרות שלהם.

|

פוּנקצִיָה |

סוּג |

שמות איתותים |

תֵאוּר |

|

קֶלֶט |

אות נתונים |

A0, B0, C0, D0 |

תשומות ל- LUT4 |

|

קֶלֶט |

אות נתונים |

A1, B1, C1, D1 |

תשומות ל- LUT4 |

|

קֶלֶט |

רַב תָכלִיתִי |

M0 |

קלט רב תכליתי |

|

קֶלֶט |

רַב תָכלִיתִי |

M1 |

קלט רב תכליתי |

|

קֶלֶט |

אות בקרה |

לִספִירַת הַנוֹצרִים |

שעון הפעל |

|

קֶלֶט |

אות בקרה |

LSR |

סט/איפוס מקומי |

|

קֶלֶט |

אות בקרה |

CLK |

שעון מערכת |

|

קֶלֶט |

אות Inter-PFU |

Fcin |

נשיאה מהירה ב- ¹ |

|

תְפוּקָה |

אותות נתונים |

F0, F1 |

אותות עקיפה של רישום פלט LUT4 |

|

תְפוּקָה |

אותות נתונים |

Q0, Q1 |

רשמו תפוקות |

|

תְפוּקָה |

אותות נתונים |

OFX0 |

פלט של lut5 mux |

|

תְפוּקָה |

אותות נתונים |

OFX1 |

פלט של LUT6, LUT7, LUT8 2 MUX תלוי בפרוסה |

|

תְפוּקָה |

אות Inter-PFU |

FCO |

לימין ביותר PFU פלט שרשרת הנשיאה המהירה ¹ |

מפרטי LFEC3E-3Q208C

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

מוליך למחצה סריג |

|

מתח - אספקה |

1.14V ~ 1.26V |

|

סה"כ פיסות זיכרון RAM |

56,320 |

|

חבילת מכשירי ספק |

208-PQFP (28x28) |

|

סִדרָה |

EC |

|

חבילה / מקרה |

208-BFQFP |

|

חֲבִילָה |

מַגָשׁ |

|

טמפרטורת הפעלה |

0 ° C ~ 85 ° C (TJ) |

|

מספר אלמנטים/תאים לוגיים |

3,100 |

|

מספר קלט/פלט |

145 |

|

סוג הרכבה |

הר השטח |

|

מספר מוצר בסיס |

LFEC3 |

יישומי LFEC3E-3Q208C

1. מערכות בקרה משובצות

LFEC3E-3Q208C מתאים היטב לבקרים משובצים במכשירים, אוטומציה תעשייתית ושערי IoT.צפיפות ההיגיון המתונה שלה ועיצוב בעלות נמוכה מאפשרים להחליף את ההיגיון בתפקוד קבוע בגמישות הניתנת לתכנות.זה מקל על שדרוג מערכות או להסתגל לתקנים מתפתחים מבלי לעצב מחדש חומרה.

2. ממשק זיכרון DDR

עם תמיכה מובנית לזיכרון DDR400, המכשיר יכול לנהל אחסון חוצץ, רישום או אחסון זמני ביישומים.תכונה זו שימושית במערכות בהן מהירות זיכרון חיצונית חשובה אך אין צורך בביצועי FPGA מתקדמים מלאים.רבים נהנים מאיזון של מהירות, עלות ויעילות זיכרון.

3. קלט/פלט גישור ופרוטוקול המרה

הודות לתמיכה הרחבה שלה בסטנדרטים של קלט/פלט כמו LVCMOS, LVTTL, LVDS, PCI ו- SSTL, ה- FPGA יעיל בגישור בין ממשקים דיגיטליים שונים.ניתן להגדיר אותו לתרגם אותות בין מערכות משנה, מה שהופך אותו ליקר בעיצובים של טכנולוגיה מעורבת.גמישות זו עוזרת להרחיב את חיי החומרה הקיימת על ידי מאפשר תאימות לרכיבים חדשים.

4. יישומי תעשייה ותשתיות

המכשיר יכול לשמש גם בציוד תעשייתי ותשתית רגיש לעלות בו מספיקים אמינות וביצועים מתונים.התמיכה שלה בסריקת גבול, ניפוי באגים על שבב ותפעול כוח נמוך הופכים אותו לאידיאלי למערכות הדורשות יעילות ותחזוקה קלה.תפקידים אופייניים כוללים יחידות בקרה, מודולי ממשק ומערכות ניטור.

LFEC3E-3Q208C חלקים דומים

|

מִפרָט |

LFEC3E-3Q208C |

LFEC3E-3Q208I |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

אלמנטים לוגיים (LUTS) |

~ 3.1K |

~ 3.1K |

~ 3.1K |

~ 3.1K |

~ 1.5K |

~ 6.1K |

|

בלוקים לוגיים |

384 |

384 |

384 |

384 |

192 |

768 |

|

איל בלוק משובץ (EBR) |

~ 55 KB |

~ 55 KB |

~ 55 KB |

~ 55 KB |

~ 18 KB |

~ 92 KB |

|

תדר הפעלה מקסימלי |

~ 340 מגה הרץ |

~ 340 מגה הרץ |

~ 340 מגה הרץ |

~ 340 מגה הרץ |

~ 300 מגהרץ |

~ 340 מגה הרץ |

|

ספירת קלט/פלט |

145 |

145 |

145 |

145 |

112 |

145 |

|

חֲבִילָה |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

|

מתח ליבה |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

|

טווח טמפרטורות |

0 ° C עד +70 מעלות צלזיוס |

–40 מעלות צלזיוס ל- +85 מעלות צלזיוס |

0 ° C עד +70 מעלות צלזיוס |

0 ° C עד +70 מעלות צלזיוס |

0 ° C עד +70 מעלות צלזיוס |

0 ° C עד +70 מעלות צלזיוס |

|

סוג תאימות / אריזה |

תֶקֶן |

תַעֲשִׂיָתִי |

ללא עופרת (QN) |

גרסה (Q) |

תֶקֶן |

תֶקֶן |

|

בַּקָשָׁה |

צפיפות אמצעית, מטרה כללי |

זהה ל- LFEC3E אך שימוש תעשייתי |

זהה ל- LFEC3E אך תואם חבילה |

אותה משפחה, הגירה קלה |

אפשרות עלות בצפיפות נמוכה |

שדרוג בצפיפות גבוהה יותר |

LFEC3E-3Q208C שלבי תכנות

לפני שתתחיל לתכנת את LFEC3E-3Q208C, חשוב להכין את הכלים הנכונים ולהבין את זרימת העיצוב לתצורת המכשירים.כל שלב בונה על הקודם, ולכן תשומת לב זהירה תבטיח תהליך תכנות חלק.

1. הכן חומרת תכנות ותוכנה

אתה מתחיל להתקין את מתכנת Diamond של Lattice או System ISPVM, שהם הכלים הרשמיים עבור FPGA זה.לאחר מכן, הגדר את כבל התכנות JTAG כמו HW-USBN-2B וודא שהנהגים מותקנים כראוי.שלב זה מבטיח שהמחשב שלך מוכן לתקשר עם מכשיר היעד ללא שגיאות חיבור.

2. יישום את העיצוב שלך בתוכנת פיתוח

בשלב הבא, צור פרויקט חדש ב- Lattice Diamond ובחר ב- LFEC3E-3Q208C כמכשיר היעד שלך.לאחר מכן אתה מוסיף את קבצי המקור של Verilog או VHDL, החל משימות סיכות ומגדיר את כל אילוצי העיתוי.לאחר סיום זה, אתה מסנתז את העיצוב, מבצע את המסלול במקום ולבסוף מייצר את הקובץ Bittream (.bit או .jed) שישמש לתכנות.

3. הגדר את הלוח והחיבורים

כעת, חבר את כבל JTAG ללוח ה- FPGA שלך, וודא כי חיבור הקרקע מאובטח לפני הצמדת קווי האות.אשר כי נגדים משיכה ומושכים נמצאים כראוי במקום, במיוחד בקווי TCK וניקוז פתוח.אם ללוח שלך יש סיכות בקרה נוספות כמו מחיקה או ispen, עליך להגדיר אותם כראוי כדי למנוע איפוסים מקריים במהלך התכנות.

4. תכנת את המכשיר

כאשר החומרה מוכנה, הפעל את כלי התכנות ובחר את הכבל המחובר שלך.טען את קובץ ה- Bittream שנוצר ובחר במצב המתאים, בדרך כלל JTAG, תלוי בהגדרה שלך.התחל את תהליך התכנות, והכלי יגדיר את התצורה של ה- FPGA תוך אימות שהנתונים נכתבו נכון.

5. אמת וניפוי באגים בתצורה

לאחר התכנות, בדוק את סיכות ה- DONT או Init בלוח שלך כדי לאשר שה- FPGA הגדיר בהצלחה.במידת הצורך, השתמש במנתח ההיגיון של iSPTRACY או בתכונות סריקת גבול כדי לבחון פונקציונליות ולאמת את התנהגות האות.אתה יכול לחזור על מחזור העיצוב והתכנות בכל פעם שנדרשים שינויים, להבטיח שהפרויקט שלך מעודן צעד אחר צעד.

LFEC3E-3Q208C יתרונות וחסרונות

יתרונות

• צריכת חשמל נמוכה, המתאימה לעיצובים רגישים לאנרגיה

• חסכוני בהשוואה ל- FPGAs יקריים גבוהים יותר

• מחזיק כלים פשוט עם עקומת למידה קלה יותר

• שדה ניתן להגדרה מחדש לעדכונים לאחר הפריסה

• חבילה קומפקטית עם איזון משאבים טוב

חסרונות

• ביצועים מוגבלים בהשוואה ל- FPGAs גדולים יותר

• היגיון היגיון וזיכרון הורד מאשר מכשירים מתקדמים

• פחות ליבות IP של צד שלישי ותמיכה במערכת האקולוגית

• מחזיק כלים חסר תכונות מתקדמות של ספקים גדולים

• לא מתאים לממשקים במהירות גבוהה במיוחד

LFEC3E-3Q208C מידות אריזה

|

סוּג |

פָּרָמֶטֶר |

|

סוג חבילה |

208-PQFP (חבילה שטוחה של ארבע פלסטיק) |

|

גודל גוף |

28 מ"מ × 28 מ"מ |

|

פְּסִיעָה |

0.5 מ"מ |

|

גובה החבילה (מקסימום) |

~ 3.4 מ"מ |

|

ספירת עופרת |

208 סיכות |

|

סגנון חבילה |

מוליכי שחף (Quad) |

|

סוג הרכבה |

הר השטח |

|

קוד מקרה |

BFQFP-208 |

|

חבילת ספקים |

מַגָשׁ |

יצרן LFEC3E-3Q208C

LFEC3E-3Q208C מיוצר על ידי תאגיד מוליכים למחצה של סריג , חברה מבוססת ארה"ב שבסיסה בהילסבורו, אורגון.Lattice, שנוסד בשנת 1983, מתמחה בפיתוח מערכי שער מתוכנת שדה נמוך בעלות עלות (FPGAs) ופתרונות קשורים.החברה מתמקדת באפשרות יישומים בשווקי תקשורת, מחשוב, אלקטרוניקה לצרכן, תעשייה ורכב.ידועה בזכות החדשנות שלה במכשירים הניתנים לתכנות חסכוניים באנרגיה, ביססה את עצמה כשחקן מפתח בתעשיית ה- FPGA, במיוחד עבור עיצובים הדורשים גורמי צורה קומפקטיים, הפחתת צריכת החשמל ואמינות גבוהה.

מַסְקָנָה

ה- LFEC3E-3Q208C מציע תערובת טובה של עלות נמוכה, שימוש בהספק נמוך, ומספיק היגיון וזיכרון לפרויקטים בינוניים.זה תומך בתקני קלט/פלט רבים, יש לו זיכרון RAM ו- PLLs מובנים ויכול לעבוד עם זיכרון DDR400, מה שהופך אותו לשימושי למשימות שליטה, ממשק ותעשייה.התכנות פשוטה עם כלי סריג, ותכונות ניפוי נוספות עוזרות בבדיקה.אמנם זה לא יכול להתאים למהירות ויכולתם של FPGAs גדולים יותר, אך זו בחירה אמינה עבור עיצובים הזקוקים לגמישות, יעילות וביצועים נוחים.

גיליון נתונים PDF

LFEC3E-3Q208C גיליונות נתונים:

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. האם LFEC3E-3Q208C תומך בממשקים במהירות גבוהה כמו PCIE או Gigabit Ethernet?

לא. LFEC3E-3Q208C מיועד ליישומים מיינסטרים ורגישים בעלויות, כך שהוא אינו כולל משדרים סדרתיים מהיר-מהיר.זה מתמקד במקום בממשקים מקבילים ותמיכה בזיכרון DDR.

2. האם ניתן לתכנת מחדש את LFEC3E-3Q208C לאחר הפריסה?

כֵּן.כ- FPGA, LFEC3E-3Q208C ניתן להגדרה מחדש לחלוטין, ומאפשר עדכונים ושינויים בעיצוב גם לאחר הפריסה.גמישות זו מפחיתה את עלויות התחזוקה לטווח הארוך ומרחיבה את מחזורי חיי המוצר.

3. כיצד LFEC3E-3Q208C מטפל באגים ובדיקות?

המכשיר משלב סריקת גבול (IEEE 1149.1), ניתוח לוגיקה על השבב (ISPTRACY) ותמיכה בפלאש SPI BOOT.כלים מובנים אלה מפשטים ניפוי באגים ומפחיתים את הצורך בחומרת בדיקה חיצונית.

4. האם LFEC3E-3Q208C יכול להרחיב את אורך החיים של מערכות חומרה ישנות?

כן, בזכות תאימות הקלט/פלט הרחבה ויכולות הגישור הפרוטוקוליות שלה, היא יכולה לממשק מערכות ישנות עם רכיבים חדשים יותר, ולסייע לעסקים להרחיב את התועלת של החומרה הקיימת.

5. אילו כלי תכנות נדרשים ל- LFEC3E-3Q208C?

הוא מתוכנת באמצעות מתכנת היהלומים של Lattice או מערכת ISPVM.כלים אלה תומכים בכניסה לעיצוב, ביצירת הזרם ובתצורת המכשירים, מה שהופך את זרימת העבודה לייעלה.

AD73311LARS: גיליון נתונים, תכונות, מדריך Pinout ותכנות

ב- 2025/08/28

EPM1270F256C4N MAX II סקירה כללית CPLD: תכונות, מפרטים ויישומים

ב- 2025/08/28

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/19 147783

-

Pinout USB-C ותכונות

ב- 2000/04/19 112073

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/19 111352

-

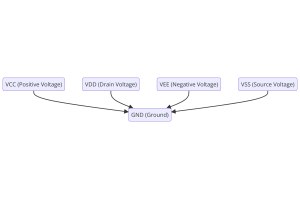

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/19 83833

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79646

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 67013

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63136

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63067

-

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54099

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52229