EPM7192SQC160-15 CPLD: תכונות, פינאוט, תכנות ויישומים

מדריך זה מדבר על ה- EPM7192SQC160-15, שבב לוגי הניתן לתכנות ממשפחת מקס 7000S.זה מסביר מה השבב יכול לעשות, איך הוא עובד ואיפה ניתן להשתמש בו.זה מראה כיצד השבב בנוי בפנים, מה כל סיכה עושה ואיך הוא מתחבר לחלקים אחרים.המדריך כולל גם היכן ניתן להשתמש בשבב זה, כיצד לתכנת אותו צעד אחר צעד, אילו שבבים דומים אחרים קיימים ומי הופך אותו.קָטָלוֹג

מהו EPM7192SQC160-15?

THE EPM7192SQC160-15 הוא CPLD בינוני (מכשיר לוגיקה מורכב לתכנות) ממשפחת מקסימום 7000S, המיועד לבקרת לוגיקה דיגיטלית אמינה במערכות משובצות ותעשייתיות.שבב זה מציע 192 תאי מקרו וכ -3,750 שערי לוגיקה, ומספק מספיק יכולת לטיפול במשימות לוגיות מתונות.זה כולל 124 סיכות קלט/פלט, ופועל באספקת 5V, עם תמיכה בקלט/פלט רב -מוולט לממשק למערכות לוגיקה של 3.3V וגם 5V.ארכיטקטורה מבוססת EEPROM הניתנת לתכנות שלה, פירושה שתוכל לתכנת אותה מחדש ישירות במעגל שלך באמצעות JTAG, מבלי שתצטרך רכיבים נוספים או זיכרון חיצוני.עם ציון מהירות של –15, הוא תומך בתדרי שעון המערכת עד בערך 76.9 מגה הרץ, ומציע ביצועי תזמון מהירים ועקביים ליישומים דיגיטליים רחבים.משפחת מקסימום 7000S ידועה בביצועים המוצקים שלה, בזיכרון ה- EEPROM ובפעולת המתח הגמיש.

מחפש EPM7192SQC160-15?צרו קשר כדי לבדוק את המלאי הנוכחי, זמן ההובלה והתמחור.

דגמי CAD של EPM7192SQC160-15

EPM7192SQC160-15 סמל

EPM7192SQC160-15 טביעת רגל

EPM7192SQC160-15 דגם 3D

תכונות EPM7192SQC160-15

192 תאי מקרו: המכשיר כולל 192 תאי מקרו, המשמשים כאלמנטים הניתנים לתכנות הליבה.ניתן להגדיר תאי מקרו אלה ליישום מגוון רחב של פונקציות לוגיות משולבות ורציפות הנדרשות בעיצובים דיגיטליים.

בערך 3,750 שערי לוגיקה: הוא מציע קיבולת לוגיקה שווה ערך של כ -3,750 שערים, מה שהופך אותה מתאימה ללוגיקה של בקרת קומפלקסיות בינונית, מכונות מדינה או היגיון דבק במערכות משובצות.

תכנות במערכת באמצעות JTAG: הוא כולל זיכרון מבוסס EEPROM המאפשר תכנות מחדש ישירות בתוך המערכת באמצעות ממשק JTAG רגיל, התומך בסטנדרטים של IEEE 1149.1 וגם IEEE 1532.

תדר מקסימלי עד 125 מגה הרץ: ההיגיון הפנימי יכול לפעול במהירויות שעון המגיעות ל 125 מגה הרץ, מה שמאפשר עיבוד מהיר ליישומים רגישים לתזמון.

עיכוב התפשטות של 7.5 ns: השבב מציע עיכוב התפשטות נמוך של כ -7.5 ננו -שניות, ומבטיח תגובת איתות מהירה מכניסה לפלט.

תומך באספקת 5V עם קלט/פלט רב -מוולט: המכשיר פועל באספקת ליבה של 5V ותומך בקלט/פלט רב-מוולט, ומאפשר תאימות לרמות האות 5V וגם 3.3 וולט לשילוב קל במערכות מתח מעורב.

קצב שבה הניתן לתכנות ויציאות ניקוז פתוח: אתה יכול לשלוט על שיעורי קצה האות להפחתת EMI ולבחור יציאות לניקוי פתוח להפעלת קווית והספקת רמה.

שישה פלט גלובלי אפשר אותות: אותות בקרה גלובליים אלה מאפשרים הפעלה או השבת תפוקות על פני בנקים/פלט מרובים לניהול אותות יעילים.

כפכפים הניתנים להגדרה במקרו-תאים: כל מקרו-תאי כולל כפכף התומך בקביעת מראש, ברור, שעון, ובקרה פרטנית, ומספק גמישות משופרת לעיצוב לוגי רצף.

מצב בעל עוצמה נמוכה: המכשיר כולל תכונה חיסכון בחשמל שיכולה לחתוך את צריכת החשמל של Macrocell ביותר מ- 50%, מה שמועיל ליישומים חסכוניים באנרגיה.

תמיכה בבדיקת סריקת גבול JTAG : מכשירים עם 128 תאי מקרו או יותר, כמו זה, כוללים תכונות בדיקת סריקת גבול מלאות לאבחון ותיקוף יעיל ברמת הלוח.

ביט אבטחה להגנת עיצוב: סיביות אבטחה ניתנת לתכנות מבטיחה שלא ניתן לקרוא או להעתיק את העיצוב הפנימי, ומגן על קניין רוחני.

קלט/פלט תואם PCI: מבנה הקלט/פלט נועד לעמוד בדרישות החשמל של PCI, המאפשר ממשק ישיר למערכות מבוססות PCI.

טווח טמפרטורת הפעלה 0 ° C עד 70 מעלות צלזיוס: טווח הטמפרטורות הסטנדרטי בדרגה מסחרית הופך את המכשיר הזה למתאים ביותר ליישומי הפנים והסביבה המקורה והביקורת.

EPM7192SQC160-15 תרשים PINOUT

תרשים זה מציג את פריסת ה- PIN עבור EPM7192SQC160-15 ומכשירי Altera Max 7000s דומים.לשבב 160 סיכות המסודרות סביב כל ארבעת הצדדים בחבילת QFP מרובעת.סיכה 1 מתחילה בפינה השמאלית העליונה והמספרים הולכים נגד כיוון השעון סביב השבב.לכל צד יש 40 סיכות.הנקודה הקטנה בסימני השמאל העליון PIN 1, המסייעת במיקום נכון.שם השבב במרכז מראה שהוא תואם לדגמים אחרים באותה משפחה.פריסה זו מספקת חיבורי קלט/פלט רבים ומועילים לעיצובים לוגיים מורכבים.

תרשים בלוק מקסימום 7000s

תרשים חסימה זה מציג את המבנה הפנימי של ה- CPLD Max 7000S, כולל EPM7192SQC160-15.השבב מחולק לארבעה קטעים עיקריים הנקראים בלוקים של מערך לוגיקה (LAB A עד D).לכל מעבדה 16 תאי מקרו, שהם יחידות לוגיקה קטנות המשמשות לבניית מעגלים דיגיטליים.יחד, מעבדות אלה מטפלות בפעולות לוגיות מורכבות.

במרכז נמצא מערך ה- Interconnect הניתן לתכנות (PIA), המחבר בין כל המעבדות ומאפשר להם לשתף נתונים.כל מעבדה שולחת ומקבלת איתותים דרך 36 ערוצים, ומעניקה ניתוב גמיש בין חסימות לוגיקה.סביב הקצוות ישנם בלוקי בקרת קלט/פלט המקשרים בין 6 ל -16 סיכות קלט/פלט לכל מעבדה, ומאפשרות למכשיר להתחבר לחלקים אחרים של מערכת.

בחלקו העליון מוצגים אותות בקרה גלובליים כמו שעונים ופלט מפלט.אותות אלה עוזרים לנהל את האופן בו נתונים נעים בתוך השבב ומתי היציאות פעילות.בסך הכל, התרשים מראה כיצד EPM7192SQC160-15 מארגן את ההיגיון והחיבורים שלו לתמיכה בעיצובים דיגיטליים מותאמים אישית.

מפרטים EPM7192SQC160-15

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

אלטרה |

|

סִדרָה |

MAX® 7000S |

|

אריזה |

מַגָשׁ |

|

סטטוס חלק |

מְיוּשָׁן |

|

סוג הניתן לתכנות |

במערכת הניתנת לתכנות |

|

זמן עיכוב TPD (1) מקסימום |

15 נ.ס. |

|

אספקת מתח - פנימית |

4.75V ~ 5.25V |

|

מספר אלמנטים/בלוקים לוגיים |

12 |

|

מספר תאי מקרו |

192 |

|

מספר השערים |

3750 |

|

מספר קלט/פלט |

124 |

|

טמפרטורת הפעלה |

0 ° C ~ 70 ° C (Ta) |

|

סוג הרכבה |

הר השטח |

|

חבילה / מקרה |

160-BQFP |

|

חבילת מכשירי ספק |

160-PQFP (28x28) |

|

מספר מוצר בסיס |

EPM7192 |

יישומי EPM7192SQC160-15

היגיון דבק מערכת משובץ

EPM7192SQC160-15 אידיאלי לגישור על מכשירים דיגיטליים שונים במערכות משובצות.ניתן להשתמש בו לניהול תקשורת בין בקרי מיקרו, שבבי זיכרון ומכשירי קלט/פלט על ידי טיפול בפענוח כתובת, בקרת אוטובוס והתאמות תזמון מבלי להזדקק ל- ICS לוגיקה נפרדת.

מכונות מדינה והגיון שליטה

עם 192 תאי המקרו שלו, השבב מתאים היטב ליישום מכונות מצב מותאמות אישית והגיון בקרה.הוא משמש בדרך כלל במשימות אוטומציה, בקרי מנוע ומערכות בקרה מבוססות תזמון הדורשות מעברי מצב אמינים וניתנים לחזרה.

ממשקי פרוטוקול תקשורת

ניתן לתכנת CPLD זה ליצור או לתרגם פרוטוקולי תקשורת כמו UART, SPI, I²C או פורמטים סדרתיים בהתאמה אישית.זה מאפשר תצורה ושינוי קלים מבלי לשנות חומרה, מה שהופך אותה ליקרה עבור ממשקי תקשורת.

עיבוד מקדים לאות דיגיטלי

הודות למהירות ההיגיון המהירה שלה ועיכוב התפשטות נמוכה, היא יכולה להתמודד עם משימות עיבוד אותות פשוטות כמו סינון, ריבוי מרבב או איתור קצה לפני שהאותות יגיעו למעבד הראשי או לשבב DSP.

תרגום לממשק והעברת רמה

יכולת הקלט/פלט הרב -מולטי שלו תומכת הן באותות 3.3 וולט והן 5V.זה הופך אותו למתאים לעיצובים הכוללים רכיבים הפועלים ברמות מתח שונות, ומאפשר תרגום מתח בטוח ויעיל.

עדכוני אבות-טיפוס מהירים ועדכוני מערכת

אתה יכול להשתמש בשבב זה במערכות שעשויות לדרוש עדכוני לוגיקה תכופים.המבנה מבוסס ה- EEPROM וממשק התכנות JTAG מאפשר לתכנת מחדש את ההיגיון גם לאחר הרכבת הלוח.

בדיקה ואבחון ברמת הלוח

עם תמיכה בסריקת גבול באמצעות JTAG, היא בודקת את החיבורים בין שבבים ב- PCB מבלי להזדקק לבדיקות.זה שימושי במהלך ייצור ואבחון בשטח לגילוי בעיות הלחמה או ניתוב.

EPM7192SQC160-15 חלקים דומים

• • EPM7192EQC160-20 (Altera)

מכשיר זה הוא מאותה סדרת MAX 7000 ומציע את אותם משאבי לוגיקה, 192 תאי מקרו ו 124 סיכות קלט/פלט בחבילת PQFP של 160 פינים.זה פועל בדרגת מהירות איטית יותר של –20, כלומר יש לו עיכובים בפריזה ארוכים יותר (~ 20 ns), אך הוא עדיין עונה על הצרכים של עיצובים שאינם קריטיים בזמן.זוהי אלטרנטיבה מתאימה ליישומים שבהם צפיפות ההיגיון חשובה, אך תזמון מהיר במיוחד אינו עדיפות, מה שהופך אותו לאידיאלי לפרויקטים רגישים לעלות שעדיין זקוקים לשוויון פונקציונלי.

• • EPM7192SQI160-10N (Altera)

חלק זה תואם גם את ההיגיון עם EPM7192SQC160-15, ומציע אותו מספר של תאי מקרו ו- I/OS.עם זאת, הוא משתמש בציון מהירות –10, התומך בפעולה מהירה יותר עם תזמון משופר (עיכוב התפשטות 10 NS).זה גם תומך בטווח טמפרטורות מורחב בין –40 מעלות צלזיוס ל- +85 מעלות צלזיוס, מה שהופך אותו לתחליף מצוין ליישומים תעשייתיים או חיצוניים.זה הופך אותו לאידיאלי כאשר נדרשים מהירות גבוהה יותר וחוסן סביבתי.

• • EPM7192SQC160-7 (אינטל)

כגרסת המהירות הישירות של EPM7192SQC160-15, גרסת –7 מספקת את הביצועים המהירים ביותר במשפחה, עם עיכובים של התפשטות עד 7.5 נ.ב.הוא שומר על אותה תצורת סיכה, מפרט כוח וצפיפות לוגיקה, ומציע החלפת ירידה למי שמחפש מהירות טובה יותר מבלי לשנות את פריסת הלוח או דרישות מתח.זה הופך אותה לבחירה הטובה ביותר עבור עיצובים קריטיים לתזמון הזקוקים לתגובה מהירה יותר של אות תוך שמירה על אותה טביעת רגל עיצובית.

EPM7192SQC160-15 שלבי תכנות

1. הזן את מצב ה- ISP

השלב הראשון הוא להעביר את המכשיר למצב של ISP (תכנות במערכת).זה נעשה דרך ממשק JTAG.לאחר מצב ה- ISP, כל סיכות הקלט/פלט במכשיר ממוקמות למצב משולש-סטייט בטוח כדי למנוע הפרעות לוגיות לא מכוונות במהלך התכנות.אתחול זה בדרך כלל לוקח כ -1 אלפיות השנייה.

2. בדוק את מזהה ההתקן

מזהה סיליקון ייחודי משובץ במכשיר כדי לאמת שהוא הדגם הנכון לפני תחילת התכנות.המערכת עוברת בהוראות קריאה ומחזרת את המזהה דרך קו TDO (נתוני בדיקה בחוץ).בדיקה זו מבטיחה כי כלי התכנות מחובר ל- CPLD הימני ונמנע מטעויות כמו להחליף חלק אחר.

3. מחיקה בתפזורת

מחיקת בתפזורת מנקה את כל הנתונים שנשמרו בעבר בזיכרון ה- EEPROM של ה- CPLD.זה מכין את השבב לקבלת תצורה חדשה.פקודת המחיקה יוזמת דופק שנמשך בדרך כלל כ 100 אלפיות השנייה, ומבטיח שכל התאים הניתנים לתכנות יתאפסו.

4. תוכנית EEPROM

נתוני תצורה חדשים נטענים במכשיר על ידי העברת כתובת וקטעי נתונים דרך יציאת JTAG.כל תא זיכרון נכתב בזה אחר זה, עם דופק תכנות המיושם לאחר כל מחזור כתיבה מוצלח.תהליך זה מגדיר את מבנה ההיגיון בו ישתמש CPLD כאשר הוא מופעל.

5. אמת את EEPROM

לאחר התכנות, המכשיר מבצע שלב אימות.זה כרוך בקריאת כל מיקום זיכרון מתוכנת והשוואת ערכי הפלט לבין הנתונים המיועדים.אם האימות נכשל, יש לחזור על התהליך.שלב זה מבטיח שהתצורה נכתבה בהצלחה.

6. צא מצב ISP

לאחר השלמת האימות, מונפקת פקודה סופית למצב יציאת ISP.המכשיר מפעיל מחדש את סיכות הקלט/פלט שלו וחידש פעולה רגילה.מעבר זה נמשך גם כאל אלפיות שנייה ומשלים את מחזור התכנות במערכת.

EPM7192SQC160-15 מידות אריזה

• • גודל גוף: 28 מ"מ × 28 מ"מ

• • גובה החבילה: 3.4 מ"מ

• • PIN PITCH: 0.65 מ"מ

יצרן EPM7192SQC160-15

ה- EPM7192SQC160-15 יוצר במקור על ידי תאגיד אלתרה, חברה הידועה במכשירי ההיגיון המתקדמים לתכנות שלה.בשנת 2015 נרכשה אלתרה על ידי חברת אינטל, והמכשיר הוא כיום חלק מקבוצת הפתרונות הניתנת לתכנות של אינטל תחת משפחת CPLD Max 7000S.אינטל ממשיכה לתמוך במוצרי Altera Legacy, אם כי ה- EPM7192SQC160-15 מסווג כעת כמיושן ברוב הקטלוגים הרשמיים.למרות מעמדה שהופסק, המוניטין ההיסטורי של אינטל לאמינות ומורשת אלתרה בפתרונות לוגיים בעלי ביצועים גבוהים מבטיחים את המשך הביקוש והזמינות באמצעות מפיצים משניים.

מַסְקָנָה

ה- EPM7192SQC160-15 הוא שבב שימושי וגמיש לטיפול במשימות בקרה דיגיטליות במערכות אלקטרוניות רבות.הוא מציע מספיק כוח לוגי למשרות כמו בניית מכונות מדינה מותאמות אישית, אותות טיפול וחיבור מכשירים שונים.הוא תומך ברמות מתח שונות, עובד במהירויות מהירות וניתן לעדכן אותו בקלות דרך JTAG.העיצוב הפנימי שלו מאפשר זרימת אות חלקה ושינויי היגיון קלים.למרות שזה הופסק כעת, זו עדיין אפשרות נהדרת לפרויקטים ישנים או מתמשכים, וניתן להחליף אותם בצ'יפס דומים המציעים תמיכה מהירה או רחבה יותר בטמפרטורה.

גיליון נתונים PDF

EPM7192SQC160-15 גיליונות נתונים:

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. האם אוכל לתכנת את EPM7192SQC160-15 מבלי להסיר אותו מלוח המעגל?

כן, השבב תומך בתכנות במערכת (ISP) דרך ממשק JTAG, כך שתוכל לתכנת אותו או לתכנת אותו מחדש ישירות בזמן שהוא מלחץ ב- PCB, שמפשט עדכוני עיצוב ומפחית את עבודת המחזור.

2. באיזו תוכנת תכנות עלי להשתמש ב- EPM7192SQC160-15?

אתה יכול להשתמש בתוכנת Quartus II של Altera (גרסאות ישנות) כדי ליצור עיצובים לוגיים, להרכיב את הקוד ולנהל את תהליך התכנות מבוסס JTAG.Quartus II תומך במכשירים מקסימליים 7000s כמו EPM7192SQC160-15.

3. האם EPM7192SQC160-15 דורש זיכרון חיצוני להפעלה?

לא, יש לו זיכרון תצורה פנימי מבוסס EEPROM.כל תצורת ההיגיון מאוחסנת בתוך השבב, ולכן אין צורך בזיכרון חיצוני לאחסון מצבי לוגיקה או רצפי אתחול.

4. מה הופך את ה- EPM7192SQC160-15 למתאים לשימוש תעשייתי?

פעולת 5V החזקה שלה, תאימות קלט/פלט רב-מוולט, עיבוד לוגיקה מהיר וזיכרון לא נדיף מבוסס EEPROM הופכים אותו לאמין למערכות תעשייתיות הדורשות פונקציות לוגיות דיגיטליות יציבות ועמידות.

5. כיצד ה- EPM7192SQC160-15 מטפל במערכות מתח מעורבות?

בזכות תמיכת ה- I/O של Multivolt, המכשיר יכול להתממשק עם רמות לוגיקה של 3.3V וגם 5V, מה שהופך אותו לאידיאלי למערכות אות מעורב וממשק לרכיבים מודרניים במתח נמוך.

מדוע לבחור ב- EPF10K100EFC484-3 לפרויקט שלך

ב- 2025/06/13

מהו מתג SPST ואיך זה עובד?

ב- 2025/06/12

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/18 147778

-

Pinout USB-C ותכונות

ב- 2000/04/18 112030

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/18 111351

-

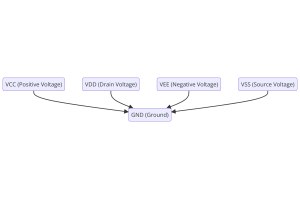

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/18 83788

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79587

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66973

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63109

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63043

-

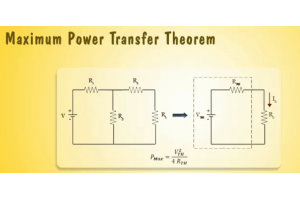

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54097

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52195