EPM7064STC100-7 CPLD: תכונות, יישומים ומדריך לתכנות במערכת

ה- EPM7064STC100-7 הוא שבב חזק מסדרת MAX® 7000S של אינטל, המיועדת לטפל במשימות מורכבות במכשירים אלקטרוניים.מדריך זה דן בתכונות והשימושים העיקריים של EPM7064STC100-7, ומדגיש את יכולתו לתכנת מחדש בקלות, את פעולתו המהירה ואת העיצוב הגמיש שלו.אידיאלי לטכנולוגיות רבות ושונות, מגאדג'טים קטנים ועד מכונות תעשייתיות גדולות, שבב זה הוא יצירה מרכזית לבניית מעגלים דיגיטליים מתקדמים.קָטָלוֹג

EPM7064STC100-7 תיאור

THE EPM7064STC100-7 הוא מכשיר לוגיקה מורכב לתכנות (CPLD) מסדרת Max® 7000S של אינטל.יש לו 64 תאי מקרו ו -1,250 שערים, המסייעים בבניית מעגלים דיגיטליים מורכבים.שבב זה פועל במהירות מקסימאלית של 166.7 מגה הרץ, עם עיכוב איתות של 7.5 ננו -שניות (NS).יש לו 68 סיכות קלט/פלט (קלט/פלט) העובדות עם היגיון 3.3 וולט ו -5 וולט, מה שמקל על השימוש במעגלים שונים.תכונת המפתח היא תכנות המערכת 5.0V במערכת (ISP) דרך ממשק JTAG (IEEE 1149.1).המשמעות היא שאתה יכול לתכנת אותו מחדש מבלי להסיר אותו מהמעגל, להקל על הבדיקה והעדכונים.הוא מגיע בחבילה שטוחה מרובעת דקה של 100 פינים (TQFP), שהיא חבילה קומפקטית ומשטח הרכבה.CPLD זה משמש במערכות משובצות, עיבוד אותות דיגיטליים, מכשירי תקשורת ואוטומציה תעשייתית.

אנו מספקים רכיבים איכותיים ושירותים בהתאמה אישית, ולכן עדיף להציב איתנו את ההזמנה בתפזורת עבור פתרונות CPLD אמינים.

תכונות EPM7064STC100-7

• • היגיון בצפיפות גבוהה: ה- EPM7064STC100-7 מעוצב עם 64 תאי מקרו ו -1,250 שערים שמישים, מה שהופך אותו למתאים ביותר ליישום פונקציות לוגיות מורכבות במעגלים דיגיטליים.ארכיטקטורה בצפיפות גבוהה זו מאפשרת ליצור עיצובים לוגיים מורכבים תוך שמירה על יעילות בפעולות לוגיות הניתנות לתכנות.מבנה המקרו-תאי המותאם היטב מבטיח ניצול יעיל של המשאבים הזמינים, תומך ביישומי לוגיקה משולבים ורצף מתקדמים.

• • ביצועים מהירים: ה- EPM7064STC100-7, שנבנה לעיבוד במהירות גבוהה, פועל עם תדר פנימי מקסימלי של 166.7 מגהרץ, ומאפשר ביצוע מהיר של פונקציות לוגיות.עיכוב ההתפשטות שלו של 7.5 NS מבטיח חביון מינימלי.יכולת מיתוג מהירה זו משפרת את יכולתו של המכשיר להתמודד עם משימות עיבוד נתונים במהירות גבוהה, מיזוג אות ובקרה ביעילות, מה שהופך אותו לבחירה אמינה עבור מערכות דיגיטליות תובעניות.

• • קלט/פלט רב -תכליתי: עם 68 סיכות קלט/פלט לתכנות, EPM7064STC100-7 מציע גמישות יוצאת דופן לשילוב בעיצובים שונים במעגלים.הוא תומך ברמות לוגיקה של 3.3V וגם 5V, הוא מאפשר תאימות חלקה עם מתחי מערכת שונים, ומבטל את הצורך במעברי רמת מתח נוספים.יכולת הסתגלות זו הופכת אותו למתאים היטב ליישומים בסביבות מתח מעורב, מה שמבטיח תחולת רחבה על פני מערכות משובצות, בקרות תעשייתיות ורשתות תקשורת.

• • תכנות במערכת (ISP): אחד היתרונות של ה- EPM7064STC100-7 הוא התכנות 5.0 וולט במערכת (ISP), הקלה באמצעות STD של IEEE.1149.1 ממשק JTAG.תכונה זו מאפשרת לתכנת מחדש ולשנות פונקציות לוגיות מבלי להסיט או להסיר את המכשיר פיזית, לפשט את התחזוקה, לניפוי באגים ופיתוח איטרטיבי.יכולת ה- ISP מפחיתה את זמן ההשבתה ומשפרת את הגמישות של עדכוני הקושחה, מה שהופך אותה לא יסולא בפז עבור עיצובים דיגיטליים דינמיים וניתנים להגדרה מחדש.

דגמי CAD של EPM7064STC100-7

EPM7064STC100-7 סמל

טביעת רגל EPM7064STC100-7

EPM7064STC100-7 דגם 3D

EPM7064STC100-7 תרשים בלוק

THE EPM7064STC100-7 תרשים בלוק מראה כיצד רכיבי ההיגיון של השבב מחוברים ונשלטים.יש לו ארבעה חסימות מערך לוגיות (מעבדות), שכותרתו A, B, C ו- D, שכל אחת מהן מכילה 16 תאים מקרו.תאי מקרו אלה מבצעים פונקציות לוגיות, והן מתחברות דרך מערך חיבור לתכנות (PIA), המאפשר ניתוב גמיש של אותות.כל מעבדה מקושרת לחסימת בקרת קלט/פלט, המטפלת עד 16 סיכות קלט/פלט למעבדה.התרשים מציג גם אותות בקרה גלובליים (GCLK1, GCLK2, OE1 ו- GCLRN) המסייעים בניהול של ענג ואיפוס פונקציות עבור השבב.כמה שערי לוגיקה מעבדים אותות אלה לפני שהם מגיעים לחלקים שונים במערכת.העיצוב של EPM7064STC100-7 מאפשר להשתמש בו ביישומי לוגיקה שונים הניתנים לתכנות, כגון מכונות מדינה, פענוח כתובות ומעגלים דיגיטליים מותאמים אישית אחרים.חיבורים הגמישים שלה מבטיחים זרימת אות יעילה ותפעול אמין.

מפרט EPM7064STC100-7

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

Altera/Intel |

|

סִדרָה |

MAX® 7000S |

|

אריזה |

מַגָשׁ |

|

סטטוס חלק |

מְיוּשָׁן |

|

סוג הניתן לתכנות |

במערכת הניתנת לתכנות |

|

זמן עיכוב TPD (1) מקסימום |

7.5 ns |

|

אספקת מתח - פנימית |

4.75V ~ 5.25V |

|

מספר אלמנטים/בלוקים לוגיים |

4 |

|

מספר תאי מקרו |

64 |

|

מספר השערים |

1250 |

|

מספר קלט/פלט |

68 |

|

טמפרטורת הפעלה |

0 ° C ~ 70 ° C (Ta) |

|

סוג הרכבה |

הר השטח |

|

חבילה / מקרה |

100-TQFP |

|

חבילת מכשירי ספק |

100-TQFP (14X14) |

|

מספר מוצר בסיס |

EPM7064 |

EPM7064STC100-7 תכנות במערכת (ISP)

EPM7064STC100-7, חלק ממשפחת CPLD MAX 7000S, עוקב אחר רצף תכנות במערכת שישה שלבים (ISP) כדי להבטיח תצורה נכונה.תהליך זה מאפשר לך לתכנת את המכשיר מבלי להסיר אותו מלוח המעגל.תהליך ה- ISP כולל העברת הוראות, כתובות ונתונים באמצעות ה- TDI (בדיקת נתוני IN) PIN תוך אחזור התגובות באמצעות PIN TDO (נתוני בדיקה).

השלב הראשון, הזן את ה- ISP, מבטיח כי סיכות קלט/פלט עוברות בצורה חלקה ממצב משתמש למצב ISP ודורש כ- 1MS.אחרי זה מגיע בדוק מזהה, שם נקרא מזהה הסיליקון של המכשיר כדי לאשר את היעד הנכון.בשלב הבא, מחיקה בתפזורת משמרות שלב בהוראות מחיקה ומיישמות דופק מחיקה של 100 מ"מ, ומנקה את כל הנתונים הקיימים בתאי EEPROM.THE תָכְנִית להלן שלב, כאשר כתובות ונתונים מועברים ברצף למכשיר, ומיישמים פעימות תכנות כדי להגדיר את תאי ה- EEPROM.יש לתכנת כל כתובת באופן פרטני, מה שהופך את הצעד הזה לזמן זמן בהתאם למספר תאי ה- EEPROM במכשיר.

לאחר השלמת התכנות, לְאַמֵת השלב מבטיח כי הנתונים אוחסנו כראוי.כאן, פולסים קריאים מיושמים על תאי EEPROM, והנתונים שאוחזרו משווים לערכים הצפויים.אם יימצאו אי התאמות, יתכן שיהיה צורך בתכנות מחדש.לבסוף, יציאה מהספק שלב מבטיח כי סיכות קלט/פלט עוברות בחזרה למצב משתמש, הדורשת 1MS נוספים.זמן התכנות או האימות הכולל מושפע משני גורמים עיקריים: זמן הדופק, הנדרש למחיקת EEPROM, תכנות וקריאה פעולות וזמן הסטה, התלוי בתדר TCK (שעון הבדיקה) ובמספר המחזורים הדרושים להעברת הוראות, כתובות ונתונים.מכיוון שלמכשירים שונים בעלי יכולת IPS יש מספרים משתנים של תאי EEPROM, זמנים קבועים וגם משתנים הם ייחודיים לכל מכשיר.ניתן לחשב את זמן ה- ISP הכולל כפונקציה של תדר TCK, מספר מכשירי היעד ואדריכלות ה- EEPROM.

יישומי EPM7064STC100-7

מערכות משובצות

ה- EPM7064STC100-7 נמצא בשימוש נרחב ביישומי מערכת משובצים, שם הוא משמש כפתרון לוגי הניתן לתכנות גמיש לבקרת ציוד היקפי שונים, אותות עיבוד ויישום פרוטוקולים מותאמים אישית.היכולת שלה להתממשק למיקרו -בקרים וחיישנים מאפשרת לייעל את ביצועי המערכת תוך שמירה על טביעת רגל קומפקטית.עם פעולתה המהירה וצריכת החשמל הנמוכה, זו בחירה מצוינת ליישומים משובצים הדורשים אמינות ויעילות.

עיבוד אותות דיגיטלי (DSP)

בעיבוד אותות דיגיטליים, EPM7064STC100-7 ממלאת תפקיד ביישום מסננים, אפנון איתות ופונקציות מתמטיות שונות.מהירויות המיתוג המהירות שלה ועיכוב התפשטות נמוכה הופכים אותו מתאים לטיפול במשימות עיבוד נתונים בתדר גבוה, מה שמבטיח חביון מינימלי בהמרת האות ובמניפולציה.הוא משמש בדרך כלל בעיבוד שמע, טלקומוניקציה ומערכות מכ"ם.

תקשורת נתונים

ה- EPM7064STC100-7 משמש בהרחבה במערכות רשת ותקשורת נתונים בשל יכולתו להתמודד עם פעולות עתירות לוגיות כמו ניתוב נתונים, חיץ ותיקון שגיאות.יכולות הקלט/פלט הניתנות לתכנות שלה מאפשרות לו להסתגל לפרוטוקולי תקשורת שונים, מה שהופך אותו לרכיב חשוב במתגי אתרנט, נתבים ותשתיות טלקומוניקציה.התמיכה שלה בתכנות במערכת (ISP) מאפשרת גם עדכוני שדה, ולשפר את יכולת ההסתגלות בסביבות רשת דינמיות.

אוטומציה תעשייתית

יישומים תעשייתיים דורשים אמינות גבוהה, עמידות וצריכת חשמל נמוכה, מה שהופך את EPM7064STC100-7 לבחירה מועדפת עבור בקרי לוגיקה לתכנות (PLCS), מערכות בקרת מנוע וציוד בדיקה אוטומטי.עם תכנות המערכת המבוססת על JTAG, הוא מספק את היכולת לחדד תהליכי אוטומציה מבלי לדרוש הסרה פיזית או עיצוב מחדש.הרבגוניות שלה בתאימות מתח גם הופכת אותו למתחיל להתממשק למגוון רחב של חיישנים ומפעילים המשמשים במסגרות תעשייתיות.

EPM7064STC100-7 חלקים דומים

• • EPM7064STC44-10N

• • EPM7064STC100-6

• • EPM7064STC100-10

יתרונות EPM7064STC100-7

תכנות במערכת (ISP)

אחד היתרונות הגדולים ביותר של ה- EPM7064STC100-7 הוא יכולתו לתכנת מחדש תוך כדי רכיבה במערכת.זה מבטל את הצורך בהסרת השבב לעדכונים, הפחתת זמן התחזוקה ושיפור היעילות.אתה יכול ליישם שינויים בעיצוב מבלי להפריע לייצור, ולהפוך אותו לפיתרון חסכוני לפרויקטים לטווח הארוך.

ביצועים במהירות גבוהה

המכשיר תומך בתדר הפעלה פנימי גבוה של עד 166.7 מגה הרץ, ומאפשר זמני עיבוד נתונים וזמני תגובה מהירים.זה הופך אותו לאידיאלי ליישומים הדורשים עיבוד אותות, בקרת לוגיקה וממשק במהירות גבוהה, מה שמבטיח פעולת מערכת חלקה ואמינה יותר.

תמיכה בקלט/פלט רב -תכליתי

עם עד 68 סיכות קלט/פלט הניתנות להגדרה ותאימות לרמות מתח מרובות (3.3 וולט, 5V ואפשרויות סובלניות עבור 2.5V, 3.3V ו- 5V), EPM7064STC100-7 מציע גמישות בעיצוב המערכת.זה מאפשר שילוב חלק במעגלים שונים ותומך בסביבות מתח מעורב, ומפחית את בעיות התאימות עם רכיבים אחרים.

פעולה אמינה בסביבות

ה- EPM7064STC100-7, שנועד לתפקד בטמפרטורות של 0 ° C עד 70 מעלות צלזיוס, מבטיח פעולה עקבית ויציבה במגוון תנאים.אמינות זו הופכת אותה לבחירה מועדפת ליישומים בהם נדרשת יציבות סביבתית, כמו אוטומציה תעשייתית, טלקומוניקציה ומערכות בקרה משובצות.

EPM7064STC100-7 תרשים PIN-OUT של חבילה

ה- EPM7064STC100-7 הוא CPLD (מכשיר לוגיקה מורכב לתכנות) מסדרת Max 7000S של Altera, ששוכנה בחבילה שטוחה מרובעת דקה של 100 פינים (TQFP-100).סוג חבילה זה מיועד ליישומי הר-השטח, ומציע איזון של צפיפות סיכה גבוהה וגודל קומפקטי.THE תרשים הצמד עוקב אחר ערכת מספור נגד כיוון השעון, עם סיכה 1 ממוקמת בפינה השמאלית העליונה של החבילה.נעים נגד כיוון השעון, 25 הסיכות הראשונות תופסות את הצד השמאלי, סיכות 26 עד 50 ממוקמות לאורך הקצה התחתון, סיכות 51 עד 75 ממשיכות לאורך הצד הימני, והסיכות 76 עד 100 מופצות לאורך הקצה העליון.THE חבילת TQFP-100 כולל לידים דקים המשתרעים כלפי חוץ מכל ארבעת צידי הגוף השטוח והמרובע.תכנון זה משפר את תאימות הרכבה על פני השטח תוך שמירה על מרווח סיכות הולם להלחמה והרכבה קלים.המגרש העופרת (המרחק בין סיכות סמוכות) הוא בדרך כלל 0.5 מ"מ, ומיטב מיטוב שלמות האות תוך צמצום טביעת הרגל הכוללת.

יצרן EPM7064STC100-7

ה- EPM7064STC100-7 הוא CPLD (מכשיר לוגיקה מורכב לתכנות) שפותח במקור על ידי Altera, חברת מוליכים למחצה הידועה בפתרונות ההיגיון הניתנים לתכנות שלה.בשנת 2015, אינטל Altera רכשה, שילבה את קווי המוצרים של FPGA ו- CPLD בקבוצת הפתרונות הניתנים לתכנות של אינטל (PSG).מאז, ה- EPM7064STC100-7 היה ממותג תחת אינטל, אם כי הוא סומן כמיושן.אינטל, כיצרנית, שמרה על תמיכה מדור קודם עבור CPLDs של סדרת MAX® 7000S, כולל מודל זה, תוך העברת בהדרגה את המיקוד שלה לעבר FPGA מודרני וטכנולוגיות לוגיות הניתנות לתכנות.

מַסְקָנָה

ה- EPM7064STC100-7 מפגיש פונקציות מורכבות, ביצועים מהירים ועדכונים קלים בשבב אחד, ומוכיח את ערכו במערכים דיגיטליים מאתגרים.מדריך זה הראה כיצד הוא עובד, למה הוא משמש וכיצד הוא מתאים למערכות אלקטרוניות שונות.זה עוזר לגרום למכשירים לפעול בצורה חלקה ויעילה, ולהוכיח שהוא עדיין שימושי מאוד ליישומים רבים.מדריך זה מספק תצוגה ברורה כיצד EPM7064STC100-7 יכול לעזור בשיפור יעילות של עיצובים אלקטרוניים ופעולות מערכת.

גיליון נתונים PDF

EPM7064STC100-7 גיליונות נתונים:

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. כיצד עיכוב התפשטות 7.5NS של EPM7064STC100-7 משפיע על ביצועי מעגל?

עיכוב התפשטות של 7.5NS מבטיח עיבוד אותות נמוכה לאחצן, מה שהופך את ה- CPLD הזה המתאים ליישומים במהירות גבוהה כמו עיבוד אותות דיגיטליים (DSP), מערכות תקשורת ואוטומציה תעשייתית הדורשים בקרת תזמון מדויקת.

2. האם ניתן לתכנת את EPM7064STC100-7 באמצעות כלי פיתוח מודרניים?

כן, ניתן לתכנת אותו באמצעות תוכנת Quartus II של אינטל (לשעבר Altera Quartus) יחד עם מתכנת JTAG מתאים.עם זאת, תמיכה ב- CPLDs ישנים יותר כמו EPM7064STC100-7 עשויה להיות מוגבלת בגרסאות קווארטוס חדשות יותר, כך שתצטרך להשתמש בגרסאות מדור קודם כמו Quartus II 13.0 SP1, התומכות עדיין במכשירים של סדרת Max® 7000.

3. האם EPM7064STC100-7 תומכים בסביבות מתח מעורב?

כן, הוא תומך ברמות לוגיקה של 3.3 וולט וגם 5V, מה שהופך אותו לתואם למגוון רחב של מעגלים דיגיטליים.גמישות זו שימושית לממשק רכיבי 5V מדורגיים עם מערכות 3.3 וולט מודרניות ללא מעגלים נוספים לשינוי ברמה.

4. מהי השיטה הטובה ביותר לפתרון בעיות עיצוב מבוסס EPM7064STC100-7?

כדי לפתור בעיות, באפשרותך להשתמש במנתח לוגיקה של Quartus SignalTap II או באוסצילוסקופים חיצוניים ומנתחי לוגיקה כדי לפקח על האותות.אם ניפוי נושאי תכנות JTAG, וודא כי חיבורי TDI, TDO, TCK ו- TMS נכונים וכי אתה משתמש במתכנת USB תואם או מתכנת ByteBlasterMV.

5. האם אוכל לתכנת את EPM7064STC100-7 מבלי להסיר אותו מלוח המעגלים שלי?

כֵּן.תכנות המערכת 5.0V במערכת (ISP) באמצעות JTAG (IEEE 1149.1) מאפשרת לך לתכנת מחדש את המכשיר בזמן שהוא נשאר במערכת.זה הופך עדכוני קושחה, ניפוי באגים ובדיקה יעילה בהרבה בהשוואה ל- CPLDs המסורתיים.

מדריך מלא לנגד 10K: קוד צבע, יישומים ושימושים במעגל

ב- 2025/03/10

קבלים לעומת סוללות: מה המתאים ביותר לצורכי האנרגיה שלך?

ב- 2025/03/7

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/19 147781

-

Pinout USB-C ותכונות

ב- 2000/04/19 112052

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/19 111352

-

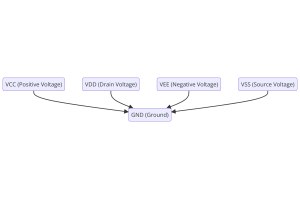

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/19 83807

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79613

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66992

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63117

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63051

-

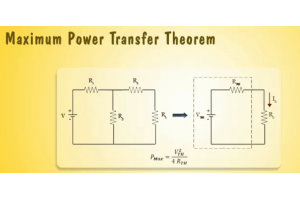

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54097

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52202