EPF8820ARC208-4 מדריך FPGA: תכונות, ארכיטקטורה, יישומים ותכנות

מאמר זה עוסק ב- EPF8820ARC208-4, שבב מיוחד המשמש באלקטרוניקה.זה מסביר מה השבב עושה, איך הוא עובד ואיפה ניתן להשתמש בו.תוכלו ללמוד על החלקים שלה, כיצד להגדיר את זה ולמה עדיין להשתמש בו היום בדברים כמו מכשירי רדיו, מכונות, מכוניות ועוד.זה גם מראה כיצד זה משתווה לשבבים דומים אחרים.קָטָלוֹג

מהו EPF8820ARC208-4?

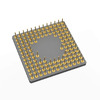

THE EPF8820ARC208-4 הוא מכשיר FPGA מדור קודם מסדרת Flex 8000 שפותחה על ידי Altera, כיום תחת קבוצת Solutions Programily Solutions.הוא תוכנן באמצעות ארכיטקטורה מבוססת CMOS SRAM, והוא שייך למשפחה של מכשירי לוגיקה הניתנים להגדרה מחדש שסימנו שלב בפיתוח לוגי הניתן לתכנות.סדרת Flex 8000 הוכרה בזכות מבנה תאי ההיגיון המגוונים שלה ובחיבור ההבדל הניתן להרחבה, המתאימה לשילוב דיגיטלי לשימוש כללי.ה- EPF8820ARC208-4 נופל באופן ספציפי לגרסת ציון בינונית בסדרה זו, ויכולות חיבור.היא חולקת את הארכיטקטורה שלה עם גרסאות אחרות בדרגה מהירות כמו –2, –3 ו- -5, שונות בעיקר בביצועי התזמון.

מחפש EPF8820ARC208-4?צרו קשר כדי לבדוק את המלאי הנוכחי, זמן ההובלה והתמחור.

EPF8820ARC208-4 תכונות

• • ארכיטקטורת Flex 8000

ה- EPF8820ARC208-4 בנוי על ארכיטקטורת Flex 8000 של Altera, המשתמשת בתצורה מבוססת SRAM לתכנות במערכת.הוא מספק פיתרון חסכוני וגמיש ליישומי צפיפות לוגיקה בינוני.

• • צפיפות היגיון

מכשיר זה משלב 672 אלמנטים לוגיים, ומספק כ 8,000 שערי מערכת שמישים.הוא מציע איזון מתאים בין מורכבות לביצועים לבקרה משובצת, היגיון דבק ועיצובים של מכונות מדינה.

• • ליבת 5V עם תמיכה בקלט/פלט של Multivolt ™

המכשיר פועל באספקת 5V, תומך גם בתקני קלט/פלט של 3.3 וולט ו -5 וולט באמצעות טכנולוגיית קלט/פלט Multivolt ™.זה הופך אותו להתאמה למערכות מתח מעורב וממשק מדור קודם.

• • תצורה ניתנת לתכנות מחדש במעגל

ה- EPF8820ARC208-4 מבוסס SRAM ותומך בתצורת מעגל באמצעות PROMs סידורי או מקבילים חיצוניים.זה מאפשר עדכוני עיצוב מהיר ותצורה מחדש מבלי להסיר את המכשיר מהמעגל.

• • ניתוב חיבורי FastTrack

מבנה הקשרים המהיר שלו מהיר מספק בד ניתוב מהיר צפוי.ארכיטקטורה זו תומכת בבקרת מיקום לוגיקה ובקרת תזמון יעילה, ומאפשרת ביצועי עיצוב יעילים.

• • נשיאות ומפלס לשרשראות לאריתמטיקה

שרשראות נשיאה ומפל ייעודיות משפרות את יישום הפונקציות האריתמטיות כמו תוספות ודלפקים.תכונות אלה מצמצמות את עיכוב ההיגיון ומפשטות את בניית פעולות המתמטיקה המורכבות.

• • תאימות לאוטובוס PCI (Rev 2.2)

מכשיר זה עומד במפרט האוטובוסים המקומי של PCI עדכון 2.2, מה שהופך אותו מתאים לשימוש במערכות מבוססות PCI.הוא תומך בסביבות איתות PCI סובלניות 5V.

• • תמיכה בסריקת גבול JTAG

ה- EPF8820ARC208-4 כולל יכולות סריקת גבול מובנות IEEE 1149.1 (JTAG).זה מאפשר ניפוי באגים, בדיקת דירקטוריון ואימות במערכת מבלי לדרוש מעגלים נוספים.

• • בקרת קצב של SLEW הניתנת לתכנות

מנהלי ההתקן הפלטים שלה כוללים בקרת קצב של SLEW הניתנת לתכנות, ועוזרים למזער את הרעש מיתוג.זה מועיל בעיצובים במהירות גבוהה לשלמות האות.

• • מצב המתנה בעל עוצמה נמוכה

המכשיר מיועד ליעילות חשמל, צורך פחות מ- 0.5mA במצב המתנה.זה מאפשר למערכות לחסוך כוח בתקופות סרק או לא פעילות.

• • טמפרטורת הפעלה: 0 ° C עד 70 מעלות צלזיוס

הרכיב פועל באופן אמין בטווח טמפרטורות מסחרי של 0 מעלות צלזיוס עד 70 מעלות צלזיוס.זה אידיאלי לשימוש לשימוש כללי בסביבות מבוקרות.

תרשים חסימה של Flex 8000

התרשים ממחיש את המבנה הפנימי וכיצד ה- FPGA מעבד היגיון וחיבורים.במרכז נמצאים בלוקי מערך ההיגיון (מעבדות), המכילים אלמנטים לוגיים מרובים (LES).LES אלה ניתנים לתכנות וניתן להגדיר אותם לביצוע מגוון רחב של משימות לוגיות, התומכות הן בעיצובים משולבים והן ברצף.גמישות זו מאפשרת יישום מעגל דיגיטלי מותאם אישית.

סביב המעבדות נמצאים אלמנטים של קלט/פלט (IOE), המטפלים בתקשורת בין ה- FPGA למכשירים חיצוניים.הם תומכים באותות קלט, פלט ובדו כיווני תוך התאמת רמות מתח שונות.חיבור כל החלקים הוא ה- FastTrack Interconnect, מערכת ניתוב במהירות גבוהה המקשרת בין מעבדות ו- IOEs ביעילות.הגדרה זו מבטיחה העברת נתונים מהירה, ניתוב אותות חלקים וביצועים אמינים על פני יישומים שונים בסדרת Flex 8000.

מצב תזמון של Flex 8000

התרשים מדגיש כיצד עיכובים משפיעים על עיבוד ההיגיון ועל זרימת האות בתוך ה- FPGA.בתוך כל אלמנט לוגי (LE), גורמי תזמון כמו עיכוב טבלת בדיקה (LUT), עיכוב שרשרת וזמני ההתקנה/החזקת הרשמה קובעים כמה מהר פעולות ההיגיון מגיבות לשינויי קלט.עיכובים פנימיים אלה חשובים לשמירה על פעולה מדויקת ויציבה, במיוחד במעגלי מיתוג מהיר.

עבור פעולות קלט/פלט, מצב העיתוי מראה כיצד האותות מתנהגים כאשר הם נכנסים ויוצאים מ- FPGA.נקודות המפתח כוללות עיכוב פלט, כמו גם הגדרת קלט וזמני החזקה, המגדירים כמה זמן צריך להיות יציב לאותות חיצוניים לכידת נתונים נכונה.התרשים מתאר גם עיכובים בין LES מחוברים, כולל נתיבי נשיאה ומפל, המשפיעים על זרימת ההיגיון על פני המכשיר.בסך הכל, אלמנטים תזמון אלה מבטיחים ביצועים מסונכרנים ואמינים ברחבי הארכיטקטורה של Flex 8000.

פלקס 8000 פעולת שרשרת נשיאה

פעולת שרשרת הנשיאה ב- EPF8820ARC208-4 FLEX 8000 נועדה לבצע חישובים אריתמטיים מהירים על ידי קישור אלמנטים לוגיים מרובים (LES) יחד.כל LE מכיל טבלת בדיקה (LUT), מעגל לוגיקה נשיאה ופנקס.התהליך מתחיל עם אות העברה שנכנס ל- LE (LE1) הראשון, אשר יחד עם תשומות A1 ו- B1 מייצר פלט סכום (S1) ואות נשיאה.

לאחר מכן מועבר אות נשיאה זה ישירות ל- LE הבא בשרשרת (LE2, LE3 וכן הלאה), ומאפשר לכל LE לחשב את תפוקת הסכום שלו (S2 ל- SN) באמצעות תשומותיו ואת הנשיאה הנכנסת.ה- LE האחרון ברצף מייצר את האות הסופי של העבירה, ומשלים את הפעולה.מבנה שרשרת נשיאה זה מאפשר תוספת מהירה ויעילה, אידיאלית לבניית תוספות, דלפקים והגיון מבוסס חשבון אחר בארכיטקטורת Flex 8000.

מפרט EPF8820ARC208-4

|

סוּג |

פָּרָמֶטֶר |

|

יַצרָן |

Altera/Intel |

|

סִדרָה |

Flex 8000 |

|

אריזה |

מַגָשׁ |

|

סטטוס חלק |

מְיוּשָׁן |

|

מספר המעבדות/CLBs |

84 |

|

מספר אלמנטים/תאים לוגיים |

672 |

|

מספר קלט/פלט |

152 |

|

מספר השערים |

8000 |

|

מתח - אספקה |

4.75V ~ 5.25V |

|

סוג הרכבה |

הר השטח |

|

טמפרטורת הפעלה |

0 ° C ~ 70 ° C (Ta) |

|

חבילה / מקרה |

208-BFQFP PAD חשוף |

|

חבילת מכשירי ספק |

208-RQFP (28x28) |

יישומי EPF8820ARC208-4

1. עיבוד אותות דיגיטלי (DSP) ובקרת מסלול נתונים

ה- EPF8820ARC208-4 מתאים היטב ליישום פונקציות DSP בהתאמה אישית בגלל צפיפות ההיגיון המתונה שלו ואדריכלות הניתוב היעילה שלו.זה יכול לטפל במניפולציה של מסלול נתונים לפעולות כמו סינון, אפנון ושינוי של אותות דיגיטליים במהירות גבוהה.

2. ממשק אוטובוס מותאם אישית ועומס מעבד

עם מספרם הגדול של סיכות קלט/פלט ותמיכה ™ Multivolt ™, FPGA זה משמש לרוב לעיצוב ממשקים היקפיים בהתאמה אישית או רמות לוגיקה לא תואמות.זה משמש גם מעבד משותף שמוריד משימות שליטה חוזרת או טיפול בטיפול במעבד הראשי.

3. עיבוד רדיו ותקשורת מוגדר תוכנה

הגמישות והיכולת של המכשיר לתכנת מחדש הופכים אותו לאידיאלי עבור יישומים כמו רדיו מוגדר תוכנה (SDR), כאשר תוכניות אפנון או פרוטוקולים עשויים להשתנות.זה יכול להתמודד באופן דינמי בקידוד, פענוח וניהול איתותים על פני שכבות תקשורת.

4. אבות -טיפוס של ASIC וחיקוי חומרה

בדרך כלל משתמשים ב- EPF8820ARC208-4 בשלב האבות-טיפוס של התפתחות ASIC.הארכיטקטורה הניתנת לתכנות מחדש מאפשרת אימות מהיר, בדיקה וסימולציה של תזמון של עיצובים דיגיטליים מורכבים לפני שהיא מתחייבת לסיליקון.

5. מנועי זיהוי קולי והצפנה

FPGA זה מסוגל ליישם היגיון מורכב בינוני כמו צינורות זיהוי קולי ואלגוריתמים קריפטוגרפיים.נוכחות של שרשראות נשיאה ו- I/OS רשום מבטיחה חישוב מהיר ועיבוד אותות נמוכה של אורגיות הנדרשים ליישומים כאלה.

6. מערכות בקרה ומכשור תעשייתי

העיתוי הצפוי, הפקדים הסינכרוניים הגדולים של מעריצים, ובלוקי ההיגיון הגמישים הופכים את ה- FPGA הזה למערכות אוטומציה תעשייתיות.לעתים קרובות הוא משמש בתזמון הניתן לתכנות, בקרת מכונות מדינה ומעגלי מיזוג אותות.

7. מערכות משובצות חלל והגנה

מכשיר זה משמש באלקטרוניקה והחיסור והגנה בהן יש צורך בגמישות תצורה ופעולה אמינה בסביבות מבוקרות.הוא תומך בעומס קושחה מאובטח ומציע כוח המתנה נמוך, המועיל ליישומים קריטיים למשימה.

8. מודולים אלקטרוניים לרכב

באלקטרוניקה של רכב ניתן למצוא את ה- EPF8820ARC208-4 במודולי בקרה המטפלים בתרגום לוגיקה, אבחון או צבירת נתונים בין חיישנים ל- ECUs מרכזי.אופיו הניתן להגדרה מחדש מאפשר עדכונים ושיפורים גם לאחר הפריסה.

9. מיתוג טלקומוניקציה וטיפול בפרוטוקול

ב- Telecom Systems, FPGA זה תומך במיתוג לוגיקה, טיפול בפרוטוקול וניהול תזמון.זה יכול להסתגל לתקני איתות שונים, ולהבטיח תאימות ושדרוג ברשתות תקשורת דינאמיות.

EPF8820ARC208-4 חלקים דומים

להלן טבלת השוואה של EPF8820ARC208-4 והחלקים הדומים הרלוונטיים ביותר שלה מאותה משפחת Flex8000:

|

מספר חלק |

ציון מהירות |

סוג חבילה |

סיכות קלט/פלט |

אלמנטים לוגיים |

ציון טמפרטורה |

|

EPF8820ARC208-4 |

–4 (קו בסיס) |

208 פינים QFP |

152 |

672 |

מִסְחָרִי |

|

EPF8820ARC208-2 |

–2 (איטי יותר) |

208 פינים QFP |

152 |

672 |

מסחרי (0–70 מעלות צלזיוס) |

|

EPF8820ARC208-3 |

–3 (בינוני) |

208 פינים QFP |

152 |

672 |

מִסְחָרִי |

|

EPF8820ARC208-5 |

–5 (מהיר יותר) |

208 פינים QFP |

152 |

672 |

מִסְחָרִי |

|

EPF8820AQC208-4 |

–4 |

208 פינים QFP (AQC) |

152 |

672 |

מִסְחָרִי |

|

EPF8820ARI208-4H |

–4 |

208 פינים QFP |

152 |

672 |

תעשייתי (–40–85 מעלות צלזיוס) |

EPF8820ARC208-4 שלבי תכנות

1. צור קובץ תצורה

התחל על ידי יצירת קובץ התצורה באמצעות תוכנת הפיתוח של Altera כמו Max+Plus II או Quartus.קובץ זה, בדרך כלל בסביבות 16KB בגודל, מכיל את זרם ה- Bitstream המלא הדרוש להגדרת ההיגיון והניתוב של EPF8820ARC208-4.

2. בחר ערכת תצורה

בחר שיטת תצורה מתאימה המבוססת על דרישות המערכת: סידורי/מקביל פעילים (כאשר ה- FPGA שולט בטעינה) או סידורי/מקביל פסיבי (כאשר בקר חיצוני מטפל בתצורה).שיטות פסיביות הן אידיאליות למערכות הדורשות תכנות מחדש בשטח או עדכונים דינמיים.

3. הגדר חיבורי חומרה

חבר את קווי התצורה הדרושים כמו NConfig, Conf_Done, DCLK ו- DATA0 בין ה- FPGA למכשיר זיכרון התצורה שבחרת (למשל, EPC1, EPC1213).ודא כי נגדי משיכה ומקורות שעון מוגדרים כראוי כך שיתאימו למצב התצורה שנבחר.

4. אתחול כוח

כאשר המערכת מפעילה או NConfig נטענת, ה- FPGA נכנס למצב תצורה ומציב את כל ה- I/OS במצב משולש.המכשיר מוכן כעת לקבל את נתוני התצורה על סמך סכמת החיווט שיישמת.

5. טען נתוני תצורה

במצב פעיל, ה- FPGA מביא נתונים ישירות מה- EPROM באמצעות המתנד הפנימי שלו.במצב פסיבי, מעבד מארח או בקר תצורה מספקים את הנתונים, והתהליך משלים כאשר האות Conf_Done הולך גבוה.

6. אתחול פנימי ומעבר למצב משתמש

ברגע שזרם ה- Bitstream נטען במלואו ונטען conf_done, ה- FPGA מבצע אתחול פנימי, מגדיר רישומים ומאפשר קלט/פלט של משתמש.לאחר מכן המכשיר מתחיל לבצע את עיצוב ההיגיון המתוכנת לתוכו.

7. תצורה מחדש אופציונלית

אתה יכול להפעיל מחזור תצורה מחדש על ידי משיכת NConfig נמוך, שמאפס את המכשיר ומכניס מחדש את מצב התצורה.זה מאפשר עדכונים מהירים, במערכת או התאוששות לוגיקה של Fallback, כאשר כל תהליך התכנות מחדש הושלם בדרך כלל מתחת למאה אלפיות השנייה.

יתרונות EPF8820ARC208-4

• • בחירה מאוזנת בדרגה מהירה

ה- EPF8820ARC208-4 מציע איזון אידיאלי בין ביצועים לעלות, מה שהופך אותו למהיר יותר מגרסאות –2 או –3 בדרגה נמוכה יותר תוך הימנעות מנקודת המחיר הגבוהה יותר של ציון המהירות –5.זה מאפשר לעמוד בדרישות התזמון מבלי לשלם יתר על המידה עבור מרווח ראש שאינו בשימוש.

• • עיכוב ניתוב צפוי עבור היגיון בקרה

בזכות הניתוב האופקי העדין שלה ונתיבי העיכוב העקביים, EPF8820ARC208-4 מספק חיזוי תזמון מצוין.זה שימושי בעיצובים מכווני בקרה או מכוני-מדינה-כבדים

• • תצורה מהירה בשדה

המבנה מבוסס SRAM מאפשר תצורה מחדש בפחות ממאה אלפיות השנייה, ומאפשר עדכוני קושחה והגיון של Fallback במערכות חי.זה חשוב ביישומים מרוחקים או קריטיים למשימה שבהם יש למזער את השבתה.

• • חסכוני

עבור יישומים הדורשים כ- 8,000 שערי מערכת, EPF8820ARC208-4 מספק בדיוק את הכמות הנכונה של ההיגיון ללא תקורה של FPGAs מודרניים גדולים יותר.זה שומר על עלויות BOM נמוכות תוך עמידה בדרישות הפונקציונליות.

• • שילוב מתח מעורב מפושט

עם תמיכה מקורית הן לאיתות קלט/פלט של 3.3 וולט והן 5V, המכשיר מפשט את עיצוב המערכת כאשר מתממשק עם רכיבי TTL מדור קודם או מתח מעורב.זה מבטל את הצורך במעברים ברמה נוספת, וחוסך שטח לוח ועלות.

EPF8820ARC208-4 מידות אריזה

• • סוג חבילה: 208 פינים RQFP (חבילה שטוחה מרובעת מלבנית)

• • גודל גוף (D × E): 30.60 מ"מ × 30.60 מ"מ

• • מתווה חבילה (D1 × E1): בערך 28.00 מ"מ × 28.00 מ"מ

• • מגרש עופרת (ה): 0.50 מ"מ

• • אורך עופרת (L): 0.60 מ"מ טיפוסי (טווח: 0.45 מ"מ עד 0.75 מ"מ)

• • רוחב עופרת (ב): 0.17 מ"מ טיפוסי (טווח: 0.17 מ"מ עד 0.27 מ"מ)

• • זווית עופרת: 0 ° עד 8 °

• • סוג הרכבה: הר השטח

יצרן EPF8820ARC208-4

ה- EPF8820ARC208-4 מיוצר על ידי תאגיד אלתרה, חברה חלוצית בתחום התקני לוגיקה הניתנים לתכנות (PLDS) ומערכי שער הניתנים לתכנות שדה (FPGAs).Altera במקור פיתחה את משפחת Flex 8000, שאליה שייך מכשיר זה, ומציע ארכיטקטורה הניתנת להגדרה מחדש המותאמת ליישומי לוגיקה בצפיפות אמצעית.בשנת 2015 נרכשה אלתרה על ידי חברת אינטלוהמוצר המשיך להיות נתמך תחת קבוצת הפתרונות הניתנים לתכנות של אינטל.עם זאת, בשנים 2024–2025, אינטל הקימה מחדש את ALTERA כמותג עצמאי, ואישר מחדש את המיקוד שלה בפיתוח FPGA ותמיכה לטווח הארוך.בעוד ש- EPF8820ARC208-4 מסווג רשמית כמיושנת, מורשת הייצור שלה נותרה קשורה למורשת של אלתה של אספקת פתרונות לוגיים תכנותיים אמינים, גמישים ומאומצים באופן נרחב.

מַסְקָנָה

ה- EPF8820ARC208-4 הוא שבב גמיש ואמין המציע שילוב טוב של מהירות, תכונות ועלות.זה עובד היטב במערכות רבות ושונות מכיוון שניתן לתכנת מחדש, תומך במתחים שונים ומטפל במשימות מתמטיקה ושליטה במהירות.העיצוב שלו עוזר לוודא שהאותות נעים בצורה חלקה ומדויקת.למרות שזה נחשב כיום לחלק ישן או מופסק, הוא עדיין שימושי במערכות הזקוקות לביצועים יציבים ואינם יכולים לעבור בקלות לשבבים חדשים יותר.זה הופך את זה לאפשרות חכמה לעדכונים, תיקונים או תמיכה לטווח הארוך של אלקטרוניקה ישנה.

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. האם EPF8820ARC208-4 דורש זיכרון תצורה חיצוני לאתחל?

כן, היא משתמשת ב PROM סידורי או מקביל חיצוני כמו EPC1 או EPC1213 כדי לטעון את נתוני התצורה במהלך אתחול המערכת או איפוס.

2. כיצד אוכל לדעת אם עיצוב הלוח הקיים שלי תומך במצב התצורה EPF8820ARC208-4?

בדוק את הסכימה שלך אם יש סיכות נדרשות כמו NConfig, Conf_Done, DCLK ו- DATA0.כמו כן, וודא שזיכרון התצורה שלך (כמו EPC1 או EPC1213) תואם לשיטת התצורה הסדרתית או המקבילה שנבחרה.

3. האם אוכל לבצע תצורה מחדש חלקית ב- EPF8820ARC208-4?

לא, ה- EPF8820ARC208-4 אינו תומך בתצורה מחדש חלקית.כל עדכונים או שינויי לוגיקה דורשים טעינה מחדש של Bitstream מלא דרך מחזור התצורה הסטנדרטי.

4. האם יש סיכון לשחיתות זרם בוט במהלך ההפעלה?

כן, אם תזמון התצורה או שלמות האות לא מתוחזקים כראוי, עלולה להתרחש שחיתות של Bitstream.להבטיח רצף כוח נקי וניתוק תקין בסמוך לקווי FPGA וקווי התצורה.

5. האם אוכל להשתמש ב- EPF8820ARC208-4 לפונקציות קריפטוגרפיות או עיבוד מאובטח?

אמנם אינו קשוח אבטחה, אך המכשיר מתאים ליישום היגיון קריפטוגרפי מותאם אישית כמו מנועי הצפנה בסיסיים או טיפול מפתח, אך הוא חסר תכונות מאובטחות מובנות שנמצאות ב- FPGAs מודרניים.

כיצד EPM7064AEFC100-10 יכול לפשט את עיצוב ההיגיון שלך

ב- 2025/07/14

LC5768MC-75F256C CPLD: תכונות, מפרט, יתרונות ויישומים

ב- 2025/07/10

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/18 147776

-

Pinout USB-C ותכונות

ב- 2000/04/18 112022

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/18 111351

-

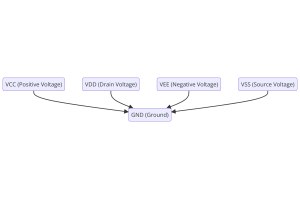

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/18 83777

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79577

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66964

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63104

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63041

-

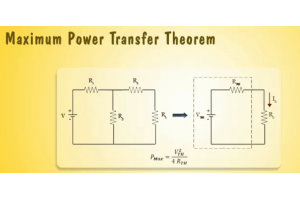

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54097

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52190