מדריך מקיף לספסלי מבחן: כלים וטכניקות לאימות מערכת דיגיטלית

מדריך זה בוחן מספי מבחן, כלי מפתח לאימות תוכנה המדמה תנאים לבדיקת כניסות ולאמת תפוקות.סנצ'ים ממלאים תפקיד בזיהוי באגים בשלב מוקדם של פיתוח, ובו שיפור אמינות התוכנה.עם דוגמאות ותובנות מעשיות, מאמר זה מדגיש את השימושים, הטכניקות והחשיבות שלהם בבניית מערכות דיגיטליות חזקות ויעילות.קָטָלוֹג

התפקיד של ספסלי מבחן באימות מערכת דיגיטלית

ספסל מבחן הוא רכיב בתהליך אימות המערכת הדיגיטלית.זה לא רק כלי לייצור תשומות ואימות תפוקות, הוא משמש כמסגרת מקיפה המדמה תנאים להערכת האמינות, הפונקציונליות והתנהגותן של מערכות דיגיטליות לפני שהם נפרסים בתחום.על ידי יצירת סביבות מבוקרות למערכות מבחני לחץ עם מגוון רחב של תרחישי קלט, ספסלי מבחן עוזרים לך לזהות פגמים פוטנציאליים בעיצוב בשלב מוקדם של מחזור חיי הפיתוח, הרבה לפני שהמערכת תושם לייצור.יש צורך בגילוי מוקדם זה של באגים ופגיעויות להפחתת שגיאות יקרות, להבטיח עמידה במפרטי הביצועים ולשיפור אמינות המערכת הכללית.

בנוסף לאימות נכונות התגובות של המערכת, ספסלי מבחן ממלאים תפקיד בהערכת מקרי קצה, בעיות תזמון ומנגנוני טיפול בשגיאות, מה שמבטיח שהמערכת יכולה לפעול כראוי אפילו בתנאים קיצוניים או לא צפויים.באמצעות בדיקות וסימולציה אוטומטית, ספסלי מבחן תורמים לאיכות תוכנה גבוהה יותר, ביצועים משופרים ומחזורי פיתוח קצרים יותר על ידי מתן בדיקות איטרטיביות ללא התערבות ידנית.הם משמשים אמצעי הגנה מפני כשלים שעלולים להתרחש לאחר הפריסה, ומבטיחים את החוסן והאמינות של מערכות דיגיטליות.

רכיבי מפתח בספסל מבחן ופונקציותיהם

כדי להבין טוב יותר כיצד פועלים ספסלי מבחן, חשוב לחקור את הרכיבים שהופכים אותם ליעילים.סוכנת מבחן מעוצבת היטב פועלת על ידי ניהול שתי משימות ליבה: יצירת תשומות (גירויים) ואימות תפוקות.בואו נבחן כל רכיב בפירוט.

דור גירוי

ייצור גירוי כרוך ביצירת קבוצה של אותות קלט המדמים תנאים לבדיקת התנהגות של מערכת דיגיטלית.תשומות אלה צריכות להיות מדויקות ומציאותיות כאחד כדי להבטיח שהמערכת נתונה למגוון תרחישים שהיא עשויה להיתקל בה בפועל.שקול מודול זיכרון RAM בסיסי כדוגמה.על ספסל הבדיקה לספק תשומות ספציפיות למודול ולהתבונן בתפוקותיו כדי להבטיח שהוא יתנהג כצפוי.כניסות המפתח למודול RAM כוללות בדרך כלל:

• CLK (שעון): נוהג בתזמון המערכת.

• ADDR (כתובת): מציין לאיזה מיקום נתונים לגישה.

• WEN (כתיבה Enable): שולט אם הנתונים נכתבים לזיכרון.

• נתונים: המידע בפועל שנכתב למודול.

הפלט, המכונה Dataout, מייצג את התוצאה של הפעולות הפנימיות של המודול.על ידי סקריפטים בזהירות כיצד נמסרים תשומות אלה ומעקב אחר נתונים, אתה יכול לוודא שהמערכת מתפקדת כראוי תחת תרחישים שונים.חשבו על יצירת גירויים כקביעת תרחיש מבחן במעבדה.כשם שמדענים שולטים בקפידה בתנאים כדי לצפות בתגובות כימיות, מעצבים דיגיטליים יוצרים תשומות מדויקות כדי לצפות כיצד מערכת מגיבה.

אימות פלט

אימות פלט הוא תהליך הבדיקה כי התפוקות בפועל של המערכת תואמות את התוצאות הצפויות.שלב זה הוא קריטי בתפיסת שגיאות מוקדם לפני שהם מתפתחים לנושאים גדולים יותר.אחרים משתמשים באימות פלט כדי לאשר שהמערכת עומדת בפונקציונליות המיועדת שלה ומופיעה בעקביות בתנאים שונים.אימות פלט כולל בדיקות אוטומטיות וגם ידניות.לְדוּגמָה:

• כלי אימות אוטומטיים: כלים כמו Modelsim ו- Quartus מאפשרים בדיקות אוטומטיות, כאשר משווים את תפוקות המערכת לתוצאות הצפויות.זה מזרז את תהליך האימות ומפחית את השגיאה.

• אימות ידני (אופציונלי): לתרחישים מורכבים יותר, ייתכן שיהיה צורך בבדיקות ידניות כדי להבטיח שמקרי קצה ספציפיים מכוסים.

כלים וטכניקות ליישום Testbench

Quartus: סימולציה של קלט/פלט חזותי

קוורטוס מספק ממשק גרפי המסדיר חזותית כניסות ומצפים תפוקות.שיטה זו יכולה להועיל למתחילים או למערכות הדורשות גישה חזותית יותר מעשית.על ידי מתן אינטראקציה עם סימולציה באמצעות סביבה גרפית, Quartus עוזר להרוס את הקשר בין תשומות לתפוקות, מה שמקל על הבנת האופן בו מערכת דיגיטלית מתנהגת בזמן.אחת מעוצמות המפתח של קוורטוס היא שהיא אידיאלית למתחילים.הממשק החזותי האינטואיטיבי שלו מספק דרך פשוטה לראות כיצד תשומות משפיעות על תפוקות ללא צורך בתסריטים או תכנות נרחבים.המשוב שהוא מציע עוזר לתפוס את התנהגותם של מעגלים ביתר קלות, מה שהופך אותו לכלי שימושי עבור עיצוב המערכת החדשה לדיגיטלית.עם זאת, לקוורטוס יש את המגבלות שלו.הגדרת הדמיות בקווארטוס יכולה להיות זמן רב, במיוחד עבור עיצובים מורכבים יותר.הכלי פחות גמיש בהשוואה לכלי סימולציה מבוססי סקריפט, שיכולים להציע אפשרויות התאמה אישית ואוטומציה יותר.לעבודה על מערכות רחבות היקף או מפורט מאוד, חוסר גמישות זה עשוי להוות אתגר.

Modelsim: סימולציה מבוססת טקסט באמצעות סקריפטים

ModelSim נוקט בגישה שונה לסימולציה על ידי עדיפות קלט מבוסס טקסט באמצעות סקריפטים.צור תרחישי מבחן באמצעות סקריפטים של Verilog (.v) או VHDL (.vhd), במקום סידור חזותי של כניסות ויציאות.שיטה זו מספקת דיוק ושליטה יותר.במקום להסתמך על ממשק גרפי, אתה מגדיר כיצד יש לבדוק את המערכת באמצעות סקריפטים מפורטים, ומאפשר התאמה אישית ואוטומציה רבה יותר בתהליך הסימולציה.אחת מעוצמות המפתח של ModelSim היא הגמישות שהיא מציעה.על ידי שימוש בסקריפטים, יש לך שליטה רבה יותר על תרחישי מבחן, מה שמאפשר להם ליצור הדמיות מורכבות ומדויקות.ברגע שמעצב מכיר את התחביר וזרימת העבודה, הגדרת הדמיות יכולה להיות מהירה בהרבה בהשוואה לשימוש בכלים גרפיים כמו קווארטוס.היכולת לעשות שימוש חוזר ולשנות סקריפטים מוסיפה גם ליעילותה, במיוחד בפרויקטים גדולים יותר.עם זאת, הגישה המבוססת על טקסטים של ModelSIM מגיעה עם מגבלות מסוימות.זה דורש הבנה מוצקה של תחביר Verilog או VHDL, שעשוי להוות אתגר למתחילים שאינם מכירים שפות תיאור חומרה.כתוצאה מכך, לדגמים יש עקומת למידה תלולה יותר בהשוואה לכלי סימולציה חזותיים יותר.משתמשים חדשים עשויים להתקשות להתחיל, אך עם תרגול, הדיוק והגמישות המוצעים על ידי סקריפט יכולים להפוך לנכס חשוב.

גישור על תורת הגישור והפרקטיקה באימות

ספסלי מבחן משמשים כגשר בין עיצובים ויישומים תיאורטיים על ידי הדמיה כיצד תתנהג מערכת דיגיטלית בתנאים שונים, כולל מקרי קצה ותשומות בלתי צפויות.בעיצוב דיגיטלי, לעיתים קרובות קשה לחזות כיצד מערכת תבצע בפועל המבוססת אך ורק על מודלים תיאורטיים.ספסלי מבחן סוגרים פער זה בכך שהם מאפשרים לך לעבור מעבר למושגי תכנון מופשטים ולהעריך את התנהגות המערכת בסביבה מבוקרת ומדומה.אחד היתרונות העיקריים של שימוש בכלי סימולציה בספסלי מבחן הוא המשוב המיידי שהם מספקים במהלך ניפוי באגים.כלים כמו Multisim או Modelsim מציעים ייצוגים חזותיים של התנהגות מערכת, המראים כיצד שינויים בתשומות משפיעים על תפוקות לאורך זמן.משוב זה מאפשר לך להצביע על בעיות מהר יותר, לעקוב אחר שגיאות בחזרה למטרת השורש שלהם ולהתאים את העיצובים שלהם בהתאם.לדוגמה, אם מערכת לא מצליחה לעמוד באילוצי תזמון או מציגה התנהגות בלתי צפויה תחת רצפי קלט מסוימים, ספסל מבחן יכול להדגיש פגמים אלה מייד, הרבה לפני שהמערכת בנויה פיזית.על ידי זיהוי סוגיות בשלב מוקדם של מחזור העיצוב, ספסלי מבחן מפחיתים את הצורך בעבודות חוזרות יקרות ואב -טיפוס פיזי, תוך ייעול תהליך האימות.אימות בשלב מוקדם זה מסייע להבטיח שמערכות דיגיטליות הן נכונות מבחינה פונקציונלית ועמידה לתנאים, מה שהופך אותן לאמינות יותר והפחתת הסיכון לכישלון לאחר הפריסה.באופן זה, ספסלי מבחן פועלים ככלי מעשי להפיכת עיצובים תיאורטיים לחזקה.

ארכיטקטורת TestBench מתקדמת

סנפי מבחן מתקדמים חורגים מבדיקות קלט-פלט פשוטות על ידי שילוב רכיבים נוספים לניהול מערכות מורכבות.ספסל מבחן סטנדרטי כולל שלושה חלקים עיקריים: א גנרטור גירוי ליצירת אותות קלט, א תכנון תחת מבחן (DUT), שהיא החומרה בפועל שנבדקת, ו- צג פלט זה בודק את התפוקות כנגד תוצאות צפויות.רכיבים אלה פועלים יחד כדי להבטיח אימות יסודי ומדויק יותר של עיצובים דיגיטליים.

שיפור דיוק המבחן כרוך בשימוש בטכניקות המבטיחות שעיצוב מתפקד באופן אמין בתרחישים שונים. בדיקות אקראיות מציג דפוסי קלט בלתי צפויים כדי לאמת את יציבות המערכת בתנאים שונים. בדיקת מקרה קצה מתמקד במצבי גבול בהם המערכת צפויה להיתקל בשגיאות.לבסוף, בדיקת רגרסיה כרוך בבדיקות ריצות מחדש לאחר שינויים כדי לאשר שלא הוצגו בעיות חדשות, מה שמבטיח שהמערכת תישאר עקבית ונטולת שגיאות לאורך זמן.

סנפי תסריט

כדי ליצור סנפי מבחן יעילים ואמינים ב- Verilog או VHDL, עקוב אחר שיטות העבודה המומלצות העיקריות.התחל פשוט, ואז התרחב על ידי בדיקת פונקציונליות בסיסית תחילה והוספת בהדרגה תרחישים מורכבים יותר.השתמש בתגובות ותיעוד כדי להקל על הסקריפטים שלך להבנה ותחזוקה על ידי הסבר בבירור של כל קטע.לבסוף, אוטומציה במידת האפשר כדי לחסוך זמן ולהפחית שגיאות באמצעות לולאות ופונקציות כדי לטפל במשימות חוזרות ונשנות ודפוסי קלט.

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

לולאה נעולה שלב דיגיטלי (DPLL): עיצוב, רכיבים ותפעול

ב- 2025/01/7

ההתפתחות וההשפעה של ארכיטקטורת RISC במחשוב מודרני

ב- 2025/01/7

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/18 147760

-

Pinout USB-C ותכונות

ב- 2000/04/18 111967

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/18 111351

-

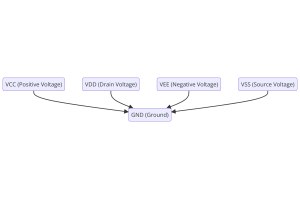

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/18 83729

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79516

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66930

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63078

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63023

-

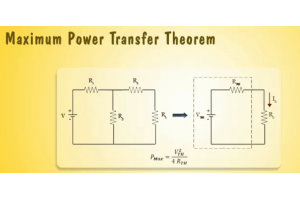

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54088

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52160