מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ניתוח הארכיטקטורה האולטימטיבית של מעבדי מחשבים חושף את המורכבות העומדת מאחורי פעולתם וביצועיהם.בין עיצובי המעבדים המשפיעים ביותר הם מחשב ההוראות המורכב של מחשב (CISC) וארכיטקטורות מחשב ההוראות המופחתות (RISC).כל אחת מהן מציעה גישות ייחודיות לביצוע הוראות, יעילות תכנות ועיצוב חומרה.מאמר זה בוחן את המורכבות של ארכיטקטורת CISC, ומדגיש את מערך ההוראות הנרחב שלה המפשט את התכנות תוך הצגת אתגרי חומרה.זה גם חופר בגישת RISC היעילה, שמיטבת את הביצועים באמצעות מערך הוראות מפושט ויעיל.לבסוף, הפוסט מדגיש כיצד מעבדים מודרניים מאמצים יותר ויותר אדריכלות היברידית, ומיזוג את חוזקותיהם של CISC וגם RISC כדי לענות על צרכים חישוביים מגוונים.קָטָלוֹג

סקירה כללית של CISC

הארכיטקטורה של מעבד מחשבים מתרכזת סביב ביצוע מגוון מגוון של הוראות או מיקרו -הרווחה, שכל אחת מהן נועדה למלא משימות ספציפיות.אמנם מערך הוראות מקיף יותר יכול להפוך את התכנות למעבד המיקרו -אינטואיטיבי יותר, אך היא עשויה גם להכניס מכשולים בביצועים פוטנציאליים.ארכיטקטורת המחשב ההוראות המורכבת (CISC) בולטת בשל אוסף ההוראות העצום שלה, כולל אלה מורכבים המפשטים את חווית התכנות בהשוואה לארכיטקטורות אלטרנטיביות.כל משימה, בין אם פשוטה או מורכבת, משויכת להוראות ייחודיות, מה שמקטין את כמות הקידוד הדרושה.עם זאת, תכנון מורכב זה יכול להוות אתגרים בולטים בפיתוח ה- CPU ובמעגלי יחידת הבקרה הנלווים.

הארכיטקטורה של CISC נבדלת על ידי מבחר רחב של מיקרו -אי -הסבר המאפשרים פיתוח תוכניות למעבד.מיקרו-אי-הכשבות אלה, המפורשות לעתים קרובות בשפת ההרכבה, מחליפות פונקציות מסוימות שהטופלו באופן מסורתי על ידי תוכנה במערכות הדרכה ברמת חומרה.שינוי זה לא רק מאיר את עומס העבודה עבורך, אלא גם מאפשר ביצוע בו זמנית של פעולות ברמה נמוכה במהלך כל מחזור הוראות, ומשפר את המהירות הכוללת של ביצוע מחשב.

תדירות השימוש בהוראות בתוך מערך ההוראות של CISC מציגה חוסר איזון בולט.בדרך כלל משתמשים בכ- 20% מההוראות, המהווים כ- 80% מכלל קוד התוכנית, ואילו לעיתים רחוקות נעשה שימוש ב -80% הנותרים, ותורמים ל 20% בלבד מהתכנות.תצפית זו מהדהדת עם עיקרון רחב יותר שנצפה בשדות שונים: מבחר קטן של כלים או שיטות מייצר לרוב את רוב התוצאות.

CISC ו- RISC השוואה

ארכיטקטורת מחשב ההוראות המופחתת (RISC) בולטת בשל מערך ההוראות היעיל שלה, שמטרתו להגביר את יעילות המעבד.עם זאת, עיצוב זה דורש גישה מתוחכמת יותר לתכנות חיצוניות.על ידי התמקדות בהוראות הפשוטות הנפוצות ביותר, RISC נמנעת למעשה מהסיבוכים המלווים לעתים קרובות פקודות מורכבות יותר.

• ארכיטקטורת RISC סטנדרטית את אורך ההוראה.

• זה מפשט פורמטי הוראות, בעיקר מסתמך על היגיון השליטה.

• בחירת תכנון זו מבטלת את הצורך בבקרת מיקרו -קוד, וכתוצאה מכך מהירויות תפעוליות מהירות יותר.

ניתן לאתר את מקורותיו של RISC למחקר פורץ הדרך שנערך על ידי ג'ון קוקה ב- IBM.ממצאיו הצביעו על כך שרק כ -20% מהוראות המחשב מהוות בערך 80% מעומס העבודה החישובי.תובנה זו נושאת משקל משמעותי, ומציעה כי על ידי אופטימיזציה של ההוראות המבוצעות בתדירות הגבוהה ביותר, ניתן להשיג שיפורי ביצועים נרחבים.כתוצאה מכך, מערכות RISC עולות לעתים קרובות על ההוראות המורכבות מגדירות מערכות מחשב (CISC), המתאימות לעקרון 80/20 הידוע המודיע על פיתוח ארכיטקטורת RISC.

בעוד ש- RISC מתהדרת בכמה יתרונות, היא אינה מחליפה לחלוטין את ארכיטקטורת ה- CISC.לכל סוג יש את חוזקותיו המובחנות, וההבדלים ביניהם הפכו פחות בולטים לאורך זמן.בפרקטיקה העכשווית, מעבדים מודרניים רבים משלבים אלמנטים הן מ- RISC והן מ- CISC, ומשקפים מגמה הולכת וגוברת לאדריכלות היברידית.לדוגמה, מעבד הוראות אולטרה-ארוך (ULIW) ממחיש תערובת זו, ומיזוג את היתרונות של שתי האדריכלות כדי לייצר יחידת עיבוד הניתנת להתאמה יותר.היתוך זה לא רק מגביר את הביצועים אלא גם מציג גמישות בתכנות, ומאפשר מגוון רחב יותר של יישומים.

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

טכנולוגיית חבילה מרובעת מרובעת (QFP): עיצוב, יישומים ואתגרים

ב- 2024/12/30

מכשירי לוגיקה ניתנים לתכנות (EPLDS): מדריך לעיצוב ויישומים

ב- 2024/12/30

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/18 147752

-

Pinout USB-C ותכונות

ב- 2000/04/18 111924

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/18 111349

-

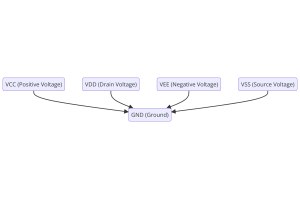

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/18 83714

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79502

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66872

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63005

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 62955

-

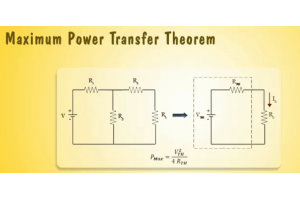

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54078

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52092