CPLD הסביר: מדריך למכשירי לוגיקה הניתנים לתכנות

בעולם הדינאמי של העיצוב האלקטרוני, מכשירי לוגיקה מורכבים לתכנות (CPLDS) בולטים ככלי רב -תכליתי, תוך מיזוג חלקה של יכולת הסתגלות, דיוק ויעילות.מכשירים אלה חוללו מהפכה בתכנון המעגלים על ידי הצגת תאי מאקרו הניתנים לתכנות ומטריצה קשרים דומיננטית, מה שמאפשר ליצור פונקציות לוגיות מורכבות עם אמינות מדהימה.מההתחלה שלהם בשנות השמונים ועד תפקיד המפתח שלהם בתעשיות מודרניות כמו רשת, רכב וחלל, CPLDs הוכיחו כי אתה מחפש גמישות וגם ביצועים.מאמר זה חופר במסע של CPLDS, התכונות הייחודיות שלהם, יישומים מעשיים ומתודולוגיות התכנות שהופכות אותם לאבן הפינה בעיצוב לוגיקה דיגיטלית.קָטָלוֹג

סקירה כללית של CPLD

במסגרת שליטה של התקני לוגיקה מורכבים לתכנות (CPLDS), ניתן למנות שטיח מתוחכם של תאי מקרו לוגיים הניתנים לתכנות, השזורים באמצעות מטריצה דומיננטית בחיבור.קווי יחידת יחידת קלט/פלט (קלט/פלט) אלה (MC) וקווי קלט/פלט (קלט/פלט) מאפשרים לך לתכנן מעגלים בעדינות, ולגדיר את התצורה של המבנים לפונקציות ייחודיות.בניגוד למכשירים המבולבלים על ידי תזמון הקשרים המורכבים שלהם, CPLDs משתמשים בחוטי מתכת בלתי ניתנים לניתוח.מאפיין זה מעניק להם התנהגות שעון עקבית וניתן לעין, מה שהופך את תחזיות העיתוי לאמינות ומדויקות יותר.

המסע והניצול

שנות השבעים בישרו על כניסתם של מכשירי לוגיקה הניתנים לתכנות (PLDS), וטיפחו מהלך לעבר יחידות מאקרו הניתנות לתכנות.משמרת זו הציגה גמישות עיצובית בשפע, ומבדילה אותם ממעגלים דיגיטליים סטטיים, אם כי התועלת שלהם הוגבלה בתחילה למעגלים פשוטים יותר.הופעתם של CPLDS באמצע שנות השמונים חוללה מהפכה בנוף זה, וסללה את הדרך לעיצובים מעגלים מורכבים.מאז, הם ארכו את עצמם למארג התעשיות כמו רשתות, אלקטרוניקה לרכב, עיבוד שבבי CNC ומערכות תעופה וחלל.אתה יכול להזכיר את האופן בו CPLDS פשט תהליכים שדרשו בעבר עבודות כפיים קפדניות, תוך סימון קפיצה מדהימה ביעילות.

תכונות ייחודיות של CPLD

CPLDs מבדילים את עצמם באמצעות תכנות הניתנת להתאמה שלהם, אינטגרציה נרחבת, יכולות פיתוח מהירות ויישומיות רחבה, יחד עם עלויות ייצור חסכוניות.הם פונים לאנשים עם ניסיון חומרה מינימלי, ומשמשים כמוצרים אמינים ומאובטחים שאינם מחייבים בדיקות ממצה.כעדות לקישור שלהם בעיצובים של מעגלים בקנה מידה גדול, CPLDS ממלאים תפקיד מפתח בפיתוח אב-טיפוס ומשרתים ריצות מתחת ל -10,000 יחידות, המגלמת יכולת שימושית עבורך.המיומנות שבה CPLDS מסתגלת לדרישות הפרויקט המתפתחות מרוויחות אותם לעתים קרובות הערכה, ומדגישה את הרבגוניות שלהם בפועל בסביבות דינמיות.

שיטות יישום

מעגלים משולבים אלה מאפשרים לך לפרט על פונקציות לוגיות המותאמות לצרכים שלהם באמצעות שפות סכימות וגם תיאור חומרה בפלטפורמות פיתוח.לדוגמה, בעיצוב מכונת תשובה, תיאורי סכימות ותיאורי חומרה מוכנים ומורכבים במחשב.תוך שימוש בכבל הורדה, הקוד מועבר ל- CPLD לתכנות במערכת, הכולל בדיקות, פתרון בעיות ושיפור עיצובים.עיצובים מעוצבים בהצלחה מיוצרים המונים על ידי שכפול שבבי CPLD.בפרויקטים כמו מערכות רמזור, חזרה על תהליך העיצוב הופכת לנדרשת, בדומה לבניית בית מחדש כדי להחזיר את החדשות שלו.מתודולוגיה חוזרת ונשנית זו מניחה לעתים קרובות את הקרקע לשליטה, ומגבירה הן כישורים והן את הביטחון.

גרסאות מובילות

לאורך כל השנים, חברות כמו Altera, Lattice ו- Xilinx חשפו קווים בולטים של CPLDs.דוגמאות ראויות לציון כוללות אלטרה EPM7128S, סריג LC4128V, ושל קסילינקס XC95108 ומודלים אלה מצאו תפקידים בולטים על פני יישומים גלובליים מגוונים.אלה שעברו הזכות לעבוד עם מוצרים מובחנים אלה מעירים לעתים קרובות על ההבדלים העדינים ועם זאת חזקים המייטמים את הפונקציות הספציפיות.זה משקף תהליך בחירה משובח שהושפע מדרישות הפרויקט הספציפיות, כאשר כל גרסה מחזיקה בערעורו הייחודי.

זיהוי וסיווג של FPGA ו- CPLD

|

אַספֶּקט |

CPLD |

FPGA |

|

היווצרות התנהגות הגיונית |

צור התנהגות הגיונית באמצעות מבנה מונחי המוצר.

דוגמאות: סדרת ISPLSI של סריג, סדרת Xilinx XC9500, Altera Max7000S

סדרה, סדרת מאץ 'סריג |

ליצור התנהגות הגיונית בשיטת בדיקת טבלה.

דוגמאות: סדרת Xilinx Spartan, Altera Flex10K, Acex1k |

|

הַתאָמָה |

מתאים לאלגוריתמים ולהיגיון שילוב, עובד

עדיף עם טריגרים מוגבלים ומונחי מוצר עשירים |

מתאים ללוגיקה רציפה, עובד טוב יותר עם

מבנים עשירים בטריגרים |

|

עיכוב תזמון |

מבנה חיווט רציף מספק אחיד ו

עיכוב תזמון צפוי |

מבנה חיווט מפולח מוביל לתזמון בלתי צפוי

עיכובים |

|

תכנות גמישות |

מעגלים פנימיים קבועים משתנים לתכנות.

נעשה שימוש בתכנות ברמת בלוק |

חיווט פנימי משתנה לתכנות.הִגָיוֹן

תכנות ברמת השער מאפשרת גמישות רבה יותר |

|

הִשׁתַלְבוּת |

אינטגרציה נמוכה יותר בהשוואה ל- FPGA |

שילוב גבוה יותר עם מבנה חיווט מורכב יותר ו

יישום לוגיקה |

|

קלות השימוש |

קל יותר לשימוש בתכנות באמצעות E2PROM או FastFlash.

לא נדרש שבב זיכרון חיצוני |

דורש זיכרון חיצוני לאחסון תכנות

מידע, המוביל לשימוש מורכב יותר |

|

מהירות וחיזוי |

מהירות מהירה יותר וחיזוי תזמון טוב יותר בגלל

חיבור גושני בין חסימות לוגיות |

מהירות איטית יותר ותזמון פחות צפוי בגלל

תכנות ברמת השער וחיבור מחובר |

|

טכנולוגיית תכנות |

משתמש בתכנות E2PROM או Flash זיכרון.נתוני תכנות

נשמר כאשר המערכת כבויה.תומך בתכנות ב-

מתכנת או במערכת |

מבוסס על תכנות SRAM.נתוני תכנות אבודים כאשר

המערכת כבויה ויש לטעון מחדש.תומך בדינמי

תְצוּרָה |

|

סודיות |

מציע סודיות טובה יותר |

מספק סודיות נמוכה יותר |

|

צריכת חשמל |

בדרך כלל צריכת חשמל גבוהה יותר, במיוחד עם

שילוב גבוה יותר |

צריכת חשמל נמוכה יותר בהשוואה ל- CPLD |

תכנות שפות של CPLD

ניתוח כיצד מתוכנת התקני לוגיקה מורכבים לתכנות (CPLDS) הוא אבן יסוד ביצירת פתרונות חומרה רב -תכליתית.השיטות ההיסטוריות לתכנות CPLDs הסתמכו על דיאגרמות סולם או שפות תיאור חומרה (HDLs), כאשר Verilog HDL ו- VHDL הם בחירות שולטות.השפה שנבחרה יכולה לעצב הן את אסטרטגיית העיצוב והן את היעילות התפעולית של היישומים.

• • Verilog HDL: Verilog HDL מוקירה בתחביר הפשוטה שלו ויכולות הסימולציה החזקות שלה, ומשקפת את המתודולוגיות המשמשות בעיצוב לוגיקה דיגיטלית.שילובו עם כלי אוטומציה של עיצוב אלקטרוני (EDA) מאפשר לך לבצע בצורה חלקה סינתזה וסימולציה.התחביר הדומה ל- C של Verilog נצפה כמוריד את מחסום הכניסה לאלה עם רקע תכנות, מה שממהר את המסע מעיצוב לפריסה על פני מגוון רחב של מגזרים תעשייתיים.

• • VHDL: VHDL מספק אפשרות מורחבת ומביעה יותר לתכנות HDL.לעתים קרובות זו הבחירה בפרויקטים הדורשים תיעוד קפדני ובדיקת סוג קפדני, תכונות המוערכות בתעשיות האווירה והביטחון.ניתן לציין שלמרות המורכבות הפוטנציאלית של VHDL בפרויקטים קטנים יותר, המבנה הממושמע שלו תומך ביצירת עיצובים אמינים במיוחד, הכרח בסביבות בהן הבטיחות דומיננטית.

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

טרנזיסטורים של NMOS: תכנון, הפעלה ויישומים

ב- 2024/12/29

טרנספורמציית FAST Fourier (FFT): מהפכה בעיבוד אותות דיגיטליים

ב- 2024/12/29

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/18 147760

-

Pinout USB-C ותכונות

ב- 2000/04/18 111967

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/18 111351

-

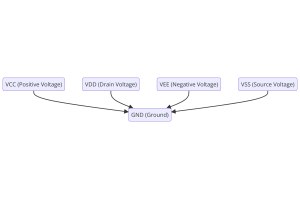

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/18 83729

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79516

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66930

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63078

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63023

-

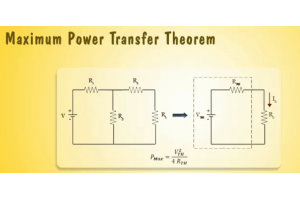

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54088

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52160