AT89S52-24PU מיקרו-בקר: אלטרנטיבות, פינאוט וגיליון נתונים

מאמר זה בוחן את בקר המיקרו AT89S52-24PU, ומדגיש את מאפייניו, השימושים המעשיים שלו וכיצד הוא מטפל ביעילות בכוח ובביצועים ביישומים תובעניים.מכשיר זה ידוע בזכות 8K בתים של זיכרון פלאש וצריכת חשמל נמוכה, ומכשיר זה הוא אידיאלי לאזן בין יעילות אנרגטית עם פונקציונליות חזקה במכשירים המונעים על סוללות.קָטָלוֹג

מהו AT89S52-24PU?

THE AT89S52-24PU בקר מיקרו הוא מכשיר גמיש ביותר שמשלב מעבד 8 סיביות עם זיכרון פלאש הניתן לתכנות על שבב יחיד.על ידי רתימת טכנולוגיית הזיכרון המתקדמת של ATMEL, מיקרו -בקר זה שומר על תאימות למערך ההוראות 80C51 המוערך.הפלאש הניתן לתכנות מחדש על השבב שלו מתאים לצרכים המגוונים של מערכות בקרה משובצות שונות באופן יעיל וחסכוני כאחד.בקר המיקרו כולל 8K פלאש ו -256 בתים של זיכרון RAM, ומספק יכולת נרחבת לתכנות מורכבות וקייטרינג ליישומים הדורשים עיבוד נתונים מורכב.הכללתם של 32 קווי קלט/פלט למטרה כללית מציעה את הרבגוניות לחיבור מגוון רחב של ציוד היקפי.

עם שלושה טיימר/דלפקים של 16 סיביות, AT89S52-24PU תומך בפונקציות מבוססות זמן מדויקות, אשר לא יסולא בפז עבור הגדרות עיבוד נתונים ובקרה.מצביעי הנתונים הכפולים משפרים ביעילות את יעילות הטיפול בנתונים, ותומכים בתרחישים העברת נתונים מהירים.טיימר כלב השמירה מוסיף שכבה של אמינות על ידי איפוס המערכת במהלך חריגות תוכנה, תכונה המוקירה על ידי מגזרים העדיפים שלמות מערכת ארוכת טווח.יכולתו של בקר המיקרו להפעלה סטטית בתדרים שונים מסייעת באיזון בין ביצועים עם צריכת חשמל.הזמינות של מצבי חיסכון בחשמל, כולל סרק והכוח-למטה, מדגישה את נאותותה ליישומים המופעלים על ידי סוללות, ומבטיחה שמירה על תוכן זיכרון במהלך שלבי ההפעלה.תכונות אלה עוסקות בדאגות יעילות אנרגיה, כפי שמעידים אימוץ במכשירים ניידים ומופעלים מרחוק.

AT89S52-24PU תצורת PIN

|

סיכה לא |

שם סיכה |

תֵאוּר |

|

1-8 |

יציאה 1 |

לממשק 1 יש משיכות פנימיות והיא 8 סיביות

יציאת קלט/פלט דו -כיוונית.ארבע כניסות TTL יכולות להיות כיור/מקור ביציאה 1

מאגרי פלט.כאשר 1 נכתבים לסיכות יציאה 1, המשיכות הפנימיות

משוך אותם לגובה, ומאפשר להשתמש בהם ככניסות.בגלל הפנימי

משיכות, סיכות יציאה 1 שנדחפות חיצוניות נמוכות יקבעו את זרם הזרם

(Iil) ככניסות.בנוסף, כפי שמוצג בטבלה, ניתן להגדיר P1.0 ו- P1.1

כדי להיות קלט הספירה החיצונית של טיימר/מונה 2 (P1.0/T2) ו-

טיימר/מונה 2 קלט ההדק (P1.1/T2EX), בהתאמה.במהלך הבזק

תכנות ואימות, יציאה 1 מקבלת גם את הכתובת בהזמנה נמוכה

בתים. |

|

9 |

RST |

יש לאפס את הקלט.ואילו המתנד הוא

תפקוד, גבוה בסיכה זו לשני מחזורי מכונות מאפס את המכשיר.

לאחר שתוזמן כלב השמירה, הסיכה הזו הולכת לגובה 98 מתנד

תקופות.ניתן להשבית תכונה זו באמצעות הסיביות של ה- DISSTO ב- SFR AUXR

(כתובת 8eh).יכולת האיפוס High Out מופעלת כברירת מחדל ב- BIT

לא. |

|

10-17 |

יציאה 3 |

יציאה 3 היא קלט/פלט דו-כיווני של 8 סיביות דו-כיווניות

נָמָל.ניתן לשקע או למקור ארבע כניסות TTL באמצעות מאגרי הפלט של יציאת 3.

כאשר 1 נכתבים ל- PINT 3 סיכות, המשיכות הפנימיות מושכות אותם גבוהות,

ומאפשר להשתמש בהם ככניסות.בגלל המשיכות, יציאה 3 סיכות את זה

הם נמשכים חיצוניים נמוכים ימקור זרם (IIL) ככניסות.לפלאש

תכנות ואימות, יציאה 3 מקבלת כמה אותות בקרה.כאמור

בתרשים למטה, יציאה 3 תומכת גם בפונקציות של מספר רב של AT89S52

תכונות מיוחדות. |

|

18 |

XTAL2 |

פלט ממגבר המתנד הפוך. |

|

19 |

XTAL1 |

קלט למגבר המתנד ההפוך וקלט

מעגל ההפעלה השעון הפנימי. |

|

20 |

GND |

טָחוּן. |

|

21-28 |

יציאה 2 |

יציאה 2 היא קלט/פלט דו כיווני של 8 סיביות דו-כיווניות

נָמָל.ארבע כניסות TTL יכולות להיות כיור/מקור במאגר הפלט של יציאה 2.כַּאֲשֵׁר

1s נכתבים לפינים של יציאה 2, המשיכות הפנימיות מושכות אותן גבוהות ומאפשרות

אותם ישמשו ככניסות.בגלל המשיכות הפנימיות, יציאה 2 סיכות את זה

הם נדחפים חיצוניים נמוכים ימקור זרם (IIL) ככניסות.במהלך אחיזה

מזיכרון התוכנית החיצונית וגישה לזיכרון נתונים חיצוני המשתמשים

כתובות 16 סיביות (Movx @ DPTR), יציאה 2 פולטת את בייט הכתובת בסדר גודל גבוה.

בעת העברת 1s, יציאה 2 משתמשת במשיכות פנימיות עוצמתיות בעניין זה

בַּקָשָׁה.יציאה 2 פולטת את תוכן מרשם הפונקציות המיוחד של P2

במהלך גישה של 8 סיביות גישה לזיכרון נתונים חיצוני (Movx @ RI).בְּמַהֲלָך

תכנות ואימות פלאש, יציאה 2 בנוסף מקבלת את ההזמנה הגבוהה

כתובת סיביות וסימני בקרה שונים. |

|

29 |

Psen |

נקראת Strobe לזיכרון התוכנית החיצוני נקראת

חנות התוכנית Enable (PSEN).Psen מופעל פעמיים בכל מחזור מכונה כאשר

ה- AT89S52 מפעיל קוד מזיכרון התוכנית החיצונית, עם שני psen

הפעלות התעלמו במהלך כל גישה לזיכרון נתונים חיצוני. |

|

30 |

Ale/Prog |

דופק הפלט של תפס הכתובת (ALE) משמש ל

תפס את בתים הנמוכים של הכתובת במהלך גישה לזיכרון חיצוני.בְּמַהֲלָך

תכנות פלאש, סיכה זו משמשת גם ככניסה לדופק התוכנית (PROG).

ALE משתחרר בקצב יציב של 1/6 תדר המתנדק בנורמלי

פעולה ויכולה לשמש לתזמון חיצוני או לענג.עם זאת, במהלך

כל גישה לזיכרון נתונים חיצוני, מדלג על דופק אייל אחד.הגדרת סיביות 0

של מיקום SFR 8EH עד 0 מבטל את תפקוד ה- ALE אם תרצה.Ale פעיל רק

כאשר הסיביות מוגדרת באמצעות הוראות Movx או Movc.אחרת, הסיכה היא

הרים גבוה אך חלש.אם בקר המיקרו נמצא במצב ביצוע חיצוני,

לקביעת הסיביות המובילה ALE אין השפעה. |

|

31 |

EA/VPP |

גישה חיצונית מופעלת.כדי לאפשר את המכשיר

הבאת קוד מאזורי זיכרון לתוכנית חיצונית החל מ- 0000h ומסתיים

ב- FFFFH, EA חייב להיות מחובר ל- GND.עם זאת, אם נעילה 1 מקודד, EA

יופעל באופן פנימי באיפוס.לביצוע תכנית פנימית, EA

צריך להיות קשור ל- VCC.במהלך תכנות פלאש, סיכה זו בנוסף

מקבל את התכנות 12 וולט אפשרות מתח (VPP). |

|

32-39 |

יציאה 0 |

ממשק 0 הוא יציאת קלט/פלט דו כיוונית של 8 סיביות.

כל סיכה יכולה לשקוע שמונה כניסות TTL כנמל פלט.הסיכות בנמל 0 יכול

לשמש ככניסות עכבה גבוהות כאשר 1 נכתבים להם.במהלך הגישות

לתוכנית חיצונית וזיכרון נתונים, יציאה 0 ניתן להגדיר גם כ-

אוטובוס כתובת/נתונים מסדר נמוך מרובה.P0 כולל משיכות פנימיות בזה

מצב.במהלך תכנות פלאש, יציאה 0 גם מקבלת את הבתים והפלטים של הקוד

אותם במהלך אימות התוכנית.במהלך אימות התוכנית, משיכות חיצוניות

נדרשים. |

|

40 |

VCC |

מתח אספקה. |

AT89S52-24PU סמל, טביעת רגל ודגם CAD

AT89S52-24PU סמל

AT89S52-24PU טביעת רגל

AT89S52-24PU מודל CAD

מאפיינים של AT89S52-24PU

• תאימות סטנדרטית של MCS®-51: תואמת לחלוטין לתקן MCS®-51, ומבטיחה ביצועים חזקים ואמינים.

• זיכרון פלאש 8K ISP: מאחסן תוכניות גדולות.תומך עד 10,000 מחזורי כתיבה/מחיקה, אידיאלי ליישומים לטווח הארוך.

• מתח הפעלה רחב (4V - 5.5V): מסתגל לסביבות אספקת חשמל שונות.

• פעולה במהירות גבוהה: מטפלת בתנאים סטטיים עד 33 מגה הרץ, ומאזן בין יעילות אנרגיה לצרכי הביצועים.

• אבטחה משופרת: תכונות נעילת זיכרון מגנות על קניין רוחני.מונע גישה או שינויים בלתי מורשים.

• פונקציות קלט/פלט וטיימר גמישות: שילוב קל עם חיישנים ומכשירים.בקרה מדויקת ליישומי זמן הדורשים תזמון מדויק.

• מצביעי נתונים כפולים: מגביר את היעילות במשימות כבדות נתונים כמו עיבוד אותות ותקשורת.מפשט את הטיפול בזרם נתונים.

• מצבי חיסכון באנרגיה: מצבים סרק ומורדים מפחיתים את צריכת האנרגיה.מותאם למכשירים ניידים ועיצובים בר -קיימא.

AT89S52-24PU מפרטים טכניים

|

סוּג |

פָּרָמֶטֶר |

|

זמן ההובלה של המפעל |

7 שבועות |

|

הַר |

דרך החור |

|

חבילה / מקרה |

40-DIP (0.600, 15.24 מ"מ) |

|

מספר I/OS |

32 |

|

טמפרטורת הפעלה |

-40 מעלות צלזיוס ~ 85 מעלות צלזיוס |

|

סִדרָה |

89S |

|

קוד JESD-609 |

E3 |

|

סטטוס חלק |

פָּעִיל |

|

מספר הסיומות |

40 |

|

מתח אספקה |

5V |

|

תֶדֶר |

33MHz |

|

מתח אספקת הפעלה |

5V |

|

מִמְשָׁק |

UART |

|

צור ציפוי |

פַּח |

|

סוג הרכבה |

דרך החור |

|

מספר הסיכות |

40 |

|

טיימרים של כלב השמירה |

כֵּן |

|

אריזה |

שְׁפוֹפֶרֶת |

|

פורסם |

1997 |

|

קוד PBFREE |

כֵּן |

|

רמת רגישות לחות (MSL) |

1 (ללא הגבלה) |

|

מיקום מסוף |

כָּפוּל |

|

מגרש מסוף |

2.54 מ"מ |

|

מספר חלק בסיס |

AT89S52 |

|

ספקי כוח |

5V |

|

גודל זיכרון |

8KB |

|

מְהִירוּת |

24 MHz |

|

מתח - אספקה (VCC/VDD) |

4V ~ 5.5V |

|

מספר הקטעים |

8 |

|

ציוד היקפי |

WDT |

|

גודל ליבה |

8 סיביות |

|

קישוריות |

UART/USART |

|

זמן גישה |

24 מיקרו |

|

ערוצי DMA |

לֹא |

|

ערוצי PWM |

לֹא |

|

מספר טיימרים/דלפקים |

3 |

|

מספר ערוצי UART |

1 |

|

מֶשֶׁך |

52.58 מ"מ |

|

להגיע ל- SVHC |

אין SVHC |

|

סטטוס ROHS |

תואם ROHS3 |

|

סוג מתנד |

פְּנִימִי |

|

גודל זיכרון RAM |

256 x 8 |

|

UPS/UCS/סוג ICS היקפי |

בקר מיקרו |

|

מעבד ליבה |

8051 |

|

סוג זיכרון התוכנית |

הֶבזֵק |

|

גודל זיכרון התוכנית |

8KB 8K x 8 |

|

גודל סיביות |

8 |

|

יש ל- ADC |

לֹא |

|

רוחב אוטובוס נתונים |

8b |

|

ערוצי DAC |

לֹא |

|

כתובת רוחב אוטובוס |

8b |

|

גוֹבַה |

4.826 מ"מ |

|

רוֹחַב |

13.97 מ"מ |

|

התקשות קרינה |

לֹא |

|

עופרת חופשית |

עופרת חופשית |

AT89S52-24PU חלקים דומים

שלושת הרכיבים המפורטים מימין דומים במפרט לאלה של טכנולוגיית מיקרו-צ'יפ AT89S52-24PU.

|

מספר חלק |

יַצרָן |

חבילה / מקרה |

מספר הסיכות |

רוחב אוטובוס נתונים |

מספר קלט/פלט |

מִמְשָׁק |

גודל זיכרון |

מתח אספקה |

ציוד היקפי |

|

AT89S52-24PU |

טכנולוגיית מיקרו -שבב |

40-DIP (0.600, 15.24 מ"מ) |

40 |

8 ב |

32 |

UART |

8 KB |

5 V. |

WDT |

|

AT89C55WD-24PU |

טכנולוגיית מיקרו -שבב |

40-DIP (0.600, 15.24 מ"מ) |

40 |

8 ב |

32 |

SPI, UART, USART |

32 KB |

5 V. |

WDT |

|

AT89S51-24PU |

טכנולוגיית מיקרו -שבב |

40-DIP (0.600, 15.24 מ"מ) |

40 |

8 ב |

32 |

UART, USART |

4 KB |

5 V. |

WDT |

|

AT89C51RC-24PU |

טכנולוגיית מיקרו -שבב |

40-DIP (0.600, 15.24 מ"מ) |

40 |

8 ב |

32 |

UART, USART |

20 KB |

- |

WDT |

תרשים בלוק פונקציונלי של AT89S52-24PU

התרשים שלהלן ממחיש את מבנה החסימה הפונקציונלי של AT89S52-24PU.

תכנות זיכרון הפלאש (מצב מקביל)

האיור שלהלן ממחיש את תהליך תכנות זיכרון הפלאש של AT89S52-24PU במצב מקביל.

אימות זיכרון הפלאש (מצב מקביל)

האיור שלהלן מדגים את התהליך של אימות זיכרון הפלאש במצב מקביל עבור AT89S52-24PU.

הורדה סדרתית זיכרון פלאש

האיור שלהלן ממחיש את תהליך ההורדה הסדרתי עבור זיכרון הפלאש AT89S52-24PU.

אלטרנטיבות של AT89S52-24PU

|

מספר חלק |

תֵאוּר |

יַצרָן |

|

AT87F52-24PC |

בקר מיקרו, 8 סיביות, פלאש, 8051 מעבד, 24MHz, CMOS,

PDIP40, 0.600 אינץ ', פלסטיק, DIP-40 |

תאגיד Atmel |

|

AT87F52-24PI |

בקר מיקרו, 8 סיביות, פלאש, 8051 מעבד, 24MHz, CMOS,

PDIP40, 0.600 אינץ ', פלסטיק, DIP-40 |

תאגיד Atmel |

|

AT87F52-24PL |

בקר מיקרו, 8 סיביות, פלאש, 24 מגהרץ, CMOS, PDIP40, 0.600

אינץ ', פלסטיק, DIP-40 |

תאגיד Atmel |

יישומים של AT89S52-24PU

• ניטור שירותי בריאות: משפר את הדיוק במכשירי ניטור רפואי.

• בטיחות רכב: משלב תכונות כמו בקרת שיוט אדפטיבית וסיוע בנתיב.

• אלקטרוניקה DIY: מאפשרת לתחביבים ליצור מכשירים בהתאמה אישית.

• אלקטרוניקה צרכנית: מייצרת מוצרים רב -פונקציונליים ואינטואיטיביים.

• בתים וערים חכמות: משפר את תקשורת המכשירים לניהול אנרגיה ונוחות טובים יותר.

חבילה עבור AT89S52-24PU

AT89S52-24PU מידע על יצרן

Microchip Technology Inc., עם המטה שלה השוכן בצ'נדלר, אריזונה, ממלא תפקיד בתעשיית המיקרו -בקר והתעשייה למוליכים למחצה.החברה נבדלת על ידי המסירות האיתנה שלה להתקדמות חלוצית ושמירה על סטנדרטים גבוהים באמצעות קווי מוצרים המוכרים בזכות אמינותם, אשר מחזקים את יעילות הפיתוח והזהירות הכלכלית.על ידי עיון בקפידה של תהליכי העיצוב והייצור שלה, מיקרו -שבב לא רק נפגש אלא עולה על מדדי התעשייה, ומטפח תפאורה המעודדת שיפור ושכלול מערכות מתמשך.Microchip Technology Inc. היא הרבה יותר מספק של בקרי מיקרו ומוליכים למחצה;זה מעצב באופן פעיל את הנוף בו טכנולוגיות אלה מפותחות ומשמשות.הדגש האסטרטגי שלה על יעילות, ניהול עלויות ובקרת איכות מציב אותו בחלל הענף.

גיליון נתונים PDF

AT89S52-24PU גיליונות נתונים:

חוט מליטה נחושת 17/אוקטובר/2013.pdf

AT89C55WD-24PU גיליונות נתונים:

העבר למיקרו -צ'יפ/תווית/PKG 5/SEP/2016.PDF

העבר למיקרו -צ'יפ/תווית/PKG 5/SEP/2016.PDF

AT89S51-24PU גיליונות נתונים:

חוט מליטה נחושת 17/אוקטובר/2013.pdf

AT89C51RC-24PU גיליונות נתונים:

MBB/תווית CHGS 16/NOV/2018.PDF

עלינו

ALLELCO LIMITED

קרא עוד

חקירה מהירה

אנא שלח בירור, נגיב מייד.

שאלות נפוצות [FAQ]

1. איך AT89S51 ו- AT89S52 נבדלים?

ההבדל העיקרי מתרכז בגודל זיכרון הפלאש שלהם: AT89S51 מצויד ב- 4K ואילו AT89S52 מרחיב את זה ל- 8K.הרחבה זו תומכת ביישומים מתוחכמים יותר ובאחסון של בסיסי קוד נרחבים, תוך התאמה לצרכים מגוונים בפיתוח מערכות משובצות.

2. מהם היישומים של AT89S52?

AT89S52 משמש במספר משימות בקרה משובצות, המוערכות לעתים קרובות ליעילות אנרגטית וביצועים אמינים.הרבגוניות שלה הופכת אותה לעיתים קרובות לאופציה מועדפת בפרויקטים המכוונים לעלות יעילות תוך שמירה על פונקציונליות, תוך התאמה לחדשנות איזון עם שיקולים פיננסיים.

3. האם אתה יכול לפרט ב- AT89S52-24PU?

זהו בקר מיקרו CMOS של 8 סיביות, הידוע בזכות מיזוג יכולות חישוב וזיכרון ליחידה קומפקטית.תכונות אלה מפתות בתהליכי תכנון יעילים בהם היעילות והמרחב חשובים.

4. מדוע ניתן לתכנן מחדש את AT89S52-24PU לתכנות מחדש?

זיכרון פלאש על השבב מאפשר תכנות מחדש, מציע יכולת הסתגלות לעדכוני תוכנה ופיתוח איטרטיבי.תכונה זו משלימה נקודת מבט של התפתחות מודרנית בה שיפורים מתמשכים לא רק אפשריים אלא מתקבלים בברכה.

5. איזו תצורה משלבת מעבד 8 סיביות עם זיכרון פלאש?

ה- AT89S52-24PU מדגים את השילוב הזה, שם מעבד 8 סיביות הרמוני עם זיכרון פלאש.שילוב זה מספק עיבוד ואחסון יעילים ליישומים הדורשים פעולות חזקות ללא עודף.

6. איזה גודל של זיכרון פלאש הוא בעל?

זה כולל 8K בתים של פלאש, המאפשר ניהול נתוני התוכנית.הרחבה זו הופכת אותו למתאים למשימות מאתגרות בהן זיכרון מוגבל יכול להוות מכשולים.

7. כיצד AT89S52 מטפלת בפעולה בתדר נמוך?

היגיון סטטי כלול, המאפשר פעולה בתדרים נמוכים עם יעילות.מאפיין זה משמש בתרחישים הדורשים שימוש בכוח מינימלי, ומשפר הן את אריכות החיים והן את הקיימות באלקטרוניקה.

8. מתי המעבד הופך לא פעיל?

מצב סרק הופך את ה- CPU לבלתי פעיל, ומשיג חיסכון באנרגיה תוך שמירה על פונקציות מיקרו -בקר.תכנון אסטרטגי זה ממזער את השימוש באנרגיה בתקופות של עיבוד פחות אינטנסיבי.

9. איזה מצב שומר על שלמות ה- RAM?

תכולת ה- RAM נשארת שלמה במהלך מצב ההפעלה, ומאפשרת שימור נתונים למרות צריכת החשמל המופחתת.פונקציונליות זו טובה בתנאים המחייבים שמירת נתונים לצד שימוש מינימלי באנרגיה, אופיינית במכשירים המונעים על סוללות.

KSZ9031RNXIA Gigabit Ethernet משדר: Pinout, Alternativ

ב- 2024/11/22

חקר ה- FOD3180 Optocupler

ב- 2024/11/22

פוסטים פופולריים

-

מחשבים מערכי הוראות מורכבים: כיצד הם שינו מחשוב?

ב- 8000/04/18 147776

-

Pinout USB-C ותכונות

ב- 2000/04/18 112022

-

שימוש בפרימיטיביות סימולציה אחידות של Xilinx: מדריך מקיף לעיצוב וסימולציה של FPGA

ב- 1600/04/18 111351

-

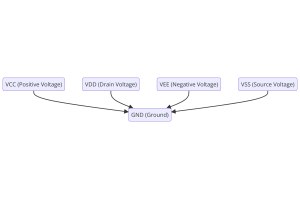

מתחי אספקת חשמל באלקטרוניקה: המשמעות של VCC, VDD, VEE, VSS ו-GND

ב- 0400/04/18 83777

-

מדריך מחברים RJ45: Pinout, חיווט, סוגי כבלים ושימושים

ב- 1970/01/1 79577

-

המדריך האולטימטיבי לקודי צבע חוט במערכות חשמל מודרניות

האופן בו מערכות החשמל שלנו משתמשות בצבעים אינן רק למראה.כל צבע חוט מציין כעת פונקציה ספציפית, מה שמקל על זיהוי וטיפול נכון ברכיבים חשמליים במהלך ההתקנה והתחזוקה.זה לא רק מזרז תהליכים תפעוליים אלא ג...ב- 1970/01/1 66964

-

מדריך שסתומי טיהור: תפקוד, תסמינים, בדיקה והחלפה לביצועי מנוע מיטביים

שסתום הטיהור הוא חלק מרכזי במערכת המכונית המסייעת לשמור על נקייה של האוויר על ידי ניהול אדי דלק לפני שהם יכולים לברוח לאטמוספרה.זה לא רק מסייע לסביבה על ידי הפחתת הזיהום, אלא גם משפר את המכונית ומש...ב- 1970/01/1 63104

-

גורם איכותי (ש) גורם: משוואות ויישומים

גורם האיכות, או 'Q', חשוב בבדיקת עד כמה משרנים ומהודדים עובדים במערכות אלקטרוניות המשתמשות בתדרי רדיו (RF).'Q' מודד עד כמה מעגל מצמצם את אובדן האנרגיה ומשפיע על טווח התדרים שהמערכת יכולה להתמודד עם...ב- 1970/01/1 63041

-

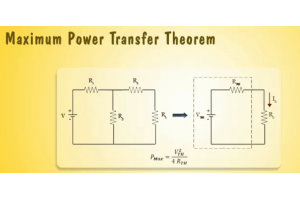

השגת ביצועי שיא עם משפט העברת הכוח המרבי

משפט העברת הכוח המרבי מסביר כיצד אנרגיה ממקור, כמו סוללה או גנרטור, זורמת לעומס מחובר.זה מראה את התנאי המדויק בו העומס מקבל הכי הרבה כוח.מאמר זה מכסה את המשמעות של משפט, כיצד הוא עובד במעגלי DC וגם...ב- 1970/01/1 54097

-

מפרטי סוללה A23 ותאימות

סוללת A23 היא סוללה קטנה בצורת צילינדר עם מתח גבוה.נקרא גם 23A, 23AE או MN21, הוא פועל ב 12 וולט וגבוה בהרבה מסוללות AA או AAA.העיצוב המיוחד שלו הופך אותו למושלם לגאדג'טים הזקוקים למקור כו...ב- 1970/01/1 52190