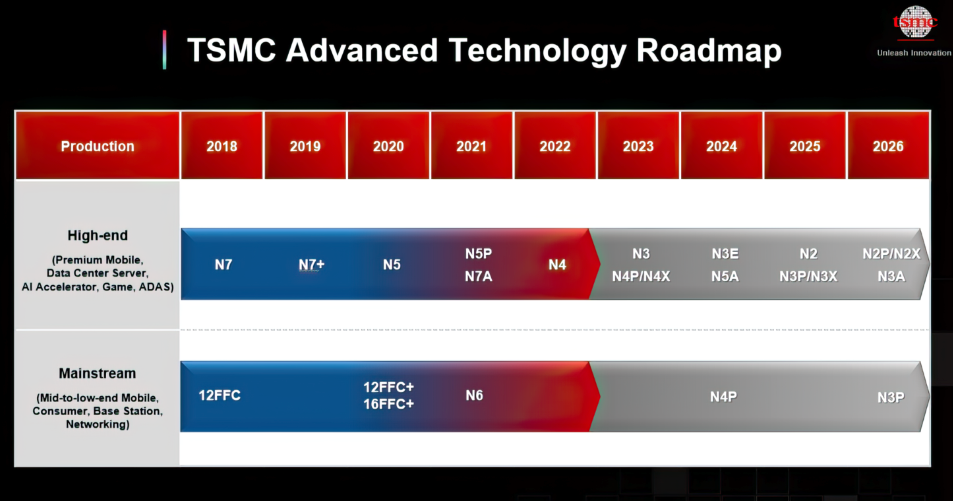

הדור השלישי של TSMC צומת 3NM נמצא על המסלול, ו- N3P יופק המוני בהמשך השנה

TSMC החלה בהצלחה להשתמש בטכנולוגיית התהליכים ברמת 3NM מהדור השני כדי לייצר שבבים ברבעון הרביעי של 2023, והשיגה את אבן הדרך המתוכננת.החברה מתכוננת כעת לייצור המוני שבבי N3P המשופרים לביצועים עבור צומת זה.TSMC הודיעה בסימפוזיון הטכנולוגי האירופי כי הדבר יתקיים במחצית השנייה של 2024.

תהליך ה- N3E נכנס לייצור המוני כמתוכנן, וצפיפות הפגמים דומה לתהליך ה- N5 במהלך ייצור המוני בשנת 2020. TSMC מתאר את התשואה של N3E כ- "גדול", וכיום המעבד היחיד המשתמש ב- N3E - Apple M4- יש משמעותיתהגדיל את מספר הטרנזיסטורים ומהירות השעון ההפעלה בהשוואה ל- M3 על בסיס טכנולוגיית N3.

מנהל TSMC אמר באירוע, "N3E החל בייצור המוני כמתוכנן ברבעון הרביעי של השנה שעברה. ראינו ביצועי ייצור מצוינים ממוצרי הלקוחות שלנו, כך שהם אכן נכנסו לשוק כמתוכנן."

מנהל TSMC אמר באירוע, "N3E החל בייצור המוני כמתוכנן ברבעון הרביעי של השנה שעברה. ראינו ביצועי ייצור מצוינים ממוצרי הלקוחות שלנו, כך שהם אכן נכנסו לשוק כמתוכנן."

פרט המפתח בתהליך N3E הוא הפשט שלו בהשוואה לתהליך ה- N3 של הדור הראשון של TSMC (הידוע גם בשם N3B).על ידי הסרת כמה שכבות הדורשות ליטוגרפיה של EUV והימנעות לחלוטין מהשימוש בדפוס כפול של EUV, N3E מפחית את עלויות הייצור, מרחיב את חלון התהליך ומשפר את התשואה.עם זאת, שינויים אלה מפחיתים לעיתים את צפיפות הטרנזיסטור ואת יעילות הכוח, סחר שניתן להקטין באמצעות אופטימיזציה של תכנון.

במבט קדימה, תהליך ה- N3P מספק קנה מידה אופטי עבור N3E ומראה גם התקדמות מבטיחה.זה עבר את הסמכת ההסמכה הדרושה ומציג ביצועי תפוקה קרובים ל- N3E.ההתפתחות הבאה של תיק הטכנולוגיה של TSMC שמה לה למטרה לשפר את הביצועים בעד 4% או להפחית את צריכת החשמל בכ- 9% באותה מהירות שעון, תוך הגדלת צפיפות הטרנזיסטור של שבבי תצורת עיצוב היברידיים ב -4%.

N3P שומר על תאימות למודולי ה- IP, כלי העיצוב והשיטות של N3E, מה שהופך אותו לבחירה אטרקטיבית עבור המפתחים.המשכיות זו מבטיחה שרוב עיצובי השבבים החדשים (CHIPs) צפויים לעבור משימוש ב- N3E ל- N3P, וממנפים את הביצועים המשופרים ויעילות העלות של האחרון.

עבודות הכנת הייצור הסופיות עבור N3P צפויות להתקיים במחצית השנייה של השנה, אז היא תיכנס לשלב HVM (ייצור המוני).TSMC מצפה מעצבי שבבים לאמץ אותו מייד.בהתחשב ביתרונות הביצועים והעלות שלה, N3P צפויה להיות מועדפת על ידי לקוחות TSMC, כולל אפל ו- AMD.

למרות שתאריך ההשקה המדויק של שבבים מבוססי N3P עדיין לא בטוח, צפוי כי יצרנים גדולים כמו אפל ישתמשו בטכנולוגיה זו בסדרת המעבדים שלהם עד שנת 2025, כולל SOC לסמארטפונים, מחשבים אישיים וטאבלטים.

"סיפקנו בהצלחה טכנולוגיית N3P", אמרנו מנהלי TSMC."זה היה מוסמך וביצועי התשואה שלו קרובים ל- N3E. (טכנולוגיית תהליכים) קיבלה גם את הוופלים של לקוחות המוצר והייצור יחל במחצית השנייה של השנה. בגלל N3P (יתרון PPA), אנו מצפים לרובפלים ב- N3 כדי לזרום לכיוון N3P. "

במבט קדימה, תהליך ה- N3P מספק קנה מידה אופטי עבור N3E ומראה גם התקדמות מבטיחה.זה עבר את הסמכת ההסמכה הדרושה ומציג ביצועי תפוקה קרובים ל- N3E.ההתפתחות הבאה של תיק הטכנולוגיה של TSMC שמה לה למטרה לשפר את הביצועים בעד 4% או להפחית את צריכת החשמל בכ- 9% באותה מהירות שעון, תוך הגדלת צפיפות הטרנזיסטור של שבבי תצורת עיצוב היברידיים ב -4%.

N3P שומר על תאימות למודולי ה- IP, כלי העיצוב והשיטות של N3E, מה שהופך אותו לבחירה אטרקטיבית עבור המפתחים.המשכיות זו מבטיחה שרוב עיצובי השבבים החדשים (CHIPs) צפויים לעבור משימוש ב- N3E ל- N3P, וממנפים את הביצועים המשופרים ויעילות העלות של האחרון.

עבודות הכנת הייצור הסופיות עבור N3P צפויות להתקיים במחצית השנייה של השנה, אז היא תיכנס לשלב HVM (ייצור המוני).TSMC מצפה מעצבי שבבים לאמץ אותו מייד.בהתחשב ביתרונות הביצועים והעלות שלה, N3P צפויה להיות מועדפת על ידי לקוחות TSMC, כולל אפל ו- AMD.

למרות שתאריך ההשקה המדויק של שבבים מבוססי N3P עדיין לא בטוח, צפוי כי יצרנים גדולים כמו אפל ישתמשו בטכנולוגיה זו בסדרת המעבדים שלהם עד שנת 2025, כולל SOC לסמארטפונים, מחשבים אישיים וטאבלטים.

"סיפקנו בהצלחה טכנולוגיית N3P", אמרנו מנהלי TSMC."זה היה מוסמך וביצועי התשואה שלו קרובים ל- N3E. (טכנולוגיית תהליכים) קיבלה גם את הוופלים של לקוחות המוצר והייצור יחל במחצית השנייה של השנה. בגלל N3P (יתרון PPA), אנו מצפים לרובפלים ב- N3 כדי לזרום לכיוון N3P. "