Order

Now

DAC8742H SBAS940 – DECEMBER 2018

# DAC8742H, HART and FOUNDATION Fieldbus / PROFIBUS PA Modem

## 1 Features

- HART-Compliant Physical Layer Modem

- 1200/2200 Hz HART FSK Sinusoids

- Register Programmable Amplitude of TX Signals

- (DAC8741H / DAC8742H only)

- Integrated RX Demodulator and Band-Pass

Filter with Minimal External Components

- FOUNDATION Fieldbus Compatible H1 Controller and Medium Attachment Unit (MAU)

- 31.25 kbit/s Communication Based on Manchester Coded Bus Powered (MBP)

- Integrated Manchester Encoder and Decoder

- Compatible with PROFIBUS PA

- Low Quiescent Current: 180 uA Max at Typical Industrial Operating Temperature Range (-40°C to 85°C)

- Integrated 1.5-V Reference

- Flexible Clocking Options

- Internal Oscillator

- External Crystal Oscillator

- External CMOS Clock

- Digital Interface

- DAC8742H: UART and SPI

- Reliability: CRC Bit Error Checking, Watchdog Timer

- Wide Operating Temperature: -55°C to 125°C

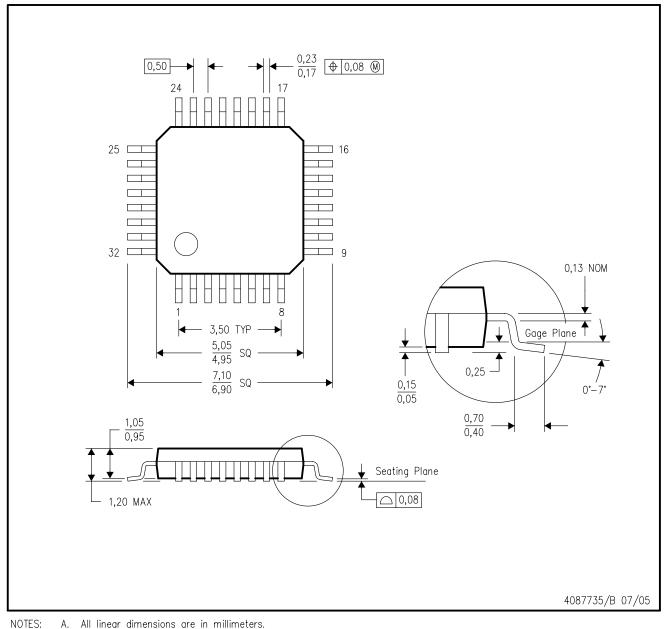

- 5 mm x 5 mm TQFP Package

## 2 Applications

- Industrial Process Control and Automation

- PLC or DCS I/O Modules

- Field and Sensor Transmitters

## 3 Description

The DAC8742H is a HART<sup>®</sup>, FOUNDATION Fieldbus<sup>™</sup>, and PROFIBUS PA compatible low power modem designed for industrial process control and industrial automation applications.

In HART mode, the DAC8742H integrates all of the required circuitry to operate as half-duplex HART physical layer modems, in either slave or master configurations with minimal external components for filtering. In FOUNDATION Fieldbus mode, the DAC8742H integrates all of the required circuitry to operate as half-duplex FOUNDATION Fieldbus compatible H1 Controllers and MAUs.

The HART, FOUNDATION Fieldbus, or PROFIBUS PA, data stream can be transferred from the microcontroller through either a UART interface or an integrated FIFO accessed by a SPI interface. The SPI interface includes an SDO pin for daisy-chain support, various interrupts, and other extended features.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM) |

|-------------|-----------|-----------------|

| DAC8742H    | TQFP (32) | 5 mm × 5 mm     |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

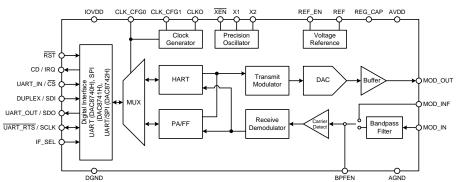

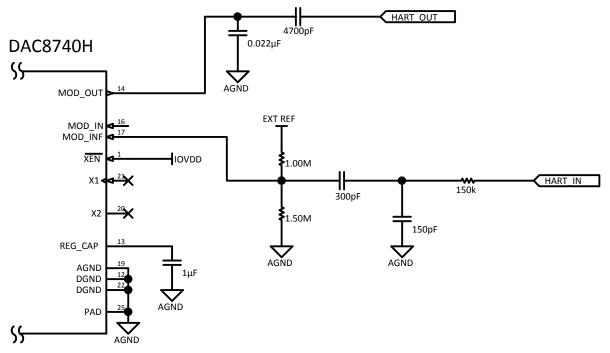

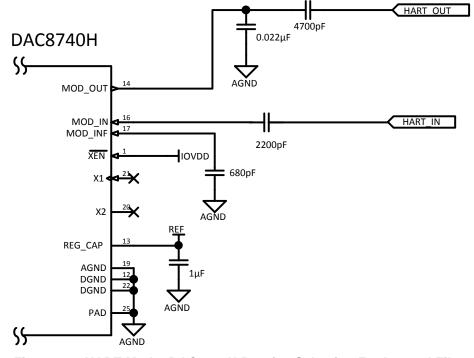

### Simplified Schematic

Texas Instruments

www.ti.com

## **Table of Contents**

| 1 | Feat | tures                            | 1    |

|---|------|----------------------------------|------|

| 2 | Арр  | lications                        | 1    |

| 3 | Des  | cription                         | 1    |

| 4 | Rev  | ision History                    | 2    |

| 5 | Pin  | Configuration and Functions      | 3    |

| 6 | Spe  | cifications                      | 5    |

|   | 6.1  | Absolute Maximum Ratings         | 5    |

|   | 6.2  | ESD Ratings                      | 5    |

|   | 6.3  | Recommended Operating Conditions | 5    |

|   | 6.4  | Thermal Information              |      |

|   | 6.5  | Electrical Characteristics       |      |

|   | 6.6  | Timing Requirements              | 9    |

|   | 6.7  | Typical Characteristics          | . 10 |

| 7 | Deta | ailed Description                | . 14 |

|   | 7.1  | Overview                         | . 14 |

|   | 7.2  | Functional Block Diagram         | . 14 |

|   | 7.3  | Feature Description              | . 14 |

|   |      |                                  |      |

|    | 7.4  | Device Functional Modes                         | 17 |

|----|------|-------------------------------------------------|----|

|    | 7.5  | Register Maps                                   | 21 |

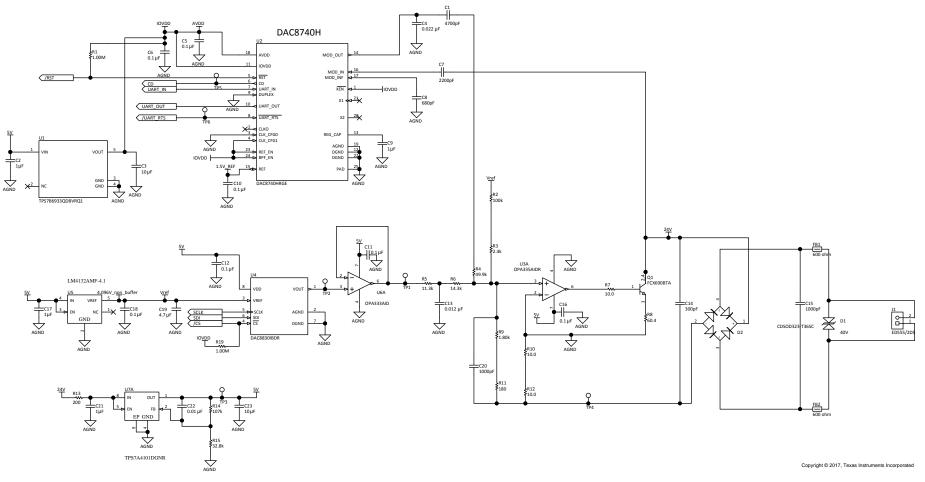

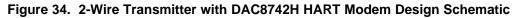

| 8  | Арр  | lication and Implementation                     | 28 |

|    | 8.1  | Application Information                         | 28 |

|    | 8.2  | Typical Application                             | 30 |

| 9  | Pow  | er Supply Recommendations                       | 34 |

| 10 | Lay  | out                                             | 35 |

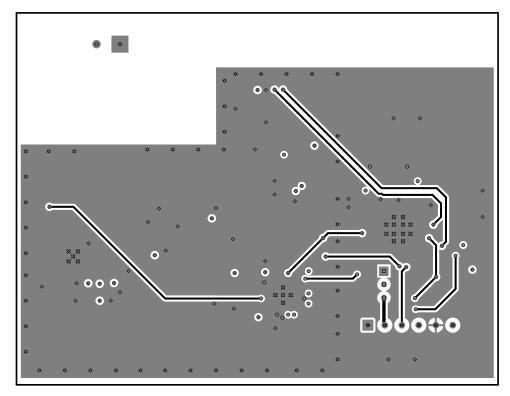

|    | 10.1 | Layout Guidelines                               | 35 |

|    | 10.2 | Layout Example                                  | 35 |

| 11 | Dev  | ice and Documentation Support                   | 37 |

|    | 11.1 | Documentation Support                           | 37 |

|    | 11.2 | Receiving Notification of Documentation Updates | 37 |

|    | 11.3 | Community Resources                             | 37 |

|    | 11.4 | Trademarks                                      | 37 |

|    | 11.5 | Electrostatic Discharge Caution                 | 37 |

|    | 11.6 | Glossary                                        | 37 |

| 12 |      | hanical, Packaging, and Orderable               |    |

|    | Info | rmation                                         | 37 |

|    |      |                                                 |    |

## 4 Revision History

| DATE          | REVISION | NOTES                                              |

|---------------|----------|----------------------------------------------------|

| December 2018 | *        | Initial release of DAC8742H standalone data sheet. |

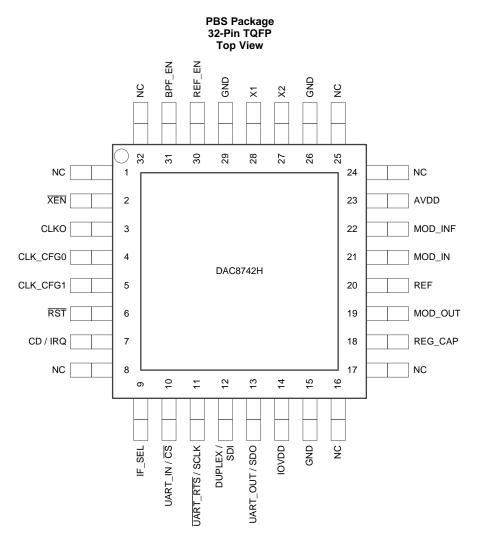

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN      |     | 1/0               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |

|----------|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO. | I/O               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |

| XEN      | 2   | Digital<br>Input  | Crystal Oscillator Enable. Logic low on this pin enables the crystal oscillator circuit; in this mode<br>an external crystal is required. Logic high on this pin disables the internal crystal oscillator<br>circuit; in this mode an external CMOS clock or the internal oscillator are required. No digital<br>input pin should be left floating. |  |

| CLKO     | 3   | Digital<br>Output | Clock Output. If using the internal oscillator or an external crystal, this pin can be configured as a clock output.                                                                                                                                                                                                                                |  |

| CLK_CFG0 | 4   | Digital<br>Input  | Clock Configuration Pin. This pin is used to configure the input/output clocking scheme. No digital input pin should be left floating.                                                                                                                                                                                                              |  |

| CLK_CFG1 | 5   | Digital<br>Input  | Clock Configuration Pin. This pin is used to configure the input/output clocking scheme. No digital input pin should be left floating.                                                                                                                                                                                                              |  |

| RST      | 6   | Digital<br>Input  | Reset. Logic low on this pin places the DAC8742H into power-down mode and resets the device. Logic high returns the device to normal operation. No digital input pin should be left floating.                                                                                                                                                       |  |

Texas Instruments

## Pin Functions (continued)

| PIN             |     |                              | DECODIPTION                                                                                                                                                                                                                                   |                                                                                 |                                                                                                                                                                                                                                         |  |  |

|-----------------|-----|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME            | NO. | - I/O                        |                                                                                                                                                                                                                                               |                                                                                 | DESCRIPTION                                                                                                                                                                                                                             |  |  |

|                 |     |                              | UART                                                                                                                                                                                                                                          | HART<br>Mode                                                                    | Carrier detect. A logic high on this pin indicates a valid carrier is present.                                                                                                                                                          |  |  |

| CD / IRQ        | 7   | Digital<br>Output            | Mode                                                                                                                                                                                                                                          | FF / PA<br>Mode                                                                 | While not transmitting, a logic high on this pin indicates a valid carrier is present. While transmitting, a logic high on this pin indicates that the jabber inhibitor has triggered.                                                  |  |  |

|                 |     |                              | SPI Mode Digital Interrupt. The interrupt can be configured as edge sensitive or level set with positive or negative polarity, as set by the CONTROL register. Events the trigger an interrupt are controlled by the Modem IRQ Mask register. |                                                                                 |                                                                                                                                                                                                                                         |  |  |

| IF_SEL          | 9   | Digital<br>Input             | pin configu                                                                                                                                                                                                                                   |                                                                                 | high on this pin configures the device for SPI mode. A logic low on this<br>the for UART mode. An internal pull-down resistor is included. No digital<br>floating.                                                                      |  |  |

|                 |     |                              | UART<br>Mode                                                                                                                                                                                                                                  | UART data                                                                       | input.                                                                                                                                                                                                                                  |  |  |

| UART_IN /<br>CS | 10  | Digital<br>Input             | SPI Mode                                                                                                                                                                                                                                      | When CS i                                                                       | elect. Data bits are clocked into the serial shift register when CS is low.<br>s high, SDO is in a high-impedance state and data on SDI are ignored.<br>nput pin should be left floating. No digital input pin should be left floating. |  |  |

| UART RTS/       |     | Digital<br>Input,            | UART<br>Mode                                                                                                                                                                                                                                  | HART<br>Mode                                                                    | Request to send a logic high on this pin enables the demodulator and disables the modulator. A logic low on this pin enables the modulator and disables the demodulator. No digital input pin should be left floating.                  |  |  |

| SCLK            | 11  | Digital<br>Output            |                                                                                                                                                                                                                                               | FF / PA<br>Mode                                                                 | This pin reports transmit FIFO threshold information as programmed by the packet initiation code.                                                                                                                                       |  |  |

|                 |     |                              | SPI Mode                                                                                                                                                                                                                                      | SPI clock. input.                                                               | Data can be transferred at rates up to 12.5MHz. Schmitt-Trigger logic                                                                                                                                                                   |  |  |

|                 |     |                              | UART<br>Mode                                                                                                                                                                                                                                  | I lightal input I odic high enables tull-dupley or internal loop-back test mode |                                                                                                                                                                                                                                         |  |  |

| DUPLEX / SDI    | 12  | Digital<br>Output            | SPI Mode SPI data input. Data is clocked into the 24-bit input shift register on the falling edg of the serial clock input. Schmitt-Trigger logic input.                                                                                      |                                                                                 |                                                                                                                                                                                                                                         |  |  |

| UART_OUT /      | 13  | Digital                      | UART<br>Mode                                                                                                                                                                                                                                  | UART data                                                                       | output.                                                                                                                                                                                                                                 |  |  |

| SDO             |     | Output                       | SPI Mode                                                                                                                                                                                                                                      | SPI data or                                                                     | utput. Data is valid on the falling edge of SCLK.                                                                                                                                                                                       |  |  |

| IOVDD           | 14  | Supply                       |                                                                                                                                                                                                                                               | upply. Supply<br>for the digita                                                 | / voltage for digital input and output circuitry. This voltage sets the logical l interface.                                                                                                                                            |  |  |

| GND             | 15  | Supply                       | Digital grou                                                                                                                                                                                                                                  | Ind. Ground                                                                     | reference voltage for all digital circuitry of the device.                                                                                                                                                                              |  |  |

| REG_CAP         | 18  | Analog<br>Output             | Capacitor f                                                                                                                                                                                                                                   | or internal re                                                                  | gulator.                                                                                                                                                                                                                                |  |  |

| MOD_OUT         | 19  | Analog<br>Output             | FOUNDAT                                                                                                                                                                                                                                       | ION Fieldbus                                                                    | put sinusoid in HART mode or Manchester coded data stream in<br>s and PROFIBUS PA modes. Requires parallel capacitance of 5-22 nF in<br>F in FOUNDATION Fieldbus and PROFIBUS PA mode for stability.                                    |  |  |

| REF             | 20  | Analog<br>Input<br>or Output |                                                                                                                                                                                                                                               |                                                                                 | ence is enabled this pin outputs the internal reference voltage. When the abled, this is the external 2.5V reference input.                                                                                                             |  |  |

| MOD_IN          | 21  | Analog<br>Input              |                                                                                                                                                                                                                                               |                                                                                 | UNDATION Fieldbus and PROFIBUS PA Manchester coded data stream r is used, do not connect this pin.                                                                                                                                      |  |  |

| MOD_INF         | 22  | Analog<br>Input              | If using the Fieldbus ar this pin.                                                                                                                                                                                                            | internal ban<br>nd PROFIBU                                                      | d-pass filter, connect 680 pF to this pin or 120 pF in FOUNDATION S PA modes. If using an external filter, connect the output of that filter to                                                                                         |  |  |

| AVDD            | 23  | Supply                       | Power supply.                                                                                                                                                                                                                                 |                                                                                 |                                                                                                                                                                                                                                         |  |  |

| GND             | 26  | Supply                       | Analog gro                                                                                                                                                                                                                                    | und. Ground                                                                     | reference voltage for power supply input.                                                                                                                                                                                               |  |  |

| X2              | 27  | Analog<br>Input              | Crystal stim                                                                                                                                                                                                                                  | nulus.                                                                          |                                                                                                                                                                                                                                         |  |  |

| X1              | 28  | Analog<br>Input              | Crystal/Clo                                                                                                                                                                                                                                   | ck input.                                                                       |                                                                                                                                                                                                                                         |  |  |

| GND             | 29  | Supply                       | Digital ground. Ground reference voltage for all digital circuitry of the device.                                                                                                                                                             |                                                                                 |                                                                                                                                                                                                                                         |  |  |

| REF_EN          | 30  | Digital<br>Input             | Reference<br>left floating                                                                                                                                                                                                                    |                                                                                 | c high enables the internal 1.5V reference. No digital input pin should be                                                                                                                                                              |  |  |

#### **Pin Functions (continued)**

| PIN    |                                | 1/0              | DESCRIPTION                                                                                                      |  |  |

|--------|--------------------------------|------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO.                            | I/O              | DESCRIPTION                                                                                                      |  |  |

| BPF_EN | 31                             | Digital<br>Input | Filter enable. A logic high enables the internal band-pass filter. No digital input pin should be left floating. |  |  |

| NC     | 1, 8, 16,<br>17,<br>24, 25, 32 | -                | Do not connect these pins.                                                                                       |  |  |

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |                                             | MIN  | MAX       | UNIT |

|------------------------------------------------|---------------------------------------------|------|-----------|------|

|                                                | AVDD to GND                                 | -0.3 | 6         |      |

| Innut voltogo                                  | IOVDD to GND                                | -0.3 | 6         | V    |

| Input voltage                                  | Analog output voltage to GND                | -0.3 | AVDD+0.3  | V    |

|                                                | Digital output voltage to GND               | -0.3 | IOVDD+0.3 |      |

| Output walte as                                | Analog output pin to GND                    | -0.3 | AVDD+0.3  | V    |

| Output voltage                                 | Digital output pin to GND                   | -0.3 | IOVDD+0.3 | V    |

| Input Current                                  | Input current to any pin except supply pins | -10  | 10        | mA   |

| Operating junction temperature, T <sub>J</sub> |                                             | -55  | 125       |      |

| Junction temperature range (TJ max)            |                                             |      | 150       | °C   |

| Storage temperat                               | ure, T <sub>stg</sub>                       | -60  | 150       |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±8000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                                        |                  | MIN    | NOM    | MAX    | UNIT |

|----------------------------------------|------------------|--------|--------|--------|------|

| POWER SUPPL                            | Y                |        |        |        |      |

| AVDD                                   |                  | 2.7    |        | 5.5    | V    |

| IOVDD                                  |                  | 1.71   |        | 5.5    | V    |

| ANALOG INPUT                           | S                |        |        |        |      |

| External<br>Reference Input<br>Voltage |                  | 2.375  | 2.5    | 2.625  | V    |

| DIGITAL INPUT                          | S                |        |        |        |      |

| External Clock                         | 3.6864 MHz Clock | 3.6469 | 3.6864 | 3.7232 | MHz  |

| Source<br>Frequency<br>(HART Mode)     | 1.2288 MHz Clock | 1.2165 | 1.2288 | 1.2411 | MHz  |

## **Recommended Operating Conditions (continued)**

Over operating free-air temperature range (unless otherwise noted)

|                                                          | MIN  | NOM | MAX  | UNIT |

|----------------------------------------------------------|------|-----|------|------|

| External Clock<br>Source<br>Frequency (FF /<br>PA Modes) | 3.96 | 4   | 4.04 | MHz  |

### 6.4 Thermal Information

|                       |                                              | DAC8742H   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PBS (TQFP) | UNIT |

|                       |                                              | 32 PIN     |      |

| $R_{	heta JA}$        | Junction-to-ambient thermal resistance       | 79.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 19.3       | °C/W |

| $R_{	heta JB}$        | Junction-to-board thermal resistance         | 33.2       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.5        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 32.9       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

All specifications over -40°C to +125°C ambient operating temperature,  $2.7V \le AVDD \le 5.5V$ ,  $1.71V \le IOVDD \le 5.5V$ , Internal Reference, Internal Filter, unless otherwise noted.

| PARAMETER           | TEST CONDITIONS                                                | MIN  | TYP | MAX | UNIT |

|---------------------|----------------------------------------------------------------|------|-----|-----|------|

| POWER REQUIRE       | MENTS                                                          |      |     |     |      |

| IOVDD               |                                                                | 1.71 |     | 5.5 | V    |

| AVDD                |                                                                | 2.7  |     | 5.5 | V    |

| AVDD and IOVDD      | Supply Current (HART Mode)                                     |      |     |     |      |

|                     | External Clock, -40°C to 85°C                                  |      | 110 | 150 | μA   |

| Demodulator active  | External Clock, -55°C to 125°C                                 |      |     | 220 | μA   |

| Demodulator active  | External Clock, -40°C to 85°C, External Reference              |      | 100 | 140 | μA   |

|                     | External Clock, -55°C to 125°C, External Reference             |      |     | 210 | μA   |

|                     | External Clock, -40°C to 85°C                                  |      | 160 | 180 | μA   |

| Madulator activa    | External Clock, -55°C to 125°C                                 |      |     | 250 | μA   |

| Modulator active    | External Clock, -40°C to 85°C, External Reference              |      | 150 | 170 | μA   |

|                     | External Clock, -55°C to 125°C, External Reference             |      |     | 240 | μA   |

|                     | External Crystal, 16pF at XTAL1 and XTAL2                      |      | 40  | 65  | μA   |

| Crystal Oscillator  | External Crystal, 36pF at XTAL1 and XTAL2                      |      | 40  | 65  | μA   |

| Internal Oscillator | External Reference                                             |      | 105 | 180 | μA   |

| SPI Interface       | Additional quiescent current required when interfacing via SPI |      | 5   |     | μΑ   |

| AVDD and IOVDD      | Supply Current (FF/PA Mode)                                    |      |     |     |      |

|                     | External Clock, -40°C to 85°C                                  |      | 160 | 220 | μA   |

| Decoder active      | External Clock, -55°C to 125°C                                 |      |     | 330 | μA   |

| Decoder active      | External Clock, -40°C to 85°C, External Reference              |      | 175 | 200 | μA   |

|                     | External Clock, -55°C to 125°C, External Reference             |      |     | 320 | μA   |

|                     | External Clock, -40°C to 85°C                                  |      | 175 | 250 | μA   |

| Encodor octivo      | External Clock, -55°C to 125°C                                 |      |     | 360 | μA   |

| Encoder active      | External Clock, -40°C to 85°C, External Reference              |      | 165 | 235 | μA   |

|                     | External Clock, -55°C to 125°C, External Reference             |      |     | 350 | μA   |

6

## **Electrical Characteristics (continued)**

All specifications over -40°C to +125°C ambient operating temperature,  $2.7V \le AVDD \le 5.5V$ ,  $1.71V \le IOVDD \le 5.5V$ , Internal Reference, Internal Filter, unless otherwise noted.

|                                    | I Fliter, unless otherwise hoted.                                                                                                                   |        |        | BAAN   |            |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|------------|

| PARAMETER                          |                                                                                                                                                     | MIN    | TYP    | MAX    | UNIT<br>μA |

| Crystal Oscillator                 | External Crystal, 16pF at XTAL1 and XTAL24065External Crystal, 36pF at XTAL1 and XTAL24065                                                          |        |        |        |            |

|                                    | External Crystal, 36pF at XTAL1 and XTAL2                                                                                                           |        | 40     | 65     | μA         |

| SPI Interface                      | Additional quiescent current required when interfacing via SPI                                                                                      |        | 5      |        | μA         |

| AVDD and IOVDD S                   | Supply Current (All Modes)                                                                                                                          |        |        |        |            |

| Power-Down Mode                    | Internal reference disabled, -40°C to 85°C, no active clock input                                                                                   |        | 30     | 60     | μΑ         |

| Power-Down Mode                    | Internal reference disabled, -55°C to 125°C, no active clock input                                                                                  |        |        | 182    | μA         |

| CLOCK REQUIREM                     | IENTS                                                                                                                                               |        |        |        |            |

| EXTERNAL CLOCK                     | (HART MODE)                                                                                                                                         |        |        |        |            |

| External Clock                     | 3.6864 MHz Clock                                                                                                                                    | 3.6469 | 3.6864 | 3.7232 | MHz        |

| Source Frequency                   | 1.2288 MHz Clock                                                                                                                                    | 1.2165 | 1.2288 | 1.2411 | MHz        |

| EXTERNAL CLOCK                     | ( (FF/PA MODE)                                                                                                                                      |        |        |        |            |

| External Clock<br>Source Frequency | 4 MHz Clock                                                                                                                                         | 3.96   | 4      | 4.04   | MHz        |

| NTERNAL OSCILL                     | ATOR                                                                                                                                                |        |        |        |            |

| Frequency                          | -40°C to 125°C                                                                                                                                      | 1.2165 | 1.2288 | 1.2411 | MHz        |

| VOLTAGE REFERE                     |                                                                                                                                                     |        |        |        |            |

| NTERNAL REFERI                     |                                                                                                                                                     |        |        |        |            |

| nternal Reference<br>Voltage       |                                                                                                                                                     | 1.47   | 1.5    | 1.53   | V          |

| Load Regulation                    |                                                                                                                                                     |        | 1.3    |        | V/mA       |

| Capacitive Load                    | Guaranteed by design                                                                                                                                |        | 1      |        | μF         |

| •                                  |                                                                                                                                                     |        | · · ·  |        | P.         |

| External Reference                 |                                                                                                                                                     | 2.375  | 2.5    | 2.625  | V          |

| input voltage                      | Demodulator                                                                                                                                         |        | 4.5    |        | μA         |

|                                    | Modulator                                                                                                                                           |        | 4.5    |        | μΑ         |

| External Reference                 | Internal Oscillator                                                                                                                                 |        | 4.5    |        | μΑ         |

| input Current                      | Power-Down                                                                                                                                          |        | 4.5    |        | μΑ         |

|                                    | Power-Down                                                                                                                                          |        | 4.5    |        | μΑ         |

| MOD IN INPUT (HA                   |                                                                                                                                                     |        |        |        |            |

| Input Voltage                      | External Reference Source, guaranteed by design.<br>Signal applied at the input to the DC blocking<br>capacitor.                                    | 0      |        | 1.5    | Vp-р       |

| Range                              | Internal Reference Source, guaranteed by design.<br>Signal applied at the input to the DC blocking<br>capacitor.                                    | 0      |        | 1.5    | Vp-р       |

| Receiver<br>Sensitivity            | Threshold for successful carrier detection and demodulation, assuming ideal sinusoidal input FSK signals with valid preamble using internal filter. | 80     | 100    | 120    | mVp-p      |

| MOD_OUT OUTPU                      | T (HART MODE)                                                                                                                                       |        |        |        |            |

| Output Voltage                     | AC-coupled (2.2 $\mu F$ ), measured at MOD_OUT pin with 160 $\Omega$ load                                                                           | 450    | 460    | 480    | mVp-p      |

| Mark Frequency                     | Internal Oscillator                                                                                                                                 |        | 1200   |        | Hz         |

| Space Frequency                    | Internal Oscillator                                                                                                                                 |        | 2200   |        | Hz         |

| Frequency Error                    | Internal Oscillator, -40°C to 125°C                                                                                                                 | -1     |        | 1      | %          |

| Phase Continuity<br>Error          | Guaranteed by design                                                                                                                                |        |        | 0      | Degrees    |

## **Electrical Characteristics (continued)**

All specifications over -40°C to +125°C ambient operating temperature,  $2.7V \le AVDD \le 5.5V$ ,  $1.71V \le IOVDD \le 5.5V$ , Internal Reference, Internal Filter, unless otherwise noted.

| PARAMETER                            | TEST CONDITIONS                                                                                                                                                                                                  | MIN            | TYP   | MAX             | UNIT   |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|-----------------|--------|

| Minimum Resistive<br>Load            | 160 $\Omega$ , AC coupled with 2.2 $\mu$ F, guaranteed by design                                                                                                                                                 | 160            |       |                 | Ω      |

| Transmit                             | RTS low, measured at the MOD_OUT pin, 1mA measurement current                                                                                                                                                    |                | 13    |                 | Ω      |

| mpedance                             | RTS high, measured at the MOD_OUT pin, ±200nA measurement current                                                                                                                                                |                | 250   |                 | kΩ     |

| FF / PA MODEM                        |                                                                                                                                                                                                                  |                |       |                 |        |

| MOD_IN INPUT (FF                     | /PA MODE)                                                                                                                                                                                                        |                |       |                 |        |

| nput Voltage                         | External Reference Source, specified by design.<br>Signal applied at the input to the DC blocking<br>capacitor.                                                                                                  | 0              |       | 1               | Vр-р   |

| Range                                | Internal Reference enabled, specified by design.<br>Signal applied at the input to the DC blocking<br>capacitor.                                                                                                 | 0              |       | 1               | Vp-p   |

| Receiver Jitter<br>Tolerance         | Edge-to-edge measurement of Manchester Encoded waveforms                                                                                                                                                         | -3.2           |       | 3.2             | μs     |

| Receiver<br>Sensitivity              | Threshold for successful carrier detection and decoding, assuming ideal Manchester Encoded input trapezoidal signals with 6µs rise time, valid preamble byte(s) and start delimiter byte, using internal filter. | 75             |       |                 | mVp-p  |

|                                      | r (FF/PA MODE)                                                                                                                                                                                                   | 1              |       |                 |        |

| Dutput Voltage                       |                                                                                                                                                                                                                  |                | 800   |                 | mVp-p  |

| Maximum<br>Amplitude<br>Difference   | Maximum difference in positive and negative amplitude signals                                                                                                                                                    | -50            |       | 50              | mV     |

| Transmit Bit Rate                    |                                                                                                                                                                                                                  | 31.1875        | 31.25 | 31.3125         | kbit/s |

| Transmit Jitter                      | Measured with respect to ideal crossing of high time and low time                                                                                                                                                | -0.8           |       | 0.8             | μs     |

| Output Signal<br>Distortion          | Measured peak to trough distortion for positive and negative amplitude voltage outputs                                                                                                                           | -10            |       | 10              | %      |

| Rise and Fall Time                   | 10% to 90% of peak to peak signal                                                                                                                                                                                |                |       | 8               | μs     |

| Slew Rate                            | 10% to 90% of peak to peak signal                                                                                                                                                                                |                |       | 0.2             | V/µs   |

| DIGITAL REQUIREI                     | MENTS                                                                                                                                                                                                            |                |       |                 |        |

| DIGITAL INPUTS                       |                                                                                                                                                                                                                  | 1              |       |                 |        |

| /IH, Input High<br>/oltage           |                                                                                                                                                                                                                  | 0.7 x<br>IOVDD |       |                 | V      |

| √IL, Input Low<br>√oltage            |                                                                                                                                                                                                                  |                |       | 0.3 x<br>IOVDD  | V      |

| CLK_CFG0, Input<br>High Voltage      | Guaranteed by design                                                                                                                                                                                             | 0.8 x<br>IOVDD |       |                 | V      |

| CLK_CFG0, Input<br>Vid-Scale Voltage | Guaranteed by design                                                                                                                                                                                             | 0.4 x<br>IOVDD |       | 0.55 x<br>IOVDD | V      |

| CLK_CFG0, Input<br>Low Voltage       | Guaranteed by design                                                                                                                                                                                             |                |       | 0.15 x<br>IOVDD |        |

| nput Current                         |                                                                                                                                                                                                                  | -1             |       | 1               | μA     |

| nput Capcitance                      |                                                                                                                                                                                                                  |                | 5     |                 | pF     |

| DIGITAL OUTPUTS                      |                                                                                                                                                                                                                  | 1              |       |                 |        |

| VOH, Output High<br>Voltage          | 200µA source/sink                                                                                                                                                                                                | IOVDD - 0.5    |       |                 | V      |

| √OL, Output Low<br>√oltage           | 200µA source/sink                                                                                                                                                                                                |                |       | 0.4             | V      |

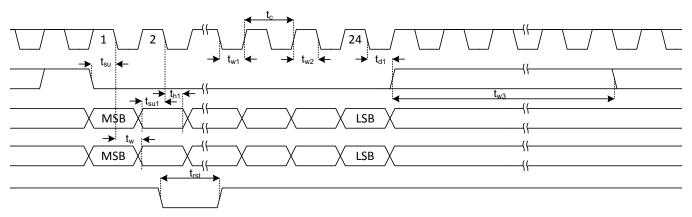

## 6.6 Timing Requirements

All timing conditions guaranteed by design

|                       | PARAMETER                                                                                                                          | MIN | NOM | MAX | UNIT      |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----------|

| t <sub>c</sub>        | SCLK Cycle Time                                                                                                                    | 80  |     |     | ns        |

| t <sub>w1</sub>       | SCLK High Time                                                                                                                     | 32  |     |     | ns        |

| t <sub>w2</sub>       | SCLK Low Time                                                                                                                      | 32  |     |     | ns        |

| t <sub>su</sub>       | /CS to SCLK Falling Edge Setup Time                                                                                                | 32  |     |     | ns        |

| t <sub>su1</sub>      | Data Setup Time                                                                                                                    | 5   |     |     | ns        |

| t <sub>h1</sub>       | Data Hold Time                                                                                                                     | 5   |     |     | ns        |

| t <sub>d1</sub>       | SCLK Falling Edge to /CS Rising Edge                                                                                               | 32  |     |     | ns        |

| t <sub>w3</sub>       | Minimum /CS High Time <sup>(1)</sup>                                                                                               | 1   |     |     | us        |

| t <sub>v</sub>        | SCLK Rising Edge to SDO Valid                                                                                                      | 32  |     |     | ns        |

| t <sub>rst</sub>      | Reset low time                                                                                                                     | 100 |     |     | ns        |

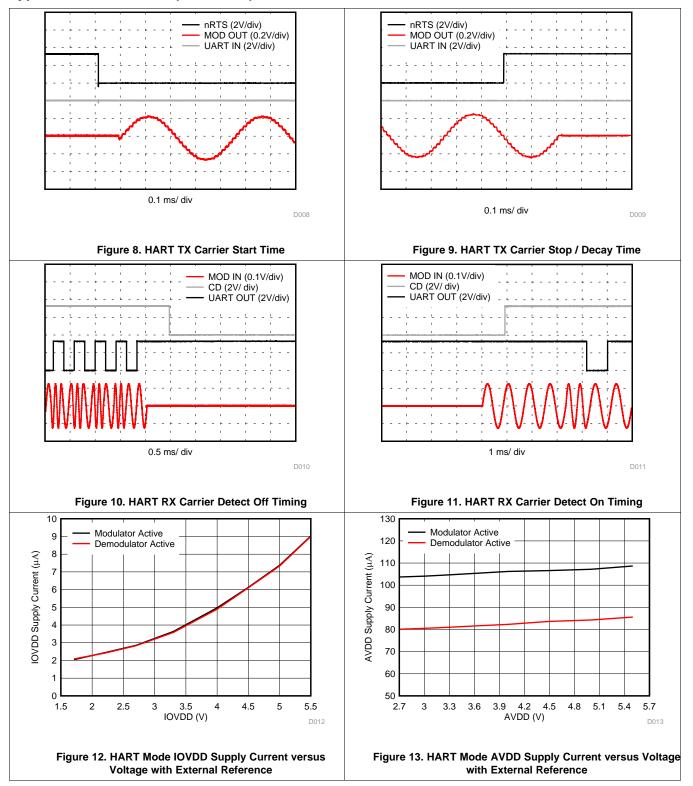

| HART Mode T           | ïming                                                                                                                              |     |     |     |           |

| t <sub>cstart</sub>   | Carrier start time. Time from RTS falling edge to transmit carrier reaching its first peak.                                        |     |     | 5   | Bit-Times |

| t <sub>cstop</sub>    | Carrier stop time. Time from RTS rising edge to transmit carrier amplitude falling below the receive amplitude                     |     |     | 3   | Bit-Times |

| t <sub>cdecay</sub>   | Carrier decay time. Time from RTS riding edge to carrier amplitude dropping to zero.                                               |     |     | 6   | Bit-Times |

| t <sub>cdeton</sub>   | Carrier detect on. Time from valid carrier on receive path to CD rising edge.                                                      |     |     | 6   | Bit-Times |

| t <sub>cdetoff1</sub> | Carrier detect off. Time from valid carrier removed on receive path to CD falling edge.                                            |     |     | 3   | ms        |

| t <sub>cdetoff2</sub> | Carrier detect on when transitioning from transmit<br>mode to receive mode in the presence of a constant<br>valid receive carrier. | 2.1 |     |     | ms        |

| t <sub>cos1</sub>     | Crystal oscillator power-up time from enabling the oscillator via clock configuration pins with 16pF load capacitors.              | 25  |     |     | ms        |

| t <sub>cos2</sub>     | Crystal oscillator power-up time from enabling the oscillator via clock configuration pins with 36pF load capacitors.              | 25  |     |     | ms        |

| t <sub>ref</sub>      | Reference power-up time from enabling via hardware pin.                                                                            | 10  |     |     | ms        |

| t <sub>pow</sub>      | Transition time from power-down mode to normal operating mode with external clock and external reference.                          | 30  |     |     | μs        |

(1) Time between two consecutive  $\overline{CS}$  rising edges must be  $\geq$ 3.06 µs

## Figure 1. SPI Timing Diagram

DAC8742H SBAS940 – DECEMBER 2018

www.ti.com

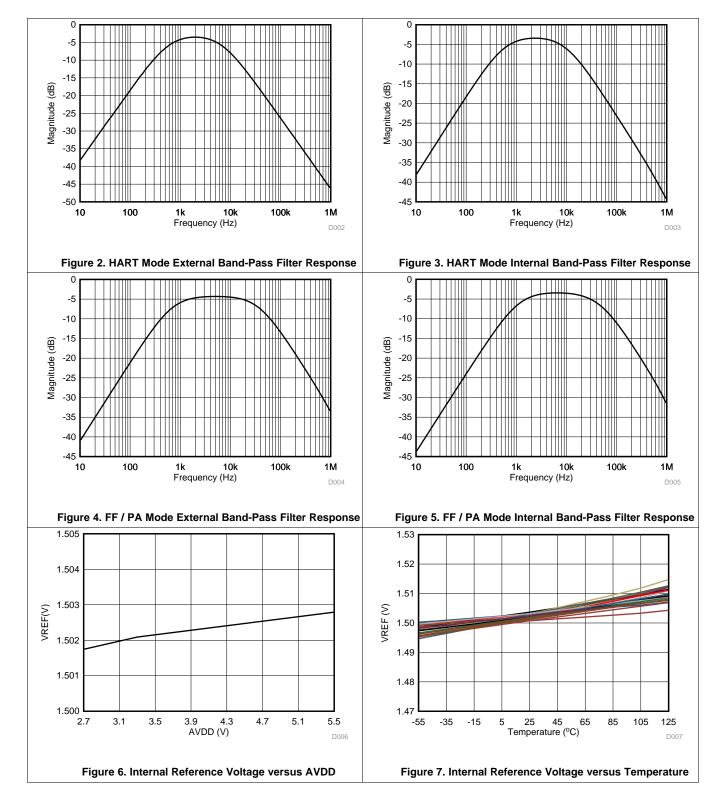

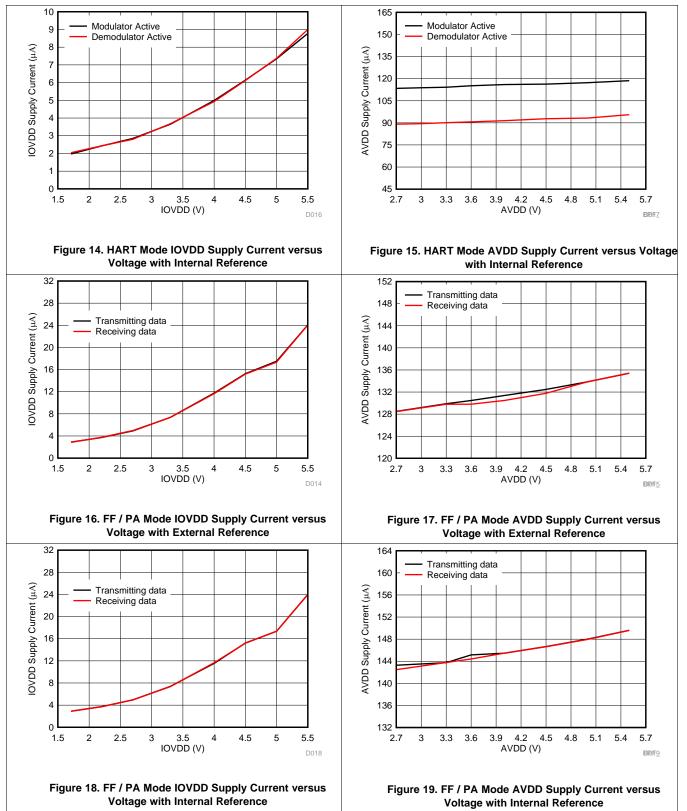

### 6.7 Typical Characteristics

#### **Typical Characteristics (continued)**

### **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

## 7 Detailed Description

### 7.1 Overview

The DAC8742H is a HART© compliant and FOUNDATION Fieldbus® or PROFIBUS PA compatible low power modem designed for industrial process control and industrial automation applications.

In HART mode, the DAC8742H integrates all of the required circuitry to operate as half-duplex HART physical layer modems, in either slave or master configurations with minimal external components for filtering. In FOUNDATION Fieldbus mode, the DAC8742H integrate all of the required circuitry to operate as half-duplex FOUNDATION Fieldbus compliant H1 Controllers & MAUs.

The HART, FOUNDATION Fieldbus, or PROFIBUS PA, data stream can be transferred from the microcontroller through either a UART interface or an integrated FIFO accessed by a SPI interface. The SPI interface includes an SDO pin for daisy-chain support, various interrupts, and other extended features.

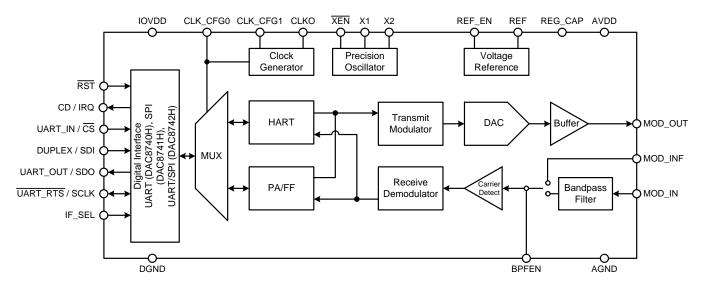

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 HART Modulator

In SPI mode, HART data is loaded into a transmit FIFO via the SPI serial interface. In UART mode, the UART BAUD rate matches the HART BAUD rate and therefore the FIFO is bypassed. In both cases the input data is translated into the mark and space, 1200 Hz and 2200 Hz respectively, frequency shift keyed (FSK) analog signals used in HART communication through an internal HART modulator.

The HART modulator implements a look-up table containing 32 6-bit signed values which represent a single phase continuous sinusoidal cycle. A counter is implemented that incrementally loads the table values to a Digital-to-Analog Converter (DAC), at a clock frequency determined by the binary value of the input data, in order to create the mark and space analog output signals used to represent HART data.

The modem operates in half-duplex mode, unless placed in full-duplex mode, where the modulator and demodulator are not active simultaneously. The modem arbitrates over which component is active. To request that the modulator is activated UART devices toggle the RTS pin low, SPI devices toggle the RTS bit in the MODEM CONTROL register. These mechanics are explained in more detail in the respective sections of Device Functional Modes.

In HART mode the MOD\_OUT pin requires parallel capacitance of 5-22 nF or 0-100 pF in FOUNDATION Fieldbus and PROFIBUS PA mode for stability.

#### Feature Description (continued)

#### 7.3.2 HART Demodulator

The HART demodulator converts the HART FSK input signals applied at the MOD\_IN or MOD\_INF pins, depending on whether an external filter is implemented, to binary data that is loaded into a receive FIFO in SPI mode. Data in the receive FIFO can then be read by the host controller via SPI serial interface. In UART mode received data is directly fed through to the UART interface.

When a valid carrier is detected on devices using the UART interfaces, the CD pin will toggle high. For devices using the SPI interface, the IRQ pin will toggle indicating an alarm condition. The MODEM STATUS register can then be read to determine the source of the interrupt, which includes a bit for carrier detection in DB1. Hysteresis is implemented with the carrier detect feature in order to prevent erroneous carrier detection signals. More details are explained in the respective Device Functional Modes sections.

#### 7.3.3 FOUNDATION FIELDBUS / PROFIBUS PA Manchester Encoder

FOUNDATION FIELDBUS or PROFIBUS PA data is loaded into a transmit FIFO via UART or SPI interfaces which is translated into the Manchester encoded binary analog signals used in both FOUNDATION FIELDBUS and PROFIBUS PA bus protocols through an internal Manchester encoder.

The Manchester encoder interacts with the DAC to transmit positive and negative amplitude signals, with respect to a positive common mode voltage, to create the Manchester encoded analog outputs at 31.25kHz BAUD. A binary 0 is represented by a low-to-high transition and a binary 1 is represented by a high-to-low transition.

In both UART and SPI interfaced device, the encoder is activated any time there is data available in the transmit FIFO and the decoder is not receiving data. In order to prevent FIFO buffer overflow, for UART mode the CD pin acts as an interrupt to indicate when the FIFO level has exceed a programmed threshold in the packet initiation code. In SPI mode the transmit FIFO threshold programmed in the FIFO LEVEL SET register can trigger an interrupt on the IRQ pin. Once the IRQ interrupts is triggered, the MODEM STATUS register can then be read to determine the source of the interrupt, which includes a bit for the FIFO level in DB4. More details are explained in the respective Device Functional Modes sections.

#### 7.3.4 FOUNDATION FIELDBUS / PROFIBUS PA Manchester Decoder

The FOUNDATION FIELDBUS and PROFIBUS PA decoder converts the Manchester encoded data applied at the MOD\_IN or MOD\_INF pins, depending on whether an external filter is implemented, to binary data that is loaded into a receive FIFO. Data in the receive FIFO can then be read by the host controller via UART or SPI serial interfaces.

When valid data is provided to the decoder, binary data is read out serially on the UART interface. For SPI devices, the receive FIFO is loaded until the threshold programmed in FIFO LEVEL SET is met which will trigger an interrupt on the IRQ pin. The MODEM STATUS register can then be read to determine the source of the interrupt, which includes a bit for the FIFO level in DB7, indicating that data is ready to be read on the SPI bus. More details are explained in the respective Device Functional Modes sections.

#### 7.3.5 Internal Reference

An internal reference is included in the DAC8742H. The REF\_EN pin is used to enable or disable the internal reference, when the internal reference is disabled an external reference must be provided at the REF pin. In SPI mode, the PDVREF bit in the CONTROL register can be used to enable or disable the internal reference via software. If the REF\_EN pin is set high, the register contents of the PDVREF bit is ignored.

| INTERFACE | PDVREF      | REF_EN | REFERENCE MODE     |

|-----------|-------------|--------|--------------------|

| UART      | 1 (Default) | 0      | External Reference |

| UART      | 1 (Default) | 1      | Internal Reference |

| SPI       | 1 (Default) | 1      | Internal Reference |

| SPI       | 0           | 1      | Internal Reference |

| SPI       | 1 (Default) | 0      | External Reference |

| SPI       | 0           | 0      | External Reference |

#### 7.3.6 Clock Configuration

All of the devices in the DAC8742H family support a variety of clocking options in order to provide system flexibility and reduce overall current consumption in HART applications. The clocking options include: an internal oscillator (HART mode only), an external crystal oscillator, or an external CMOS clock. The selection of the clocking scheme is controlled by the XEN, CLK\_CFG1, and CLK\_CFG0 pins as described in the table below.

The internal oscillator takes approximately 50 ms to start oscillating from when it is enabled. During this time period the device is unable to perform modulation or demodulation activities.

| XEN | CLK_CFG1 | CLK_CFG0 | CLKO             | DESCRIPTION                                   | MODE                     |

|-----|----------|----------|------------------|-----------------------------------------------|--------------------------|

| 1   | 0        | 0        | No Output        | 3.6864MHz CMOS clock<br>connected at XTAL1    |                          |

| 1   | 0        | 1        | No Output        | 1.2288MHz CMOS clock<br>connected at XTAL1    |                          |

| 1   | 1        | 0        | No Output        | Internal oscillator enabled                   |                          |

| 1   | 1        | 1        | 1.2288MHz Output | Internal oscillator enabled,<br>CLKO enabled  | HART                     |

| 0   | 0        | 0        | No Output        | Crystal oscillator enabled                    | TAK I                    |

| 0   | 0        | 1        | 3.6864MHz Output | 3.6864MHz crystal oscillator,<br>CLKO enabled |                          |

| 0   | 1        | 0        | 1.8432MHz Output | 3.6864MHz crystal oscillator,<br>CLKO enabled |                          |

| 0   | 1        | 1        | 1.2288MHz Output | 3.6864MHz crystal oscillator,<br>CLKO enabled |                          |

| 1   | 0        | 0.5      | No Output        | 4MHz CMOS clock connected<br>at XTAL1         |                          |

| 1   | 1        | 0.5      | No Output        | 2MHz CMOS clock connected<br>at XTAL1         | FOUNDATION<br>FIELDBUS & |

| 0   | 0        | 0.5      | No Output        | 4MHz crystal oscillator                       | PROFIBUS PA              |

| 0   | 1        | 0.5      | 4MHz Output      | 4MHz crystal oscillator, CLKO<br>enabled      |                          |

#### **Table 1. Clock Configuration Table**

#### 7.3.7 Reset and Power-Down

The  $\overline{RST}$  pin functions as both a hardware reset and a power-down. When the pin is brought low a reset is issued, restoring all device components to their default state. While the pin is kept low, the device is in a power-down state where the internal reference is disabled, the modulator and demodulator or encoder and decoder are disabled, serial data output lines are high-impedance, MOD\_OUT impedance is set to 70 k $\Omega$ , and the clock output is disabled. If an external crystal oscillator is used, the crystal oscillator circuit remains active to reduce start-up time when exiting the power-down state. Clock configuration pins remain active in power-down allowing the crystal oscillator to be disabled if desired.

#### 7.3.8 Full-Duplex Mode

In full-duplex mode the modulator and demodulator (HART mode) or encoder and decoder (FOUNDATION FIELDBUS or PROFIBUS PA mode) are simultaneously enabled. This allows a self-test feature to verify functionality of the transmit and receive signal chains to improve system diagnostics.

#### 7.3.9 I/O Selection

The DAC8742H implements both SPI and UART interfaces. Only one interface is active at a time for the DAC8742H. The interface mode is selected by the IF\_SEL pin: a logic high on this pin sets the device to SPI mode and a logic low sets the device to UART mode. An internal pull-down resistor is included to ensure power-up in a known state, by default the pull-down sets the interface to UART mode. If changing I/O modes after power-up, a reset command should be issued on RST.

#### 7.3.10 Jabber Inhibitor

The DAC8742H implements a Jabber Inhibitor feature in FOUNDATION FIELDBUS or PROFIBUS PA modes which prevents the encoder from continuously transmitting data on the bus for longer than a programmed threshold controlled by the UART or SPI interface. In SPI mode this threshold is programmed by the PAFF\_JABBER register, in UART mode this threshold is programmed by the four byte initialization sequence before each transmission. This is described in further detail in the Device Functional Modes and Register Map sections.

### 7.4 Device Functional Modes

#### 7.4.1 UART Interfaced HART

When interfacing the HART modem via the UART interface, the device can be thought of as a simple UART-to-HART or HART-to-UART direct feedthrough converter. The UART data is transmitted and received at 1200 BAUD, which is matched to the HART FSK input and output signals.

The HART communication protocol is a half-duplex protocol which means that either the modulator or demodulator is active, and never simultaneously enabled. The device arbitrates over which component of the modem is active at <u>all times</u> based on activity on the HART bus. Bus activity is interfaced to the host controller through the CD and RTS pins.

By default when RTS is high the demodulator is active and the modulator is inactive. When a valid carrier is detected and data is being received by the modem, the CD pin is toggled high and binary UART data is provided at the output. If a request to send is issued by toggling the RTS pin low while CD is high, the demodulator remains at priority and any data provided at the UART input is ignored. When CD is low no valid carrier is present and when RTS is brought low the modulator is activated and UART input data is latched into the modulator and placed onto the HART bus.

#### 7.4.2 UART Interfaced FOUNDATION FIELDBUS / PROFIBUS PA

FOUNDATION FIELDBUS and PROFIBUS PA are half-duplex communication protocols where only the encoder or decoder are active at any time and the DAC8742H arbitrates over which path is active. When interfacing the FOUNDATION FIELDBUS or PROFIBUS PA modem via the UART interface, data placed in the transmit FIFO is automatically placed on the FF/PA bus until the FIFO is empty any time the device is not receiving data, assuming correct data format.

When receiving data the decoder will expect a preamble byte(s) and a start delimiter byte. These bytes, as well as the stop byte, will be stripped from the UART communication and only the first data byte will be transmitted to start the data packet. The host controller must use a timer to detect the end of the packet. Each byte transmitted on the UART will be at 57.6 kHz BAUD and byte spacing of 256 us. If a new byte has not been started within 512 us it can be assumed that the incoming packet has ended.

The device expects to see a four byte sequence to initiate transmission: 0xEA followed by 0x80-0x9F, where bits 4:3 of the second byte configure an interrupt threshold for the transmit FIFO level and bits 2:0 set the number of preamble bytes to be transmitted. The third byte contains the information to configure the Jabber Inhibitor followed by the final byte of 0xAE. To send inverted Manchester encoded data the first byte, 0xEA, is inverted to 0x15 and the first three bits of the second byte are inverted such that the range of values for the second byte are from 0x60-0x7F. The functionality of bits 4:3 and 2:0 and the Jabber Inhibitor byte remain the same and the final byte is inverted to 0x51. The details concerning this four byte sequence are explained in the tables below.

|                  |   | B3    |   |   |   |    |    |    |    |    |    |       | B2    |   |        |     |

|------------------|---|-------|---|---|---|----|----|----|----|----|----|-------|-------|---|--------|-----|

| Mode             |   | D7:D0 |   |   |   | D7 | D6 | D5 | D4 | D3 | D2 | D1    | D0    |   |        |     |

| Non-<br>inverted | 1 | 1     | 1 | 0 | 1 | 0  | 1  | 0  | 1  | 0  | 0  | D2M_I | LEVEL | F | PRE_BY | TES |

| Inverted         | 0 | 0     | 0 | 1 | 0 | 1  | 0  | 1  | 0  | 1  | 1  | D2M_I | LEVEL | F | PRE_BY | TES |

DAC8742H SBAS940-DECEMBER 2018

www.ti.com

(1)

NSTRUMENTS

**EXAS**

|                  | B1             |    |    |    | E  | 30 |    |    |    |

|------------------|----------------|----|----|----|----|----|----|----|----|

| Mode             | D7:D0          | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Non-<br>inverted | JABBER_TIMEOUT | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0  |

| Inverted         | JABBER_TIMEOUT | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 1  |

| CONTROL BITS |     | DESCRIPTION                                                                                           |                                                                   |  |  |  |  |  |

|--------------|-----|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|

|              | 0   | 0                                                                                                     | Alarm on UART_RTS when transmit FIFO has less than 2 bytes loaded |  |  |  |  |  |

|              | 0   | 1                                                                                                     | Alarm on UART_RTS when transmit FIFO has less than 4 bytes loaded |  |  |  |  |  |

| D2M_LEVEL    | 1   | 0                                                                                                     | Alarm on UART_RTS when transmit FIFO has less than 6 bytes loaded |  |  |  |  |  |

|              | 1   | 1 1 Alarm on UART_RTS when transmit FIFO has less than 8 bytes loaded                                 |                                                                   |  |  |  |  |  |

| PRE_BYTES    | Num | Jumber of preamble bytes is equivalent to the straight binary decimal value in this register plus one |                                                                   |  |  |  |  |  |

The JABBER\_TIMEOUT bits control the timeout period for the Jabber Inhibitor. If a value of 0x0 is programmed the Jabber Inhibitor is disabled. Otherwise the timer will be programmed in 2.048ms increments such that the timeout can be calculated as shown below. If the Jabber Inhibitor triggers the CD pin will be taken high. The CD pin will be returned to logic low when the silence period of 3 seconds has ended.

TimeOut = JABBER\_TIMEOUT x 2.048ms

The encoder will begin transmitting data once the following conditions are met: a valid four-byte transmission initiation sequence has been sent to the device, the FIFO is not empty, and the device is not receiving data. Transmission will begin by sending the preamble byte(s) followed by a start delimiter. Then, the encoder will begin to remove data from the FIFO – this creates at least a five-byte lag of the encoder with respect to the UART.