# AD9081/AD9082 System Development User Guide

#### SCOPE

This user guide provides information for systems engineers and software developers using the AD9081 and AD9082 family of software defined, direct RF sampling transceivers. This family of devices consists of high performance digital-to-analog converters (DAC) and analog-to-digital converters (ADC) with configurable digital datapaths in support of processing signals or RF bands of varying bandwidth. These devices also support various digital features that enhance or simplify system integration. Table 1 outlines the key differences between these devices, and the Common Features section outlines the common features shared among the devices. These devices are interchangeable unless otherwise stated in this user guide. For full specifications on the AD9081 and AD9082, refer to the AD9081 and AD9082 data sheets, which must be consulted in conjunction with this user guide to achieve successful product selection and design.

Table 1. Product Listing with Distinguishing Features

|                                        | Transmit (Tx)                         |                                        |                                         |                           | Receive (                    | Rx)                                     |                                  | Special Digital Features |                                       | Device ID Register Values               |       |       |       |       |

|----------------------------------------|---------------------------------------|----------------------------------------|-----------------------------------------|---------------------------|------------------------------|-----------------------------------------|----------------------------------|--------------------------|---------------------------------------|-----------------------------------------|-------|-------|-------|-------|

| Device and<br>Channel<br>Configuration | No. of DAC<br>Channels,<br>Resolution | Max DAC<br>Rate<br>(GSPS) <sup>1</sup> | Max Tx<br>Channel<br>Bandwidth<br>(GHz) | No. of<br>ADC<br>Channels | Max<br>ADC<br>Rate<br>(GSPS) | Max Rx<br>Channel<br>Bandwidth<br>(GHz) | Tx and Rx<br>Bypass<br>Operation | Rx to Tx<br>Loopback     | Fast<br>Frequency<br>Hopping<br>(FFH) | Direct<br>Digital<br>Synthesis<br>(DDS) | 0x003 | 0x004 | 0x005 | 0x006 |

| AD9081                                 |                                       |                                        |                                         |                           |                              |                                         |                                  |                          |                                       |                                         |       |       |       |       |

| -4D4AC                                 | 4 – 16b                               | 12                                     | 1.2                                     | 4                         | 4                            | 2                                       | Yes                              | Yes                      | Yes                                   | Yes                                     | 0Fh   | 81h   | 90h   | A3h   |

| -4D4AC                                 | 4 – 12b                               | 12                                     | 1.6                                     | 4                         | 4                            | 2                                       | Yes                              | Yes                      | Yes                                   | Yes                                     | 0Fh   | 81h   | 90h   | A3h   |

| -4D4AB                                 | 4 – 16b                               | 12                                     | 0.6                                     | 4                         | 4                            | 0.6                                     | Yes                              | Yes                      | Yes                                   | Yes                                     | 0Fh   | 81h   | 90h   | B3h   |

| AD9082                                 |                                       |                                        |                                         |                           |                              |                                         |                                  |                          |                                       |                                         |       |       |       |       |

| -4D2AC                                 | 4 – 16b                               | 12                                     | 1.2                                     | 2                         | 6                            | 3                                       | Yes                              | Yes                      | Yes                                   | Yes                                     | 0Fh   | 82h   | 90h   | 23h   |

| -4D2AC                                 | 4 – 12b                               | 12                                     | 2.4                                     | 2                         | 6                            | 3                                       | Yes                              | Yes                      | Yes                                   | Yes                                     | 0Fh   | 82h   | 90h   | 23h   |

| -2D2AC                                 | 2 – 16b                               | 12                                     | 2.4                                     | 2                         | 6                            | 3                                       | Yes                              | Yes                      | Yes                                   | Yes                                     | 0Fh   | 82h   | 90h   | 13h   |

| AD9988                                 |                                       |                                        |                                         |                           |                              |                                         |                                  |                          |                                       |                                         |       |       |       |       |

| -4D4AC                                 | 4 – 16b                               | 12                                     | 1.2                                     | 4                         | 4                            | 1.6                                     | No                               | No                       | No                                    | No                                      | 0Fh   | 88h   | 99h   | A3h   |

| AD9986                                 |                                       |                                        |                                         |                           |                              |                                         |                                  |                          |                                       |                                         |       |       |       |       |

| -4D2AC                                 | 4 – 16b                               | 12                                     | 1.2                                     | 2                         | 6                            | 2.4                                     | No                               | No                       | No                                    | No                                      | 0Fh   | 86h   | 99h   | 23h   |

| -4D2AC                                 | 2 – 16b                               | 12                                     | 2.4                                     | 2                         | 6                            | 2.4                                     | No                               | No                       | No                                    | No                                      | 0Fh   | 86h   | 99h   | 23h   |

| AD9207                                 | N/A                                   | N/A                                    | N/A                                     | 2                         | 6                            | 3                                       | Yes                              | N/A                      | Yes                                   | N/A                                     | 03h   | 07h   | 92h   | 23h   |

| AD9209                                 | N/A                                   | N/A                                    | N/A                                     | 4                         | 4                            | 2                                       | Yes                              | N/A                      | Yes                                   | N/A                                     | 03h   | 09h   | 92h   | A3h   |

| AD9177                                 | 4 – 16b                               | 12                                     | 1.2                                     | N/A                       | N/A                          | N/A                                     | Yes                              | Yes                      | Yes                                   | Yes                                     | 04h   | 77h   | 91h   | A3h   |

<sup>&</sup>lt;sup>1</sup> Max DAC Rate assumes 16-bit resolution.

# **TABLE OF CONTENTS**

| Scope1                                       | Main Digital Datapath                | 177 |

|----------------------------------------------|--------------------------------------|-----|

| System Overview3                             | DAC Outputs                          |     |

| Common Features3                             | Auxiliary Features                   | 192 |

| Software Overview6                           | Receive AGC Assist Functions         | 192 |

| Software Architecture6                       | Programmable Filter (PFILT)          | 197 |

| Folder Structure7                            | Transmit Downstream Power Amplifier  |     |

| API Integration and Build7                   | Protection                           | 207 |

| API Overview Block Diagram9                  | Transmit Power Control               | 211 |

| Serial Peripheral Interface11                | IRQ                                  | 212 |

| SPI Configuration API12                      | GPIOx Pin Operation                  | 212 |

| Sampling Clock and Distribution Options 13   | Temperature Monitoring Unit (TMU)    | 215 |

| Clock Multiplier13                           | AD9081/AD9082/AD9177 Only Features   | 217 |

| Clock Receiver Input15                       | Transmit and Receive Bypass Mode     | 217 |

| Clock Output Driver18                        | FFH Mode                             | 217 |

| Clock Configuration APIs18                   | Receive to Transmit Analog Loopback  | 222 |

| JESD204B/C Interface Functional Overview     | Applications Information             |     |

| and Common Requirements20                    | Device Latency                       | 224 |

| New Features in the JESD204C Standard20      | System Multichip Synchronization     | 226 |

| 8-Bit/10-Bit Link Establishment Overview 24  | PCB Layout and Design Considerations | 229 |

| 64-Bit/66-Bit Link Establishment Overview 24 | RF and JESD204B/C SERDES             |     |

| SERDES PLL and Configuration24               | Transmission Line Layout             | 232 |

| SYSREF and Subclass 1 Operation26            | Isolation Techniques Used on the     |     |

| Receive Input and Digital Datapath38         | Evaluation Board                     | 233 |

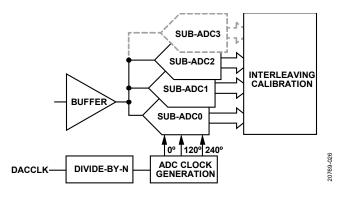

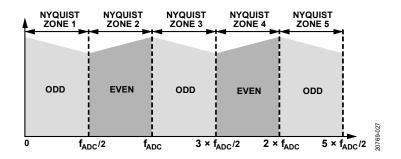

| ADC Architecture Overview38                  | Power Consumption                    | 234 |

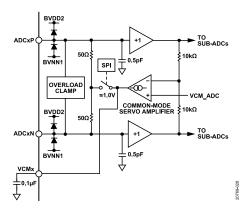

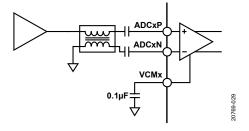

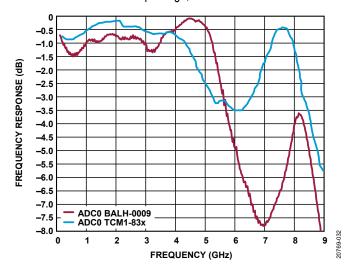

| ADC Input Buffer40                           | Power Management Considerations      | 256 |

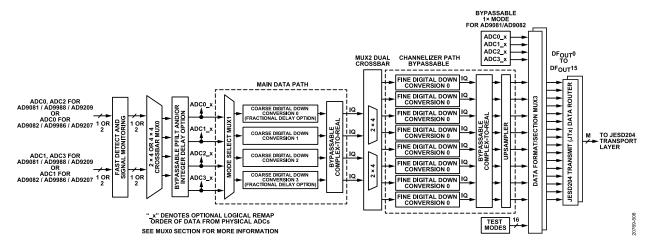

| Receive Digital Datapath Overview44          | Thermal Management Considerations    |     |

| Receive Datapath Configuration               | Device Test Modes                    |     |

| Considerations45                             | ADC Datapath Test Modes              | 259 |

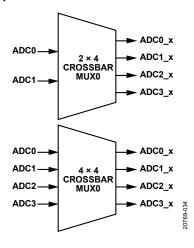

| Mux047                                       | JESD204B/C Transmitter Test Modes    |     |

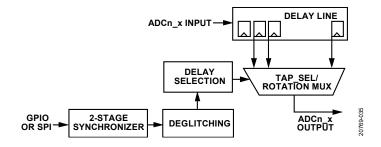

| Bypassable Integer Delay and PFILT48         | JESD204B/C Receiver Test Modes       | 262 |

| Mux149                                       | JESD204B Debug Guide                 | 275 |

| Receive Main Digital Datapath50              | PHY PRBS Failure                     | 275 |

| Receive Channelizer Digital Datapath61       | Lane Crossbar Mapping                | 275 |

| JESD204B/C Transmitter69                     | 8-Bit/10-Bit Data Link Errors        |     |

| Configuring the JESD204B/C Transmitter       | Invalid Mode Bit Readback            | 276 |

| Link82                                       | JESD204C Debug Guide                 | 278 |

| Transmit Digital Datapath and Output 144     | PHY PRBS Failure                     |     |

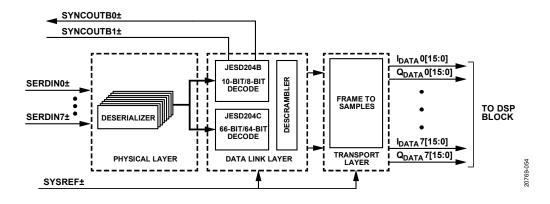

| JESD204B/C Receiver Functional Overview. 144 | Lane Crossbar Mapping                | 279 |

| Configuring the JESD204B/C Receiver165       | Register 0x055E, Bits[6:4], is Not 6 |     |

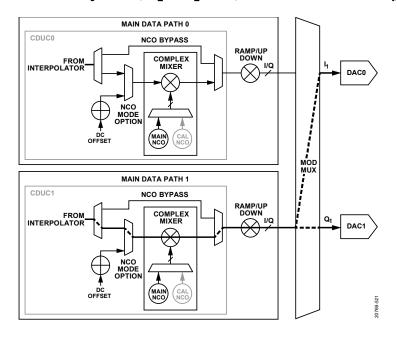

| Transmit Digital Datapath Overview168        | Invalid Mode Bit Readback is 1       |     |

| Data Router Multiplexers and Default         | Need Analog Devices Debug Assistance |     |

| Mapping170                                   | Register Details                     |     |

| Channelizer Datapath171                      | Notes                                |     |

| 8 × 8 Crossbar Multiplexer177                |                                      |     |

analog.com Rev. A | 2 of 391

#### SYSTEM OVERVIEW

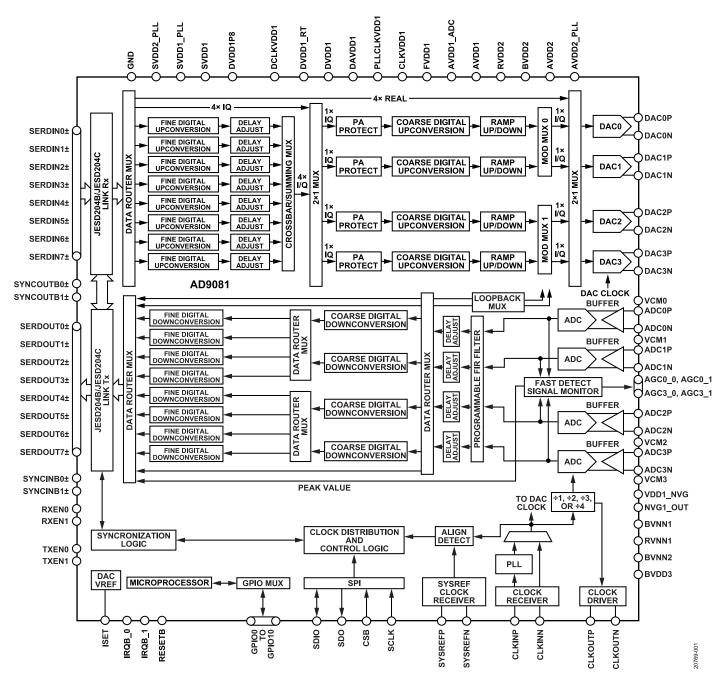

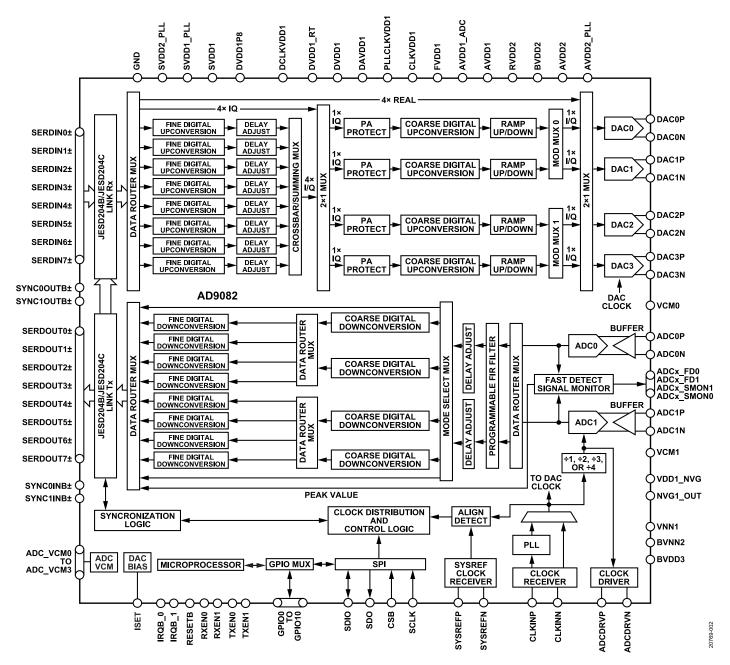

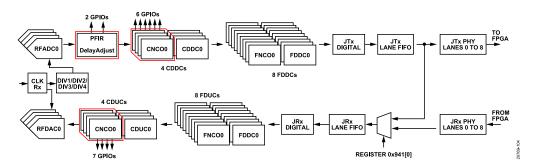

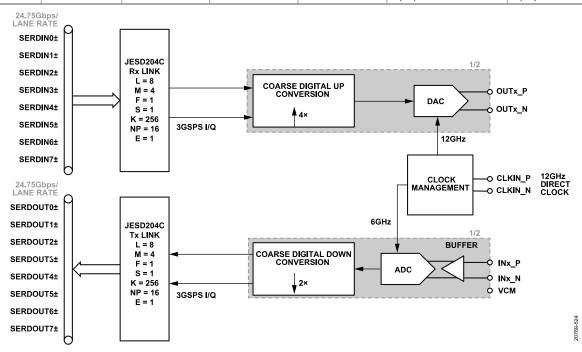

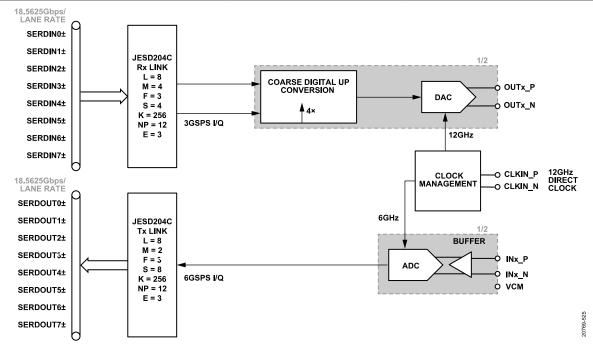

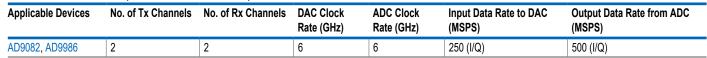

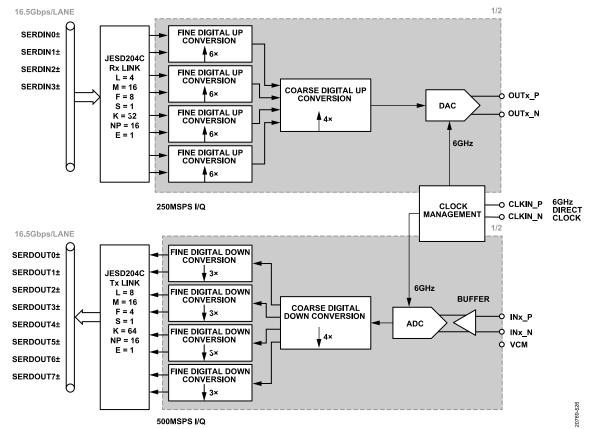

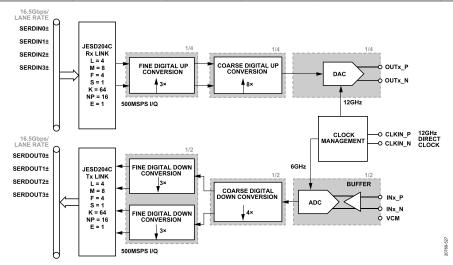

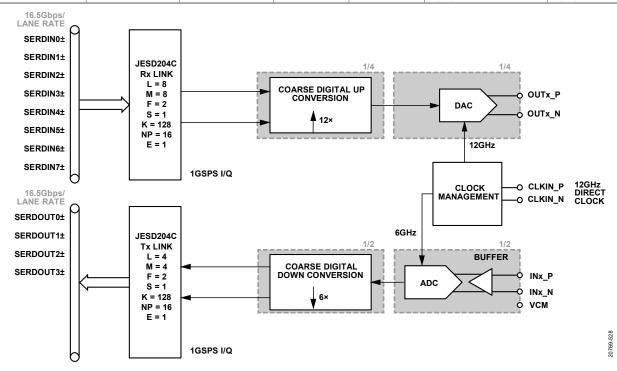

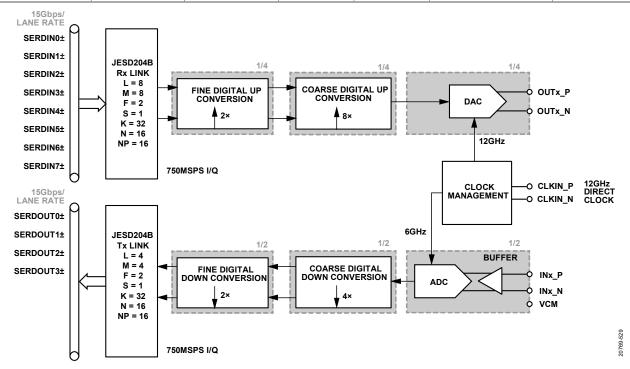

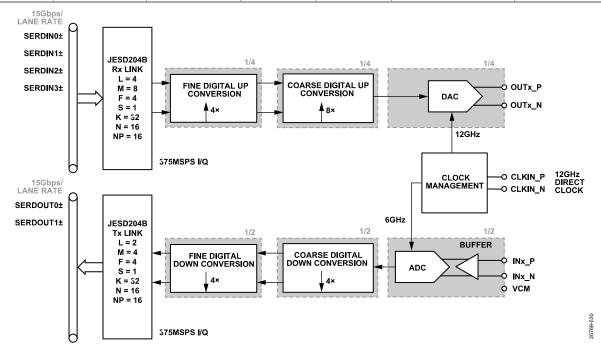

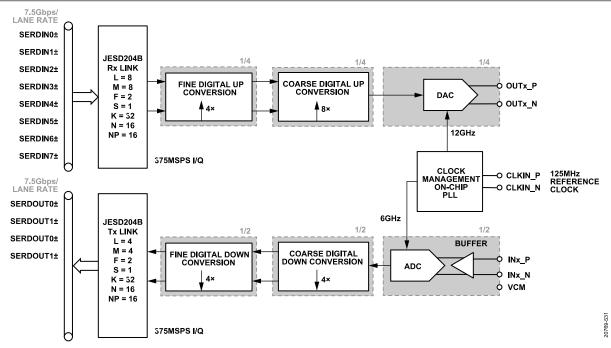

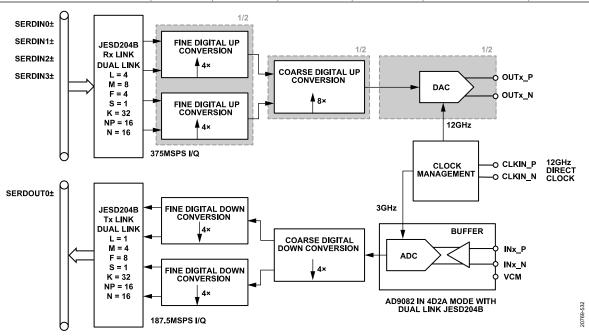

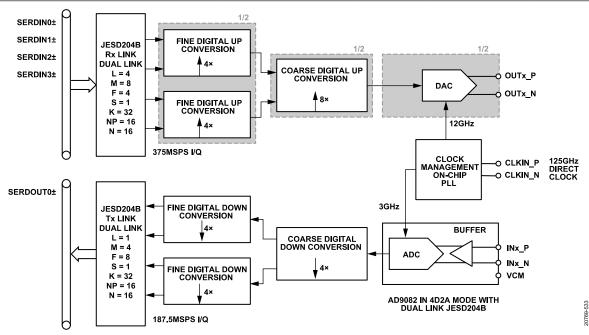

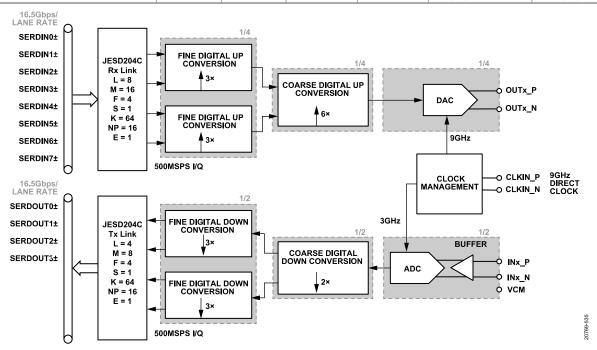

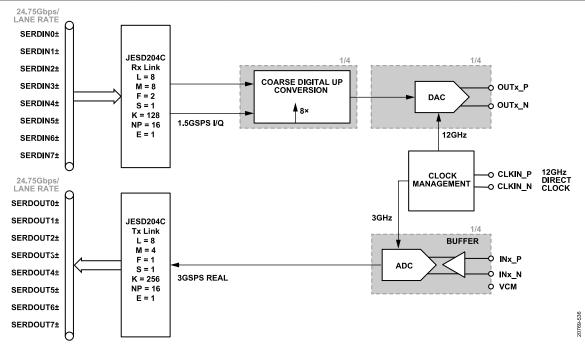

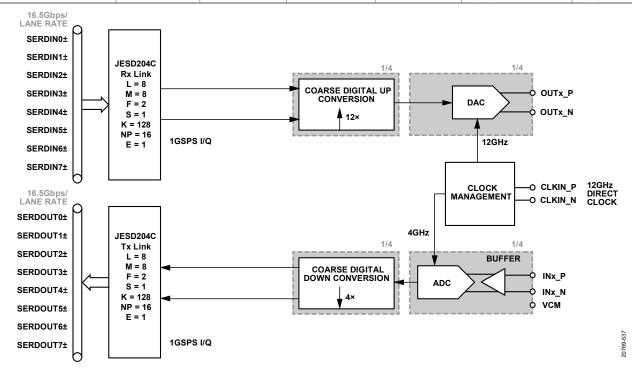

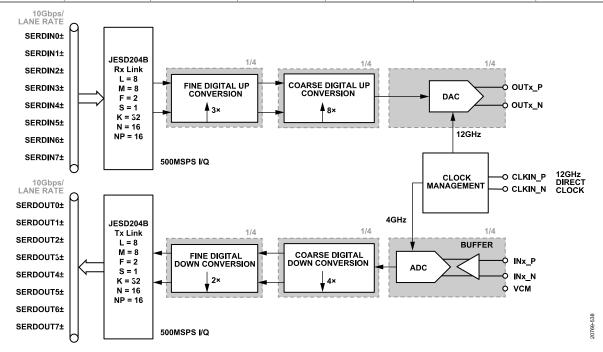

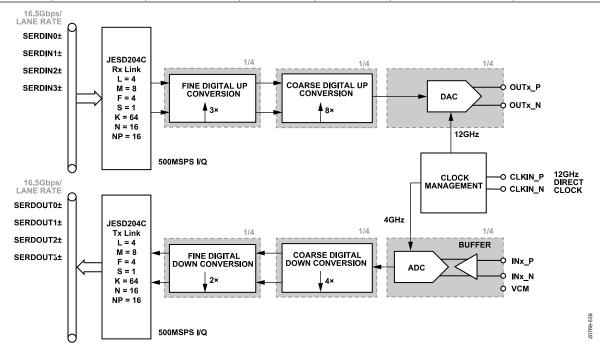

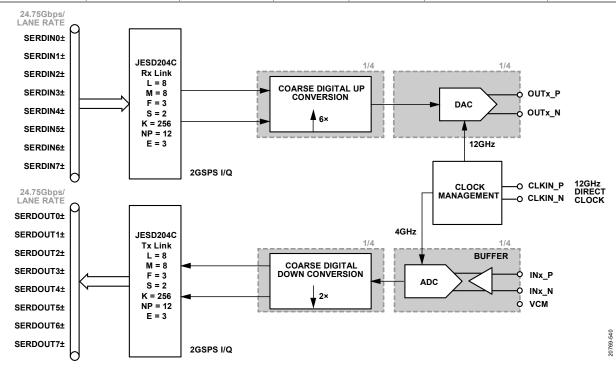

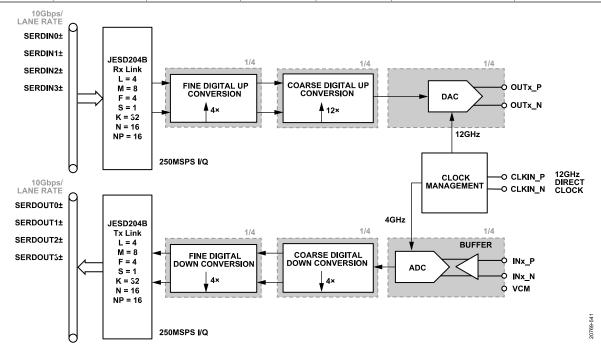

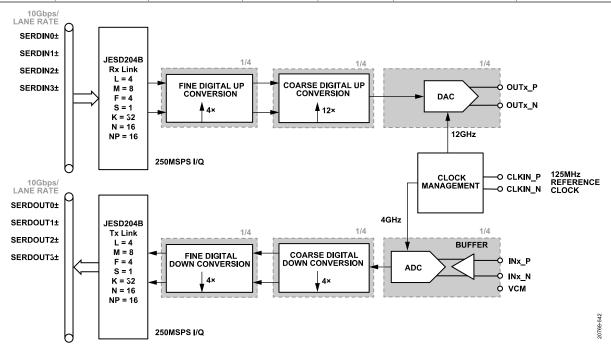

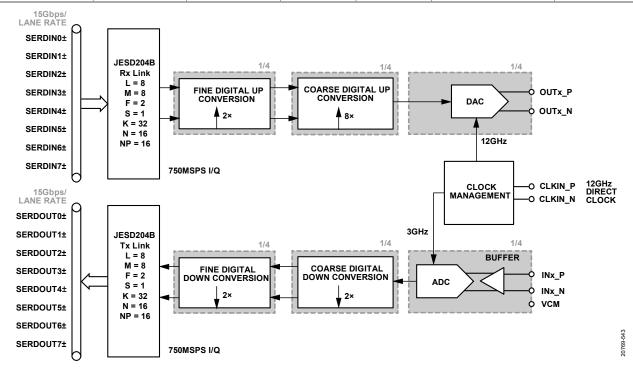

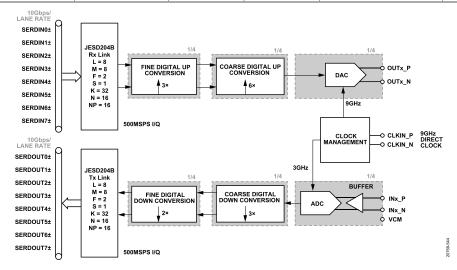

The AD9081 is a highly integrated, RF mixed signal front-end (MxFE™) that features four 16-bit, 12 GSPS DAC cores and four 12-bit, 4 GSPS ADC cores, as shown in Figure 1. The AD9082 features four 16-bit, 12 GSPS DAC cores and two 12-bit, 6 GSPS ADC cores, as shown in Figure 2. Aside from the different ADC options, both devices are nearly identical in all other aspects (unless otherwise noted in this user guide). The devices include an optional on-chip clock multiplier for DAC and ADC sampling clock generation as well as broadband ADC and DAC cores with on-chip 100 Ω termination.

The transmit and receive digital datapaths are highly configurable and support a wide range of single band and multiband applications with varying RF bandwidth requirements. The transmit and receive datapaths consist of four main datapaths in support of wideband signals and eight channelizers in support of narrower band signals. For multiband applications with wide separation between RF bands, the channelizers can be used to process the individual RF bands to reduce the overall complex data rate needed to represent each narrower band. Both the main and channelizer datapath stages offer flexible interpolating and decimation factors to allow a manageable data interface rate aligned to the actual signal bandwidth requirements. The numerically controlled oscillator (NCO) of each stage can be independently tuned for maximum flexibility.

Additional digital features are listed in the Common Features section.

The serializer/deserializer (SERDES) interface supports eight lanes for transmit data and eight lanes for receive data. Both JESD204B and JESD204C protocols are supported as well as the ability to configure dual links. The JESD204B/C data link layer is highly flexible and allows optimization of the lane count (or rate) required to support a desired data throughput rate. Multichip synchronization and internal synchronization for deterministic latency and phase alignment are supported via an external alignment signal (SYSREF).

## **COMMON FEATURES**

# **Analog Features**

Common analog features for the devices include the following:

- ▶ Usable RF range up to 8 GHz

- ▶ ADC overvoltage protection

- ▶ DAC transmit gain control

- ▶ On-chip phased-locked loop (PLL) clock multiplier with output clock

#### **Digital Features**

Common digital features for the devices include the following:

- ▶ Transceiver and receiver digital upconverter (DUC) and digital downconverter (DDC)

- ▶ Highly configurable 196-tap programmable filter (PFILT) supporting four profiles

- ▶ Transceiver and receiver integer delay with receiver fractional delay

- Multichip synchronization

- Receiver signal monitoring and automatic gain control (AGC) assist features

- ► Transceiver gain control and power amplifier (PA) protection

- Power reduction options

- ▶ General purpose input/output (GPIO)

#### **SERDES Interface**

Common SERDES features for the devices include the following:

- ▶ JESD204B and JESD204C

- ▶ Eight transmit lanes and eight receive lanes

- Support for two links

- Support for up to 16 virtual converters

- Sample repeat option

analog.com Rev. A | 3 of 391

#### SYSTEM OVERVIEW

Figure 1. AD9081 Functional Block Diagram

analog.com Rev. A | 4 of 391

#### SYSTEM OVERVIEW

Figure 2. AD9082 Functional Block Diagram

analog.com Rev. A | 5 of 391

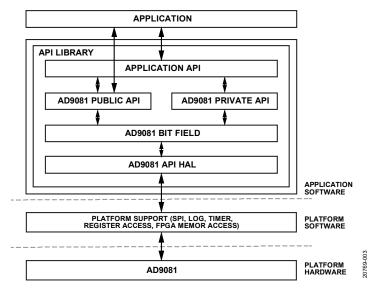

This section provides information about the application programming interface (API) software developed by Analog Devices, Inc., for the AD9xxx product family. This section outlines the overall architecture, folder structure, and methods for using the API software on any platform.

The device API C code drivers are provided as reference code that allows the user to quickly configure the product using high level function calls. The library acts as an abstraction layer between the application and the hardware. The API is developed in C99 to ensure agnostic processor and operating system integration. Customers can port this application layer code to their embedded systems by integrating their platform specific code base to the API hardware abstraction layer (HAL).

To request this software package, navigate to the software request form while signed in to your MyAnalog account. From under **Target Hardware**, select **High Speed Data Converters** and choose the desired API product package. You will receive an email notification once the software is provided to you.

#### **SOFTWARE ARCHITECTURE**

The device API library is a collection of APIs that provide a consistent interface for the AD9xxx product family. The APIs are designed such that there is a consistent interface to the devices.

The API library is a software layer that sits between the application and the device, as shown in Figure 3. The library is intended to serve the following purposes:

- ▶ To provide the application with a set of APIs that can be used to configure the device without the need for low level register access, which makes the application portable across different revisions of the hardware and across different hardware modules.

- ▶ To provide basic services to aid the application in controlling the components of the device module, such as NCO configuration and JESD204B/C link configuration.

The driver does not alter the device configuration or state of the device without assistance. The application must configure the device according to the required mode of operation and poll for status. The library acts only as an abstraction layer between the application and the hardware.

For example, the application is responsible for the following:

- Configuring the JESD interface

- Configuring the DDC and NCOs

The application must access the device only through the exported APIs. Accessing the device directly using serial peripheral interace (SPI) access is not recommended. If the application directly accesses the device hardware, the application must do so in a limited scope, such as for debug purposes. Note that this practice of direct access may affect the reliability of the API functions.

Figure 3. AD9081 API Architecture

analog.com Rev. A | 6 of 391

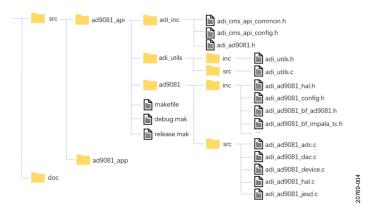

#### **FOLDER STRUCTURE**

The collective files of the device API library are structured as shown in Figure 4. Each branch in the directory hierarchy is explained in the /src/ad9081\_api section through the /doc section. The library is supplied in source format. All source files are in standard C99 to simplify porting to any platform.

Figure 4. AD9081 Source Code Folder Structure

## /src/ad9081\_api

The device API root folder contains all source code and the example makefile for the API.

## /src/ad9081\_api/adi\_inc

This folder contains all API public interface files. These files are the header files required by the client application for integration.

## /src/ad9081\_api/adi\_utils

This folder contains the helper functions common to all Analog Devices APIs. These functions are internal private functions and are not designed for client application use.

## /src/ad9081\_api/ad9081

This folder includes the main API implementation code for the device APIs and any private header files used by the API. Analog Devices maintains this code as intellectual property and all changes are at the sole discretion of Analog Devices.

## /src/ad9081\_app

This folder contains simple source code examples of how to use the device API. The application targets the device evaluation board platform. Customers can use this example code as a guide to develop their own application based on individual user requirements.

#### /doc

This folder contains the documentation for the device APIs.

## **API INTEGRATION AND BUILD**

This section provides an overview of the integration and building steps required when using Analog Devices API source code.

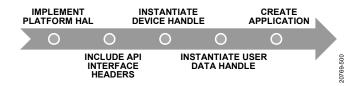

Because Analog Devices provides the full source code, the user can integrate and build the libraries per their application. However, users are required to integrate the API HAL with their platform specific code base. This action is readily accomplished because the API was developed in C99. The C99 standard was followed to ensure agnostic processor and operating system integration with the API code. See Figure 5 for the AD9xxx API integration flow.

analog.com Rev. A | 7 of 391

Figure 5. AD9xxx API Integration Flow

## Integrating the AD9xxx API into an Application

There are five phases to integrating the AD9xxx API into an application as described in the Phase 1: Implement the HAL Functions section through Phase 5: Create the Application section.

# Phase 1: Implement the HAL Functions

The API requires access to several platform specific hardware and system control functions, such as a system delay and sleep function, SPI bus controller functions, GPIO controller, and so on. The end user must provide and implement these functions per the AD9xxx requirements. The prototypes of these functions are defined in the **src/ad9xxx\_api/adi\_inc/adi\_cms\_api\_common.h** header file and are explained in the HAL function pointer data types section of the general API architecture document.

Users develop their own HAL functions based on their hardware dependent platforms. Therefore, depending on their platform, users use different drivers for the peripherals, such as the SPI and GPIO. Users can use their own drivers for these peripherals, or users can use standard drivers if they use an operating system.

The AD9xxx API was developed such that developers can use any driver of their choosing for their platform requirements. However, there are a few platform dependent functions in the API HAL. Do not modify these layers because a specific function prototype was used for these functions. Instead, users must write their own platform functions based on these prototypes in the **adi\_cms\_api\_common.h** file in the **src/AD9xxx\_api/adi\_inc** directory for specific platform requirements.

Per the AD9xxx API specification, the following HAL members are required, at the minimum, for proper operation of the AD9xxx APIs:

- ▶ hal info.spi xfer, pointer to the SPI data transfer function for each AD9xxx device

- ▶ hal info.delay us, pointer to the delay function for each AD9xxx device

- ▶ hal info.log write, pointer to the log write function for each AD9xxx device

- ▶ hal.info.reset pin ctrl, pointer to a function that implements reset pin control for each AD9xxx device

#### Phase 2: Include the AD9xxx API Interface Header Files

The /src/ad9xxx api/adi inc/adi AD9xxx.h header file defines the interface to the AD9xxx API and must be included in the application.

#### Phase 3: Instantiate AD9xxx Device Handle

For each AD9xxx device, the application must instantiate a unique AD9xxx handler reference.

For a full description of the AD9xxx handler, refer to the AD9081/AD9082/AD9986/AD9988 API specification, integration, and porting guide, Revision 1.1.0 or later. This document is part of the API release package.

For each handler instantiated by the application, all the required members of the device handler must be initialized prior to calling any APIs with that handler as a parameter.

Along with the HAL members, the SPI, GPIO, and other peripheral interfaces must also be initialized prior to using any API functions.

## **Example AD9xxx Device Instantiation on the ADS9 Platform**

```

adi AD9xxx device_t AD9xxx_dev = {

.hal_info = {

.sdo = SPI_SDO,

.msb = SPI_MSB_FIRST,

.addr_inc = SPI_ADDR_INC_AUTO,

.log_write = ad59_log_write,

.delay_us = ads9_wait_us,

.spi_xfer = ads9_spi_xfer_AD9xxx,

```

analog.com Rev. A | 8 of 391

```

.reset_pin_ctrl = ads9_hw_rst_pin_ctrl_AD9xxx,

.serdes info = {

.ser_settings = { /* AD9xxx jtx */

.lane settings = {

{.swing setting = AD9XXX SER SWING 850, .pre emp setting = AD9XXX SER PRE EMP ODB, .post emp setting = AD9XXX SER POST EMP ODB},

{.swing_setting = AD9XXX_SER_SWING_850, .pre_emp_setting = AD9XXX_SER_PRE_EMP_ODB, .post_emp_setting = AD9XXX_SER_POST_EMP_ODB),

{.swing setting = AD9XXX SER SWING 850, .pre emp setting = AD9XXX SER PRE EMP ODB, .post emp setting = AD9XXX SER POST EMP ODB),

{.swing_setting = AD9XXX_SER_SWING_850, .pre_emp_setting = AD9XXX_SER_PRE_EMP_ODB, .post_emp_setting = AD9XXX_SER_POST_EMP_ODB},

{.swing_setting = AD9XXX_SER_SWING_850, .pre_emp_setting = AD9XXX_SER_PRE_EMP_ODB, .post_emp_setting = AD9XXX_SER_POST_EMP_ODB),

{.swing setting = AD9XXX SER SWING 850, .pre emp setting = AD9XXX SER PRE EMP ODB, .post emp setting = AD9XXX SER POST EMP ODB), {.swing setting = AD9XXX SER SWING 850, .pre emp setting = AD9XXX SER POST EMP ODB), .post emp setting = AD9XXX SER POST EMP ODB),

{.swing_setting = AD9XXX_SER_SWING_850, .pre_emp_setting = AD9XXX_SER_PRE_EMP_ODB, .post_emp_setting = AD9XXX_SER_POST_EMP_ODB},

.invert mask = 0x00.

.lane mapping = { { 6, 4, 3, 2, 1, 0, 7, 5 }, { 2, 0, 7, 7, 7, 7, 3, 1 } }, /* link0, link1 */

.des settings = { /* AD9xxx jrx */

.boost mask = 0xff,

.inver\bar{t} mask = 0x00,

ctle_filter = { 2, 2, 2, 2, 2, 2, 2, 2 },

.lane_mapping = { { 0, 1, 2, 3, 4, 5, 6, 7 }, { 4, 5, 6, 7, 0, 1, 2, 3 } }, /* link0, link1 */

};

```

### Phase 4: Instantiate User Data Handle.

Another member of the device handler that must be instantiated properly is user\_data. The user can implement a user defined data structure to hold all the peripheral specific configuration settings for the hardware platform that is connected to the AD9xxx. For the AD9xxx, there is a platform API for creating user data (that is, ads9\_user\_data\_create\_AD9xxx()).

# **Phase 5: Create the Application**

Using the AD9xxx APIs provided in the /src/AD9xxx\_api/ adi\_inc/adi\_AD9xxx.h header file, write the application code to initialize, configure, monitor, and log the AD9xxx device per your target application requirements.

An example application based on one of the Analog Devices platforms is provided with every product API as a reference. The example application is in the <code>/src/AD9xxx\_app/app\_ads9/AD9xxx\_app.c</code> folder. The application initializes the platform peripherals it is based on, initializes the device under test (DUT) and any other clocking chips on the evaluation board, and then configures the device for a use case.

This example application can be used to bring up the device in predefined use cases, or it can serve as a starting point for more complicated target applications.

## **API OVERVIEW BLOCK DIAGRAM**

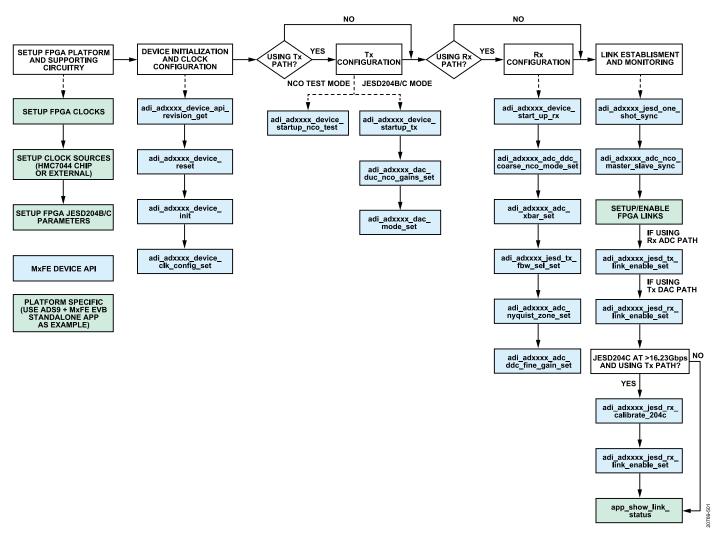

To set up the AD9xxx MxFE products, a variety of system high level API function calls facilitate the setup of the device in a variety of conditions. These function calls cover the configuration of all key feature blocks of the product and abstract the details of the required sequences to set up the chip properly and minimize the burden on the user to complete all steps manually.

Figure 6 shows the general overview of the system bring-up for the MxFE products. The blocks in green represent the stages of the hardware and system configuration outside of the AD9xxx that set up the environment around the product. These steps must be adapted based on the setup of the user and reference some of the example code and steps needed when using the Analog Devices evaluation platform (ADS9v2 field-programmable gate array (FPGA) board with the MxFE evaluation board). The blocks in blue reference the top system level API functions that are called as part of the example standalone application, which is included in the source code package in the src/AD9xxx\_app folder. The example standalone application provides a set of preconfigured use cases that set up various conditions by calling these system high level APIs. For most use cases, the startup process is enough to get the MxFE configured properly for integration in any system.

This startup process consists of four basic functional groups of configurations: initialization and clocking, transmit datapath setup, receive datapath setup, and SERDES link establishment. Figure 6 shows the API function calls needed for each section.

For more details on the API function calls, refer to the AD9081/AD9082/AD9986/AD9988 API specification, integration, and porting guide, Revision 1.1.0 or later. This document is part of the API release package.

analog.com Rev. A | 9 of 391

Figure 6. System High Level API Block Diagram

Although the setup flow shown in Figure 6 sets up the majority of the basic functional blocks in MxFE products, there are block level API function calls underneath each high level section. These block level API function calls can be called independently from some of the higher level API calls to tweak settings in various functional blocks of the chip.

Refer to the AD9081/AD9082/AD9986/AD9988 API specification, integration, and porting guide, Revision 1.1.0 or later, for each of the four basic functional groups and the input parameters available for user configuration. The source code for all API methods is provided in the API source code package and details how each block configuration is executed.

analog.com Rev. A | 10 of 391

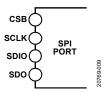

#### SERIAL PERIPHERAL INTERFACE

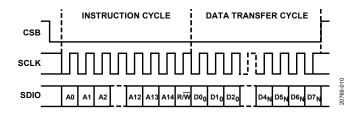

The device is configured using a flexible, synchronous serial communications port, shown in Figure 7, to allow a 3-wire or 4-wire simplified interface with industry standard microcontrollers and microprocessors. An active low input signal at the CSB pin starts and gates a communication cycle used to perform a write or read operation. This input signal must remain low throughout the communication cycle and must return high before returning low again to start a new communication cycle. The SCLK pin synchronizes data to and from the device and runs the internal state machines with all data input appearing on the bidirectional SDIO pin registered on the rising edge of SCLK. All data is driven out of the SDIO pin (or SDO pin for a 4-wire interface) occurring on the falling edge of SCLK during a read operation with the pin going into a high impedance state when the CSB pin returns high. To provide higher noise immunity, the SCLK input features a Schmitt trigger receiver. For timing specifications associated with the SPI port, refer to the device data sheet.

The SPI port is compatible with most synchronous transfer formats to allow a simplified write and read operation to all registers used to configure the device. Register 0x000 is used to configure the SPI, with Bits[7:4] being a mirror image of Bits[3:0]. Before configuring the device, set the self clearing bit, SOFTRESET (Bit 0), to perform a software reset. An LSB first transfer format is supported with the LSBFIRST bit (Bit 1). A multibyte transfer format with an incrementing address is supported with the ADDRINC bit (Bit 2). To enable a 4-wire interface using the SDO pin, set the SDOACTIVE bit (Bit 3) where the SDIO pin is a unidirectional input with the output appearing at the SDO pin.

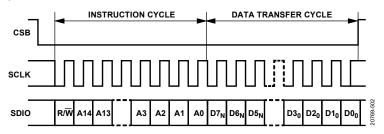

Figure 7. SPI Pins

The default communication cycle with MSB first consists of two phases, as shown in Figure 8. The first phase is the instruction cycle that consists of 16 SCLK cycles that define the operation type and the starting register address. The first bit of the 16-bit instruction word that appears at the SDIO input defines whether the upcoming data transfer is a read or write operation ( $R/\overline{W}$ ). The remaining 15 bits (MSB to LSB format) specify the starting register address for the read or write data transfer operation. For multibyte transfers, the remaining register addresses are generated by the device based on the ADDRINC bit. If this bit is set high, multibyte SPI writes start with the specified address and increment by 1 for every eight bits sent. If the address increment bits are set to 0, the address decrements by 1 for every eight bits sent.

Figure 8. Serial Register Interface Timing, MSB First, Register 0x000, Bit 6 and Bit 1 = 0

The second phase of the communication cycle consists of eight SCLK cycles and is the actual transfer of a data byte between the device and the system controller. To transfer more than one byte (or N + 1 bytes) during the transfer cycle, 8×N SCLK additional cycles are required to ensure that the last byte is transferred. Each time one of the eight clock cycles completes, the internal address index updates such that the next eight data bits transfer to the next register address. Note that a multibyte transfer applies to all registers excluding the registers associated with the transmit and receive digital datapath NCO frequency or phase offset settings. These registers require an additional bit field to be written to such that all NCOs can update simultaneously, if desired, to maintain synchronization.

The SPI port can also support an LSB first data format, as shown in Figure 9, when the LSBFIRST bit is set. In this case, the instruction and data bits must be written from LSB to MSB with the R/W bit following the MSB (or A14) of the address word.

analog.com Rev. A | 11 of 391

## **SERIAL PERIPHERAL INTERFACE**

Figure 9. Serial Register Interface Timing, LSB First, Register 0x000, Bit 6 and Bit 1 = 1

For additional details, see the Analog Devices SPI standard.

## **SPI CONFIGURATION API**

The API provides a HAL to allow users to configure the SPI per the end application requirements. Table 2 details the API functions related to reset, SPI configuration, and SPI read and write operations. For more information, refer to the AD9081/AD9082/AD9986/AD9988 API specification, integration, and porting guide, Revision 1.1.0 or later. This document is part of the API release package.

Table 2. SPI and Reset API Functions

| Function                           | Description                                                                                         |

|------------------------------------|-----------------------------------------------------------------------------------------------------|

| adi_adxxxx_device_init             | Device initialization function. The SPI is configured per the user SPI settings defined by the HAL. |

| adi_adxxxx_device_reset            | Device reset function to perform soft or hard reset.                                                |

| adi_adxxxx_device_spi_register_set | SPI register set function to perform SPI reads per the user SPI operation defined by the HAL.       |

| adi_adxxxx_device_spi_register_get | SPI register get function to perform SPI reads per the user SPI operation defined by the HAL.       |

analog.com Rev. A | 12 of 391

The DAC and ADC cores use sampling clocks that originate from either an external clock source or an on-chip clock multiplier that consists of an integer PLL circuit and voltage-controlled oscillator (VCO). Consider the internal clock multiplier for all applications where its phase noise meets the requirements of the target system, because use of the clock multiplier simplifies external clock distribution as well as multichip synchronization, if required. If the phase noise requirement cannot be met with the clock multiplier, supply an external clock equal to the desired DAC clock rate.

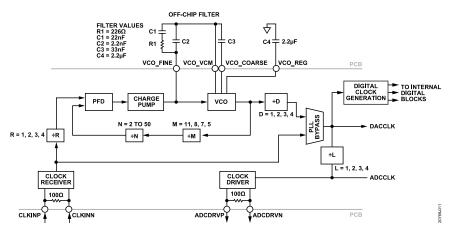

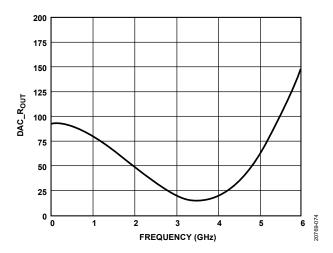

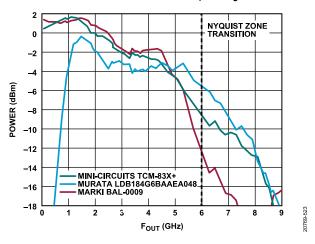

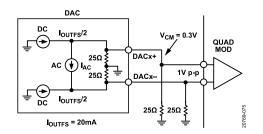

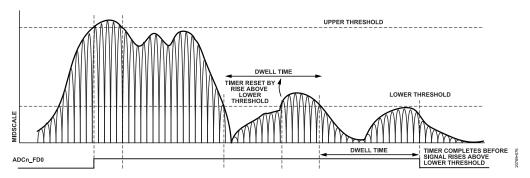

Figure 10 shows a block diagram of the internal clock multiplier with the clock distribution path that provides both DAC and ADC clocks, as well as a digital block that generates various internal system clocks. Table 3 lists the SPI registers associated with the clock and clock distribution. To access these registers, first set the SPI\_EN\_D2ACENTER bit field. A differential input clock signal is applied to the clock receiver input pins, CLKINP and CLKINN, to meet the amplitude and frequency requirements stated in the device data sheet. The PLL\_BYPASS bit in Register 0x0094 determines if the sampling clock source originates from the external source or the PLL. If the external source is selected, the PLL circuitry automatically powers down if EN\_PDPLL\_WHENBYPASS (Bit 4) in Register 0x0094 is set. In either case, the DAC clock is the primary clock and the ADC clock is derived from the DAC clock. The sampling clock passed onto the DAC core must be set to the desired DAC clock rate. The ADC clock is a divided version of the DAC clock with the divider circuit controlled by Register 0x0180. The divider setting of 1, 2, 3, or 4 is set by the ADCDIVN\_DIVRATIO\_SPI bits, and the ADCDIVN\_PD bit provides a power-down option. The user can also export the internal ADC clock to other devices via a differential clock driver.

### **CLOCK MULTIPLIER**

The clock multiplier uses an integer type PLL synthesizer to generate the internal DAC sampling clock. The relation between the DAC clock and the reference clock is as follows:

$$f_{DAC} = (f_{CLKIN} \times \frac{(M_{VCO} \times N_{VCO})}{R})/D \tag{1}$$

where:

$f_{DAC}$  is the desired DAC clock rate.

$M_{VCO}$  is the VCO prescaler feedback divider ratio with a value of 5, 7, 8, or 11 (M = 8 is the nominal setting).

$N_{VCO}$  is the VCO feedback divider ratio ranging from 2 to 50.

R is the reference clock divider ratio with a value of 1, 2, 3, or 4. Its value is set such that the phase frequency detector (PFD) frequency (f<sub>PFD</sub>) operates within a range of 25 MHz to 750 MHz.

$f_{CLKIN}$  is the input frequency of the differential signal appearing across CLKINP or CLKINN.

D is the VCO to DACCLK divider ratio with a value of 1, 2, 3, or 4.

Figure 10. PLL and Clock Distribution Path Block Diagram

The PLL VCO is specified to operate over a frequency range of 5.8 GHz to 12 GHz. The VCO phase noise improves when operating with a lower VCO frequency. When  $f_{DAC}$  operation is as low as possible, but above 5.8 GHz, the VCO divider ratio must be at the minimum setting (D = 1), which results in the lowest valid VCO frequency, which is within the VCO specified range. Because the VCO divider does not include a reset capability, its output phase cannot be made deterministic via an external synchronization signal (such as SYSREF) when D > 1.

analog.com Rev. A | 13 of 391

Therefore, sample accurate deterministic latency accuracy or multichip synchronization (MCS) is not possible due to this phase ambiguity when using the clock multiplier PLL with D > 1.

When the PLL divider settings are configured, calibrate the VCO to ensure that a clock source remains stable over the fully specified device operating range. To initiate the VCO calibration, set the D\_CAL\_RESET bit (Register 0x00E2, Bit 1) high to reset the calibration engine, and then low to trigger the reset. The PLL\_LOCK\_SLOW bit and/or the PLL\_LOCK\_FAST bit in Register 0x2008 can be read after the D\_PLL\_LOCK\_CONTROL bit in Register 0x00EC is set to determine if the PLL has achieved a locked and stable state before proceeding further in the device initialization process.

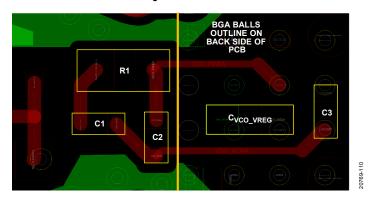

Referring to Figure 10, the following external passive components are required when using the clock multiplier:

- ▶ The PLL loop fine filter that consists of R1, C1, and C2

- ▶ The PLL coarse loop filter that consists of C3 set to 33 nF, which does not impact phase noise.

- The VCO regulator bypass capacitor, C4, set to 2.2 μF.

Place these passive components on the back side of the printed circuit board (PCB) in close proximity to the device. If the clock multiplier is powered down, and a direct external clock is applied to the clock receiver input pins, these passive components are not needed. The VCO\_COARSE, VCO\_FINE, VCO\_VCM, and VCO\_VREG pins can be left unconnected.

The PLL loop filter and charge pump settings can be customized according to the PFD frequency, reference clock phase noise, and DAC output phase noise requirements. The charge pump output current can be set from 0 mA to 6.3 mA in the 6-bit D\_CP\_CURRENT bit field of Register 0x00E4, where the default setting is 1.9 mA, and a setting of 11 1111 corresponds to 6.3 mA.

The default charge pump setting with the values shown in Figure 10 results in a phase margin of approximately 80° if the PFD frequency (f<sub>PFD</sub> = f<sub>CLKIN</sub>/R) is set to 500 MHz. This setting also corresponds to a PLL loop bandwidth of 295 kHz when operating with a VCO output frequency of 9 GHz. Note that increasing the VCO output frequency to 12 GHz reduces the PLL loop bandwidth to 230 KHz. Doubling the charge pump level results in almost a doubling of the bandwidth that can improve jitter and phase noise performance.

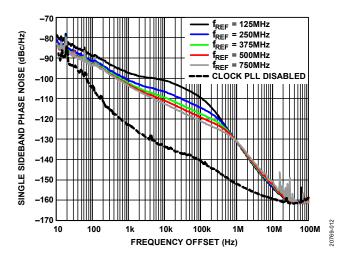

General guidelines for optimizing phase noise performance include the following:

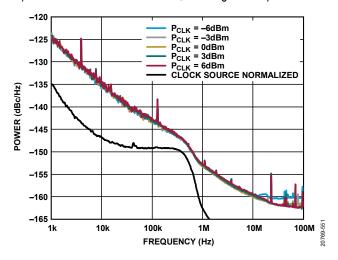

- ▶ Use the highest possible f<sub>PFD</sub> to minimize the contribution of in band noise from the PLL and reference source. Figure 11 shows how the PLL phase noise varies as a function of the f<sub>PFD</sub>, whereas the loop filter and charge pump values remain constant. Note that the trace corresponding to clock PLL disabled represents the extrapolated phase noise when the clock input is driven from an R&S SMA100B RF generator.

- Set the PLL filter bandwidth such that the PLL in band noise contribution intersects with the VCO open-loop noise contribution, which minimizes the overall combined contribution of both noise sources.

Together with the previous guidelines, general steps for configuring the clock multiplier PLL to obtain the required input reference clock frequency are as follows:

- 1. The DAC sample clock frequency is the starting point for configuring the clock multiplier PLL. Once this frequency is determined, the other settings can be established. This step is also necessary for ADC only versions. The ADC clock is derived from the internal clock that was used for the DACs.

- Choose the VCO divider ratio (D), which is set using the PLL\_DIVIDEFACTOR bit field. D can be 1, 2, 3, or 4. D must be chosen so that

the VCO frequency (DAC sample clock frequency×D) is from 6000 MHz to 12000 MHz. The frequency of the DAC sample clock is (VCO

frequency)/D.

- 3. Choose the ADC clock divide ratio (L), which is set using the ADCDIVN\_DIVRATIO\_SPI bit field. L can be 1, 2, 3 or 4. The ADC sample clock frequency is the DAC clock frequency/L. If the ADC clock is not needed, the ADC clock divider can be powered down.

- 4. The loop divider values M and N are then chosen so that M×N is from 10 to 550. M can be 5, 7, 8 or 11 and is set using the D\_CONTROL\_HS\_FB\_DIV bit field. N can be any integer from 2 through 50 and is set using the D\_DIVIDE\_CONTROL bit field. Start with M = 5 and vary N. If the desired characteristics cannot be met with M = 5, change the M value and vary N to find the desired configuration.

- 5. Choose the reference clock divider ratio (R) value to be 1, 2, 3, or 4. R is set using the D\_REFIN\_DIV bit field. After R is set, the frequency of the reference clock applied to the CLKINP and CLKINN pins is known.

The frequency of the applied reference clock is represented by the following equation:

$$f_{CLKIN} = \frac{f_{DAC} * D}{M_{VCO} * N_{VCO}} * R \tag{2}$$

analog.com Rev. A | 14 of 391

Note that the values contained in the bit fields are not necessarily the same as the value of the parameters they represent. For example, to set L = 1, ADCDIVN DIVRATIO SPI must be set to 00, not 01. See Table 3 for more information.

Table 3. PLL Clock Multiplier Registers

| Address | Bits  | Bit Name             | Description                                                                   |

|---------|-------|----------------------|-------------------------------------------------------------------------------|

| 0x00D0  | 2     | SPI_EN_D2ACENTER     | Enable SPI access to bit fields associated with PLL.                          |

| 0x0091  | 0     | ACLK_POWERDOWN       | Power down clock receiver.                                                    |

| 0x0093  | [1:0] | PLL_DIVIDEFACTOR     | Programmable divide-by-D value.                                               |

| 0x0094  | 4     | EN_PDPLL_WHENBYPASS  | Enable power down of the PLL clock multiplier when the PLL is in bypass mode. |

|         | 0     | PLL_BYPASS           | Enable PLL bypass.                                                            |

| 0x0180  | 4     | ADCDIVN_PD           | Power down ADC clock divider.                                                 |

|         | [1:0] | ADCDIVN_DIVRATIO_SPI | ADC clock divider setting, VCO_L. Divide-by-1 = 00, divide-by-4 = 11.         |

| 0x0196  | [4:0] | ADC_DRIVER_DATA_CTRL | ADC driver-output voltage swing level control.                                |

| 0x0198  | 0     | PD_ADC_DRIVER        | Power down ADC driver.                                                        |

| 0x00E2  | 1     | D_CAL_RESET          | VCO calibration.                                                              |

| 0x00E3  | [1:0] | D_REFIN_DIV          | Programmable divide-by-R value.                                               |

| 0x00E4  | [5:0] | D_CP_CURRENT         | Charge pump current setting.                                                  |

| 0x00E9  | [5:0] | D_DIVIDE_CONTROL     | Programmable divide-by-N <sub>VCO</sub> value.                                |

| 0x00EC  | [5:4] | D_CONTROL_HS_FB_DIV  | Programmable divide-by-M <sub>VCO</sub> value.                                |

|         | [2:1] | D_PLL_LOCK_CONTROL   | 00: no locks enabled.                                                         |

|         |       |                      | 01: fast lock enabled.                                                        |

|         |       |                      | 10: slow lock enabled.                                                        |

|         |       |                      | 11: fast lock, slow clock enabled.                                            |

| 0x2008  | 1     | PLL_LOCK_FAST        | High value indicates PLL lock.                                                |

|         | 0     | PLL_LOCK_SLOW        | High value indicates PLL lock.                                                |

Figure 11. Single Sideband Phase Noise vs. Frequency Offset for Different PLL Reference Clock (f<sub>PFD</sub>), Output Frequency (f<sub>OUT</sub>) = 1.8 GHz, f<sub>DAC</sub> = 12 GSPS, PLL Enabled with Exception of External 12 GHz Clock Input with Clock PLL Disabled

# **CLOCK RECEIVER INPUT**

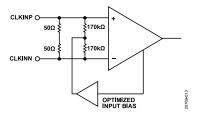

Figure 12 shows a simplified diagram of the clock receiver input that supports up to 12 GHz operation. The clock receiver input has a self biased input with a nominal common-mode voltage ( $V_{CM}$ ) of 0.5 V and a differential impedance of 100  $\Omega$  across the input pins, CLKINP and CLKINN. To maintain the proper common-mode voltage bias, AC coupling of the external clock source to the clock receiver input is

analog.com Rev. A | 15 of 391

recommended. Limit the maximum differential input signal to 1.8 V peak-to-peak, which corresponds to a power level of approximately 6 dBm for a sine wave source. To disable the clock receiver, set the ACLK POWERDOWN bit in Register 0x0091.

Figure 12. Clock Receiver Input Simplified Equivalent Circuit

The additive jitter and phase noise contribution from the clock receiver depends on the input slew rate and input voltage level. This additive jitter can limit the achievable noise floor performance of a DAC or ADC when operating under large signal conditions with high frequency content. To improve the phase noise performance, use a higher slew rate clock input signal.

Figure 13 shows the phase noise of the clock receiver path for different clock input sine wave drive levels at 12 GHz. The phase noise is measured with the DAC output reconstructing a 1.8 GHz full-scale output signal. The phase noise of the 12 GHz clock source (normalized to 1.8 GHz) is also provided to show the additive phase noise from the device. The plot shows that the drive level mostly impacts the high frequency offset phase noise (> 1 MHz) with drive levels above -3 dBm, resulting in the optimal wide offset performance.

Figure 13. Single Sideband Phase Noise vs. Frequency Offset for Different Clock Input Power (P<sub>CLK</sub>), f<sub>OUT</sub> = 1.8 GHz, External 12 GHz Clock Input with Clock PLL

Disabled

The quality of the clock source and the interface to the CLKINP pin and CLKINN pin directly impact AC performance. Ensure that the external clock path remains clean of any power supply or PCB coupling induced noise, and select the phase noise and spur characteristics of the clock source to meet the target application requirements.

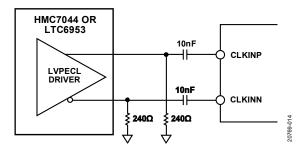

High speed logic families that provide low voltage positive emitter coupled logic (LVPECL) or current mode logic (CML) output drivers are available on the HMC7044 and LTC6953 clock generation and distribution IC and are preferred because of the low jitter and high slew rates provided. Figure 14 shows an AC-coupled interface with an LVPECL driver. Note that, for a CML driver interface, the 240  $\Omega$  resistors must be removed, as shown in Figure 14.

analog.com Rev. A | 16 of 391

Figure 14. Differential LVPECL Sample Clock

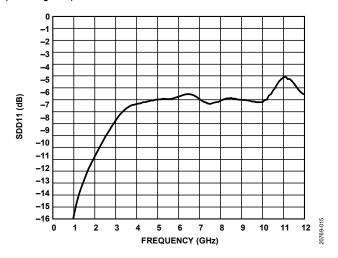

Figure 15 shows the differential input return loss curve for the clock inputs up to 12 GHz with a reference impedance of 100  $\Omega$ . The S-parameters are available for download on the AD9081 or AD9082 product page. Consider an S-parameter evaluation using the component models with PCB extraction when optimizing the power transfer between the external clock driver and clock receiver input.

Figure 15. Clock Receiver Differential Input Return Loss

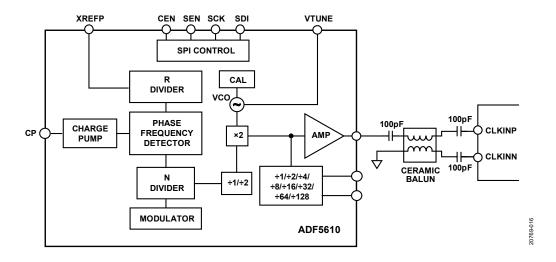

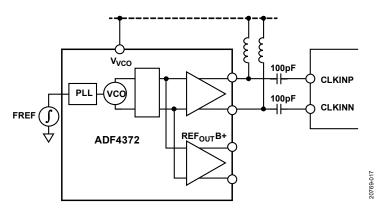

For high RF clock frequency generation beyond 4.5 GHz, a wideband synthesizer IC, such as the ADF5610 or ADF4372, can be used. The ADF5610 and ADF4372 have fundamental VCO modes extending up to 7.3 GHz and 8.0 GHz, respectively, with an internal clock doubler used to synthesize output frequency beyond the fundamental VCO limit. Figure 16 shows a recommended interface when the clock source is a single-ended signal, and a ceramic balun, such as the Mini-Circuits NCR2-113+, is used to convert the single-ended signal to a differential signal. Note that using the ADF5610 results in clock output multiplier spurs in the 30 dB range. Therefore, a band-pass filter may be necessary to attenuate these subharmonics.

Figure 17 shows a differential CML interface using the ADF4372, which is suitable for operation below an 8 GHz output.

analog.com Rev. A | 17 of 391

Figure 16. Balun Coupled Differential Clock

Figure 17. ADF4372 Differential CML Sample Clock

# **CLOCK OUTPUT DRIVER**

An optional differential clock output driver with on-chip  $100 \Omega$  termination is available at the ADCDRVP pin and ADCDRVN pin to provide a clock equal to the ADC sample rate, as shown in Figure 10. To power down the output driver, set the PD\_ADC\_ DRIVER bit in Register 0x0198. The output provides a differential clock output with a nominal common-mode voltage of 0.5 V. The voltage swing level can be varied via the ADC\_DRIVER\_ DATA\_CTRL bit in Register 0x0196 with the voltage swing set according to the following relationship:

Swing = 993 mV - code×99 mV

where the code can assume a value of 0 to 20 and an inversion of CLKOUT polarity occurring for codes 11 to 20. The driver output impedance remains relatively constant for different settings.

## **CLOCK CONFIGURATION APIS**

Table 4 lists the API functions related to the configuration and control of the input clock receiver and the clock output driver as described in this section.

The adi\_adxxxx\_device\_clk\_config\_set function is a high level function that configures the device appropriated per Analog Devices recommended setting, based on the DAC sampling frequency, ADC sampling frequency, and applied reference input of the desired use case clocking scheme. However, if the user wants to configure each block of the input clock receiver, on-chip PLL, and distribution dividers, the APIs are provided in Table 4.

For more information, refer to the AD9081/AD9082/AD9986/AD9988 API specification, integration, and porting guide, Revision 1.1.0 or later. This document is part of the API release package.

analog.com Rev. A | 18 of 391

## Table 4. Input Clock Receiver and Output Driver Configuration and Control APIs

| Function Call                             | Description                                                                                              |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------|

| adi_adxxxx_device_clk_config_set          | Function to set the input clock receiver per the desired reference clock and sampling clock requirements |

| adi_adxxxx_device_clk_pll_lock_status_get | Function to get the on-chip PLL status                                                                   |

| adi_adxxxx_adc_clk_enable_set             | Function to enable/power up the input clock receiver                                                     |

| adi_adxxxx_adc_clk_out_enable_set         | Function to enable/power up the clock output driver                                                      |

analog.com Rev. A | 19 of 391

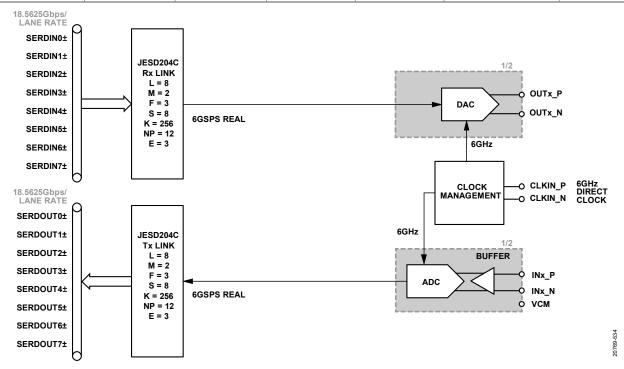

The device employs serial interfaces that comply to the JESD204C standard for the ADC and DAC paths, including the JESD204B backward compatible option.

The main differences introduced in the JESD204C standard as employed on this device are the additional 64-bit/66-bit encoding scheme, the respective synchronization process (eliminating the need for the SYNCxOUTB± pins and SYNCxINB± pins), and the recommended operating link rates.

If the 8-bit/10-bit link layer option is selected, the link operation complies to both the JESD204B and JESD204C standards and the link lane rates can be between 1.5 Gbps and 15.5 Gbps. If the 64-bit/66-bit link layer option is selected, the link operation complies to the JESD204C standard, including the new synchronization process (SYNCxOUTB± pins and SYNCxINB± pins are not used), and the link lane rates can be between 6 Gbps and 24.75 Gbps. Table 5 shows the high level differences between using the 8-bit/10-bit and 64-bit/66-bit link layers.

This section of the user guide focuses on the common requirements for the ADC and DAC paths.

#### **NEW FEATURES IN THE JESD204C STANDARD**

The following subsections contain an overview of JESD204C specifications that are new or updated when compared to those in the JESD204B standard.

## **Terminology and Parameters**

There are new terms and configuration parameters introduced in the JESD204C standard that are used to describe the functions associated with the 64-bit/66-bit link layer (see Table 6). These terms are detailed throughout the document in the context of the JESD204C transmitter and JESD204C receiver physical, link, and transport layers.

Table 5. Differences Between 8-Bit/10-Bit and 64-Bit/66-Bit Link Layer Operations

| Function/Attribute                                                                                                   | 8-Bit/10-Bit Encoding                                                     | 64-Bit/66-Bit Encoding                                                                                                                                   |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Payload Delivery Efficiency                                                                                          | 80% encoding efficiency                                                   | 96.97% encoding efficiency                                                                                                                               |  |

| SYNCxOUTB± and SYNCxINB± Signal                                                                                      | Yes, from JESD204B receiver to JESD204B transmitter                       | Not used, entirely feed forward                                                                                                                          |  |

| Link Initialization                                                                                                  | Code group synchronization (CGS) + initial lane alignment sequence (ILAS) | Synchronization header alignment, extended multiblock alignment, and extended multiblock alignment achieved using embedded synchronization header stream |  |

| Scrambling                                                                                                           | Optional (recommended)                                                    | Required                                                                                                                                                 |  |

| Error Monitoring  8-bit/10-bit disparity, not in table (NIT), and unexpected K-characters (UEKC) errors are detected |                                                                           | Cyclic redundancy check (CRC) checks per multiblock of data (2048 bits                                                                                   |  |

| Deterministic Latency and Multichip Sync                                                                             | Aligned to local multiframe clock (LMFC)                                  | Aligned to a local extended multiblock clock (LEMC)                                                                                                      |  |

| Lane Rate                                                                                                            | 1.5 Gbps ≤ lane rate ≤ 15.5 Gbps                                          | 6 Gbps ≤ lane rate ≤ 24.75 Gbps                                                                                                                          |  |

analog.com Rev. A | 20 of 391

Table 6. New Terms and Parameters Defined in JESD204C

| Term                                                                        | Definition                                                                                                                          |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Block                                                                       | A structure starting with a 2-bit synchronization header containing 66 bits or 80 bits (BkW) total (always 66 bits for the device). |

| Block width, the number of bits in a block (always 66 bits for the device). |                                                                                                                                     |

| cmd                                                                         | Command, as related to the command channel.                                                                                         |

| Command Channel                                                             | Data stream using extra bandwidth afforded from synchronization headers.                                                            |

| E                                                                           | The number of multiblocks in an extended multiblock.                                                                                |

| EMB_LOCK                                                                    | A state that asserts extended multiblock alignment is achieved.                                                                     |

| EoEMB                                                                       | End of extended multiblock identifier bit (Bit 22 of the synchronization word).                                                     |

| EoMB                                                                        | End of multiblock sequence (00001), decoded from the synchronization header stream.                                                 |

| Extended Multiblock                                                         | A set of data containing one or more multiblocks.                                                                                   |

| LEMC                                                                        | Local extended multiblock clock.                                                                                                    |

| Multiblock                                                                  | A set of data containing 32 blocks.                                                                                                 |

| PCS                                                                         | Physical coding sublayer.                                                                                                           |

| SH_LOCK                                                                     | A state that asserts synchronization header alignment is achieved.                                                                  |

| Synchronization Header (SH)                                                 | Two bits that guarantee a transition precede every block.                                                                           |

| Synchronization Transition Bit                                              | Decoded synchronization header (2b'10 = 0, 2b'01 = 1).                                                                              |

| Synchronization Word                                                        | 32 synchronization transition bits from a multiblock.                                                                               |

# **Physical Layer Updates**

The JESD204C physical layer specification and the implementation on the device supports operation with the 8-bit/10-bit (JESD204B) and 64-bit/66-bit (JESD204C) link layers.

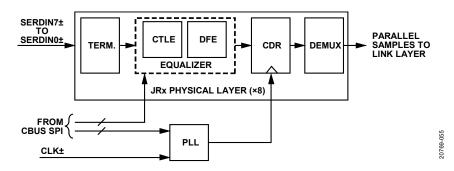

JESD204C introduces data interface classes and defines two categories of classes, Category B and Category C. There are three classes defined for each category. Table 7 lists the lane rates associated with each category. For Category C, there are three subclasses defined to minimize link power dissipation for a variety of channel types: C-S (short), C-M (medium) and C-R (reflective). Each class is a superset of the previous class. Table 8 lists the architectural differences between the classes. The device implements a class C-M interface on both the ADC and DAC paths, although the lane rate is limited to 1.5 Gbps on the low end (when employing 8-bit/10-bit encoding) and 24.75 Gbps on the high end (when employing 64-bit/66-bit encoding).

Table 7. Lane Data Rates for Data Interface Classes

| Data Interface Class | Minimum Data Rate (Gbps) | Maximum Data Rate (Gbps) |

|----------------------|--------------------------|--------------------------|

| B-3                  | 0.3125                   | 3.125                    |

| B-6                  | 0.3125                   | 6.375                    |

| B-12                 | 6.375                    | 12.5                     |

| Category C           | 6.375                    | 32                       |

Table 8. JESD204C 32 Gbps Interface Device Class Features

| Class | Relative Power | Tx FFE <sup>1</sup> (dB) | Rx CTLE <sup>2</sup> (dB) | Rx DFE <sup>3</sup> (No. of Taps) |

|-------|----------------|--------------------------|---------------------------|-----------------------------------|

| C-S   | Low            | 9.5                      | 6                         | 0                                 |

| C-M   | Medium         | 9.5                      | 9                         | 3                                 |

| C-R   | High           | 9.5                      | 12                        | 14                                |

<sup>&</sup>lt;sup>1</sup> FFE is feedforward equalization.

# **Transport and Link Layer**

The transport layer provides mapping between converter samples and octets. The 8-bit/10-bit and the 64-bit/66-bit link layers use the same octet format and there is no difference in the transport layer that depends on the encoding scheme.

The only difference between using the two encoding schemes is that the octets sent to the 64-bit/66-bit link layer must be scrambled. For the 8-bit/10-bit link layer, scrambling is optional.

analog.com Rev. A | 21 of 391

<sup>&</sup>lt;sup>2</sup> CTLE is continuous time linear equalizer.

<sup>&</sup>lt;sup>3</sup> DFE is decision feedback equalizer.

When using the 8-bit/10-bit link layer option of JESD204C, the device is fully compatible with the JESD204B specification and all that the specification implies. These implications include the use of K28 characters for CGS, ILAS, and character replacement as well as the SYNCxOUTB± pins and SYNCxINB± pins used to initiate synchronization and report errors from the receiver back to the transmitter.

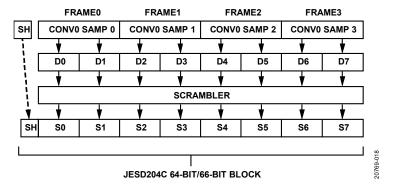

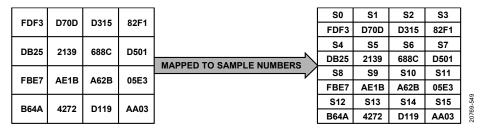

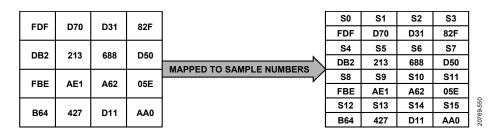

When operating with 64-bit/66-bit encoding, the use of the SYNCxOUTB± pins and SYNCxINB± pins is eliminated and there is no compatibility with JESD204B. There is no encoding of the octets. The octets are packed into a 64-bit block of data. The entire block is then scrambled and has a 2-bit synchronization header appended. This format is shown in Figure 18, where D[0:7] represents the eight data octets, S[0:7] represents the scrambled octets, and SH is the 2-bit synchronization header.

Figure 18. 64Bbit/66-Bit Block Format Example for LMFS = 1.1.2.1, N = N' = 16

The synchronization header is a 2-bit, unscrambled value at the beginning of each block. The header contents are interpreted to decode a single synchronization transition bit. The synchronization header bits must be either a 0 to 1 sequence to indicate a Logic 1 or a 1 to 0 sequence to indicate a Logic 0.

Table 9 shows the synchronization header and synchronization transition bit values.

Table 9. Synchronization Header Bit Values

| Synchronization Header Bits[0:1] | Synchronization Transition Bit Value |

|----------------------------------|--------------------------------------|

| 00                               | Invalid                              |

| 01                               | 1                                    |

| 10                               | 0                                    |

| 11                               | Invalid                              |

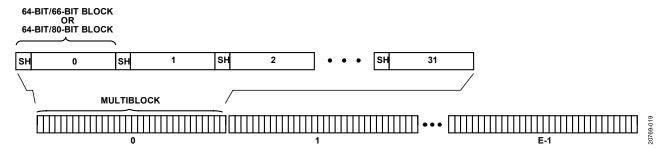

## Multiblocks (MB) and Extended Multiblocks (EMB)

There are 32 blocks in a JESD204C multiblock. The 32 synchronization transition bits in each multiblock make up a 32-bit synchronization word. The functions within the synchronization word are described in the Synchronization Word section. An extended multiblock is a container of E multiblocks and must contain an integer number of frames. When a multiblock does not contain an integer number of frames, E must be >1. Figure 19 shows the format of the multiblock and extended multiblock.

Figure 19. JESD204C Multiblock and Extended Multiblock Format

analog.com Rev. A | 22 of 391

The JESD204C standard supports a multiblock that is either 2112×(32×66) bits or 2560×(32×80) bits, depending on which 64-bit encoding scheme is used. A multiblock in the AD9081 and AD9082 is always 2112 (32×66) bits because 64-bit/ 80-bit encoding is not supported. For most implementations and configurations, an extended multiblock is one multiblock.

The E parameter is introduced in JESD204C and determines the number of multiblocks in the extended multiblock. The default value for E is 1. E must be > 1 for configurations where the number of octets in the frame (F) is not a power of two and is typically associated with modes where NP = 12.

This requirement ensures that the extended multiblock boundary coincides with a frame boundary.

The equation for E is given as the following:

$E = (K \times F)/256$

when 256 mod F != 0

E must be an integer and the number of frames in a multiframe (K) must be set appropriately.

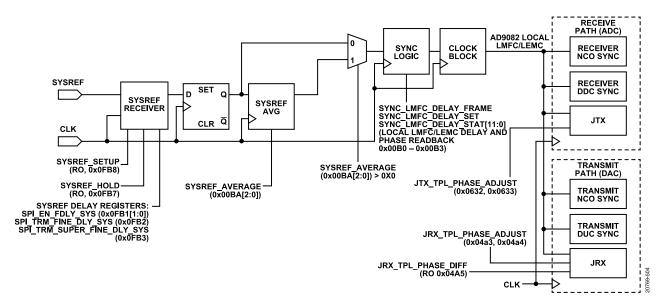

LEMC is the local extended multiblock counter and is roughly equivalent to the LMFC in the 8-bit/10-bit link layer. The SYSREFN and SYSREFP input signal aligns all LEMCs in a system and the LEMC boundaries are used to determine synchronization and lane alignment.

# **Synchronization Word**

The 32-bit synchronization word is constructed from each of the sample headers from the 32 blocks within the multiblock where Bit 0 is transmitted first. The synchronization word is used to enable lane synchronization, error detection, and deterministic latency.

There are seven bits (CMD, Bits[6:0]) that provide a command channel for the transmitter to communicate to the receiver. However, this command channel is not supported on the AD9081 and AD9082 and these bits are always zeros for the device.

Table 10 describes the different synchronization word fields and functions.

Table 10. Synchronization Word Fields and Functions

| Synchronization Word Bit | Bit Name | Function                                                                  |

|--------------------------|----------|---------------------------------------------------------------------------|

| 0                        | CRC11    | Bits[11:9] of the 12-bit CRC check applicable to the previous multiblock. |

| 1                        | CRC10    |                                                                           |

| 2                        | CRC9     |                                                                           |

| 3                        | 1        | Always 1.                                                                 |

| 4                        | CRC8     | Bits[8:6] of the 12-bit CRC check applicable to the previous multiblock.  |

| 5                        | CRC7     |                                                                           |

| 6                        | CRC6     |                                                                           |

| 7                        | 1        | Always 1.                                                                 |

| 8                        | CRC5     | Bits[5:3] of the 12-bit CRC check applicable to the previous multiblock.  |

| 9                        | CRC4     |                                                                           |

| 10                       | CRC3     |                                                                           |

| 11                       | 1        | Always 1.                                                                 |

| 12                       | CRC2     | Bits[2:0] of the 12-bit CRC check applicable to the previous multiblock.  |

| 13                       | CRC1     |                                                                           |

| 14                       | CRC0     |                                                                           |

| 15                       | 1        | Always 1.                                                                 |

| 16                       | Cmd6     | Bits[7:5] of the 7-bit command channel (not supported, always 0).         |

| 17                       | Cmd5     |                                                                           |

| 18                       | Cmd4     |                                                                           |

| 19                       | 1        | Always 1.                                                                 |

| 20                       | Cmd3     | Bit 3 of the 7-bit command channel.                                       |

| 21                       | 1        | Always 1.                                                                 |

| 22                       | EoEMB    | End of extended multiblock bit.                                           |

| 23                       | 1        | Always 1.                                                                 |

analog.com Rev. A | 23 of 391

Table 10. Synchronization Word Fields and Functions (Continued)

| Synchronization Word Bit | Bit Name | Function                                |

|--------------------------|----------|-----------------------------------------|

| 24                       | Cmd2     | Bits[2:0] of the 7-bit command channel. |

| 25                       | Cmd1     |                                         |

| 26                       | Cmd0     |                                         |

| 27                       | 0        | End of multiblock pilot signal.         |

| 28                       | 0        |                                         |

| 29                       | 0        |                                         |

| 30                       | 0        |                                         |

| 31                       | 1        |                                         |

#### **CRC-12 Encoder**

The CRC-12 encoder in the JESD204C transmitter takes in the 2048 scrambled data bits of each multiblock and computes 12 parity bits. These parity bits are transmitted to the receiver during the subsequent multiblock.

The receiver computes 12 parity bits from each multiblock of data received. The 12 bits are compared to the bits that were received over the command channel. If the parity bits do not match, there is at least one error in the received data. See the 64-Bit/66-Bit Link Establishment Overview section for details.

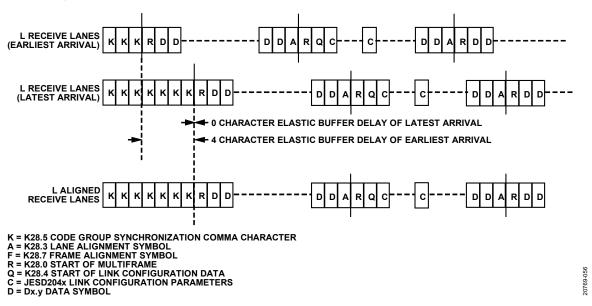

### 8-BIT/10-BIT LINK ESTABLISHMENT OVERVIEW

When using the 8-bit/10-bit link layer, the link establishment process follows the protocol established in the original JESD204B/C standard (and subsequent versions). Using K28 characters and the SYNC~ signals, the link first establishes CGS, then frame synchronization (FS) and ILAS prior to transmitting sample data in the user data phase.

During the user data phase, character replacement (inserting K28.x characters) is used to monitor frame and multiframe alignment while an error checking circuit in the JESD204B/C receiver monitors incoming data for 8-bit/10-bit errors (running disparity, NIT, UEKC). Details are not provided because this protocol is well established. For more details, refer to the Analog Devices webcast on the JESD204B data link layer.

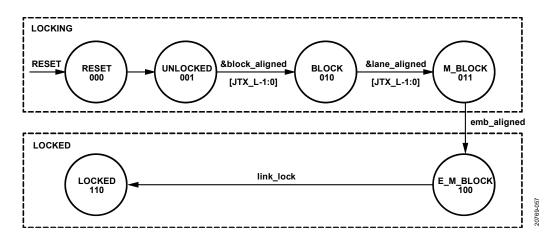

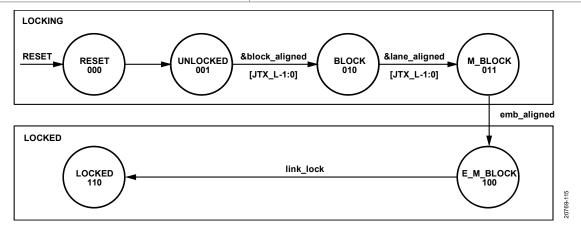

## 64-BIT/66-BIT LINK ESTABLISHMENT OVERVIEW

The link establishment process when using the 64-bit/66-bit link layer starts automatically when the link is powered on. The SYNC~ signal, or synchronization request, is not required. The process begins with synchronization header synchronizations, then progresses to extended multiblock synchronization, and then to extended multiblock alignment. Details on the 64-bit/66-bit link establishment process can be found in the 64-Bit/66-Bit Link Layer and Link Establishment section.

## **SERDES PLL AND CONFIGURATION**

Because the JESD204B/C receiver and transmitter share the SERDES PLL, consider the following during PLL configuration:

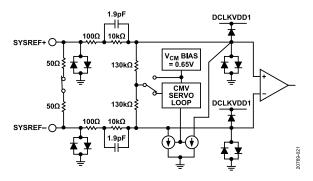

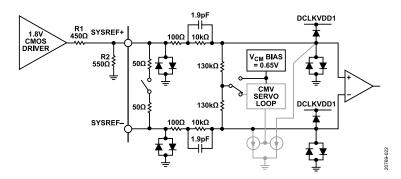

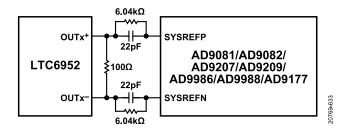

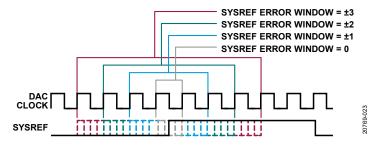

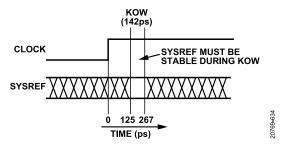

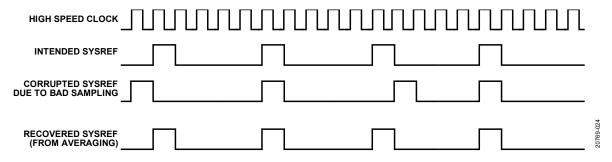

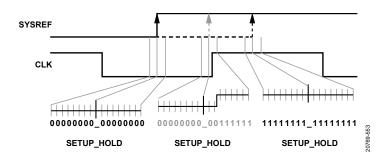

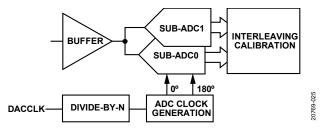

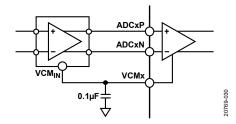

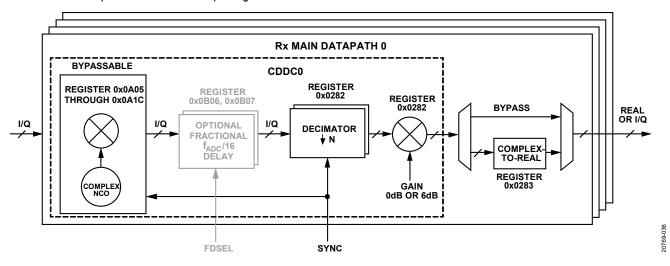

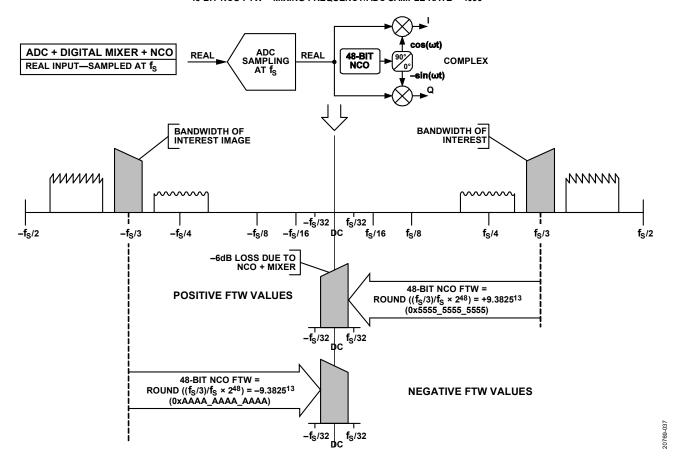

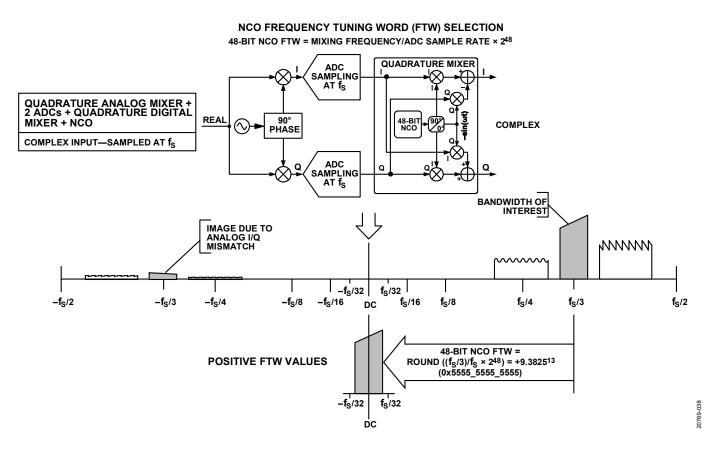

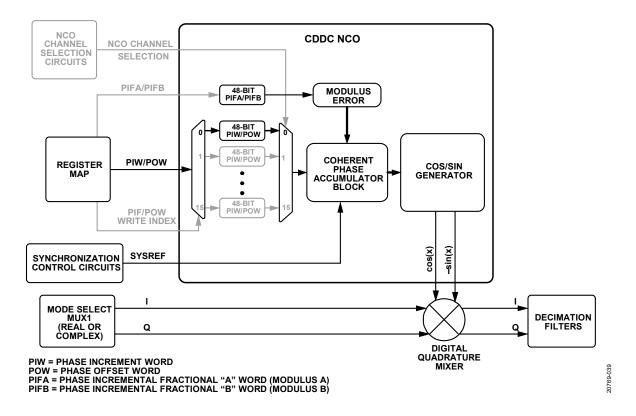

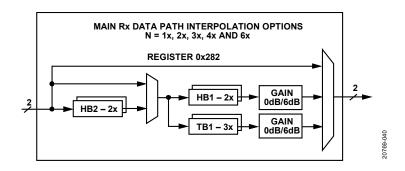

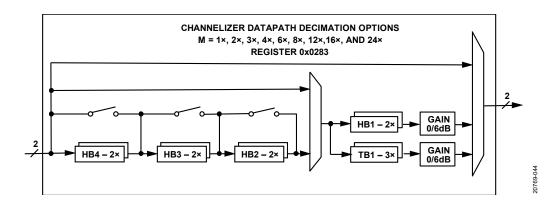

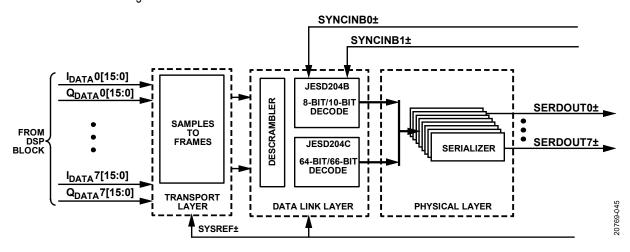

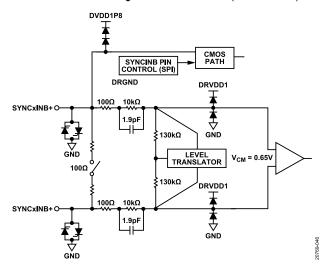

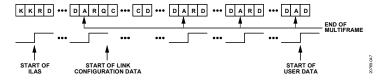

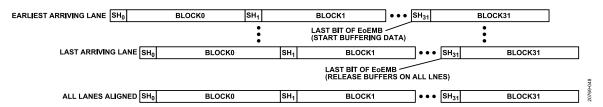

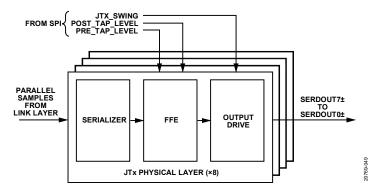

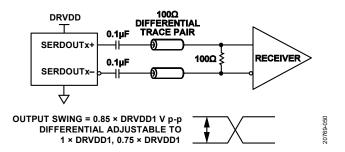

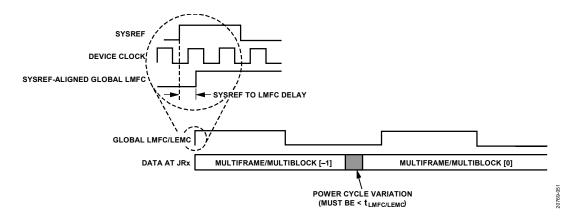

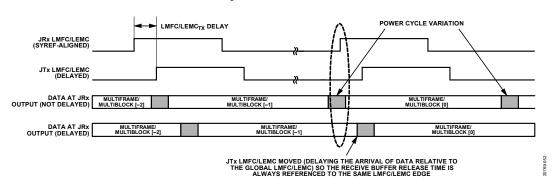

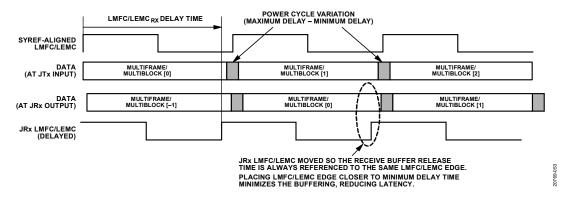

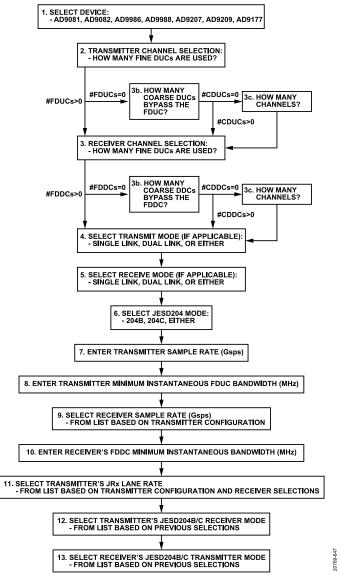

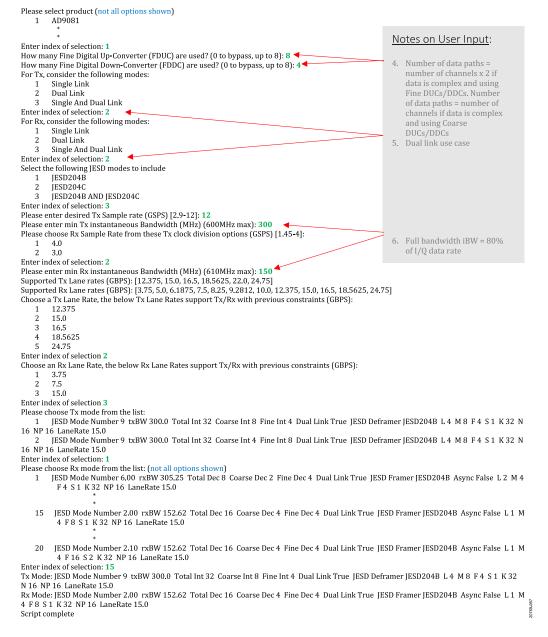

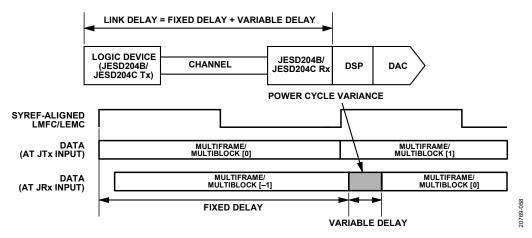

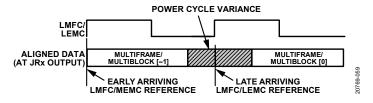

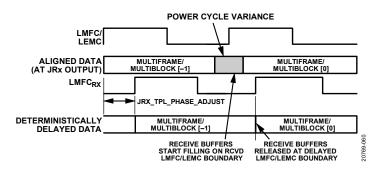

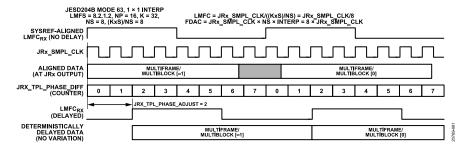

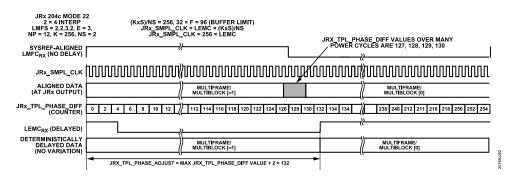

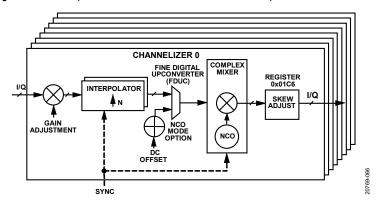

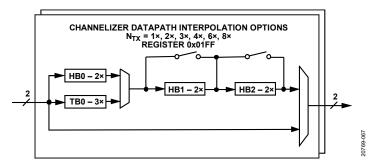

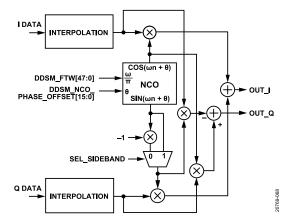

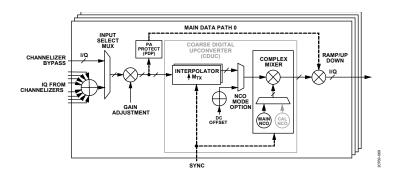

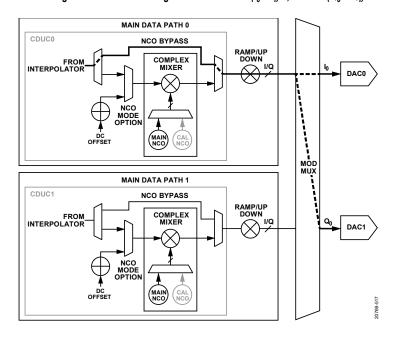

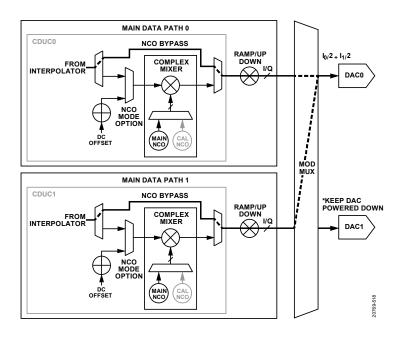

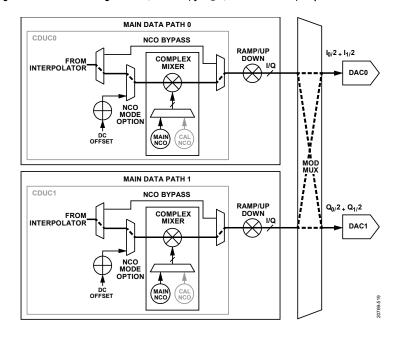

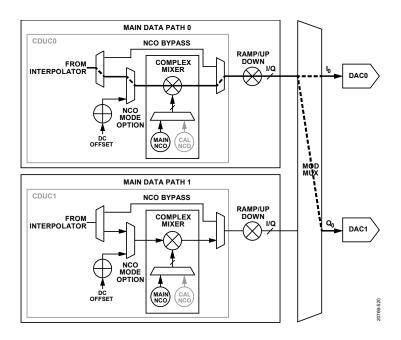

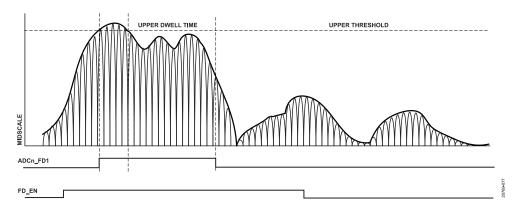

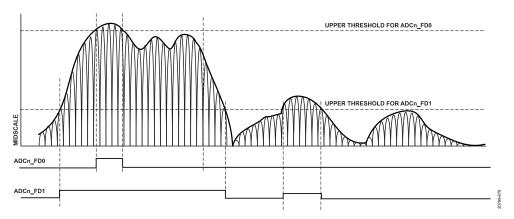

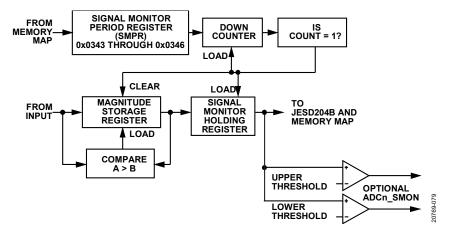

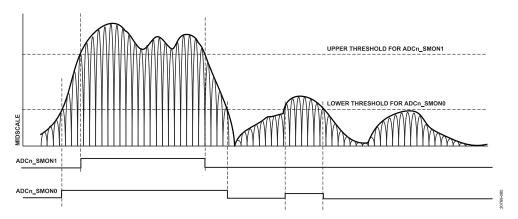

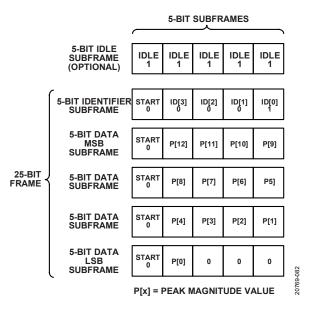

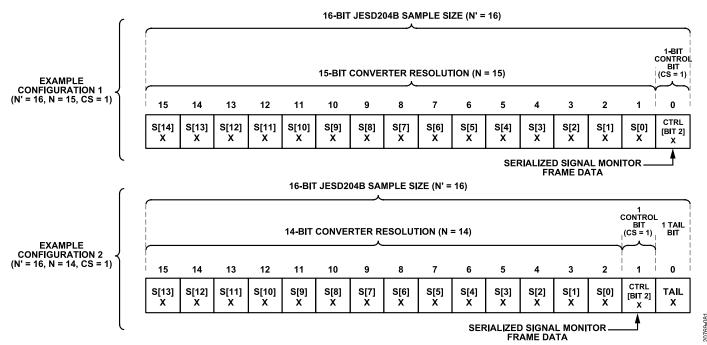

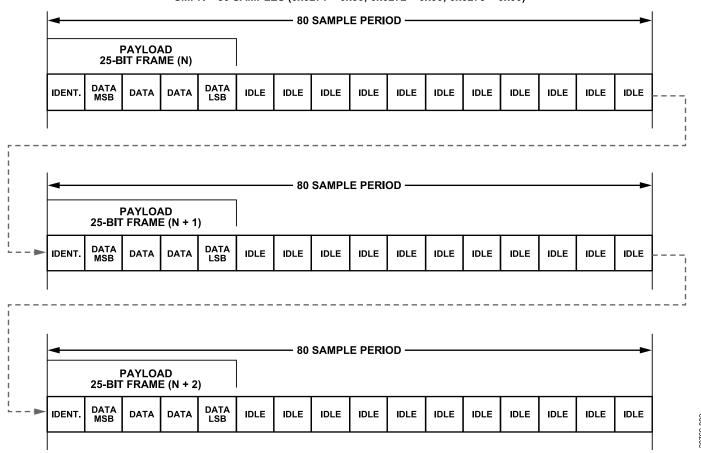

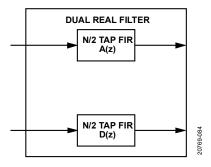

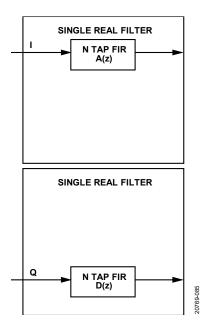

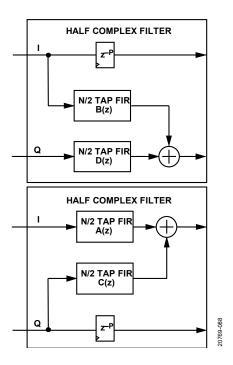

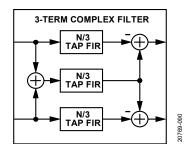

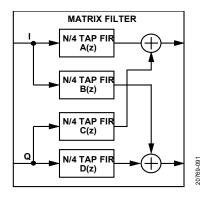

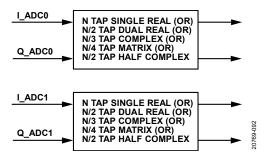

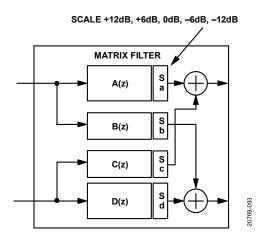

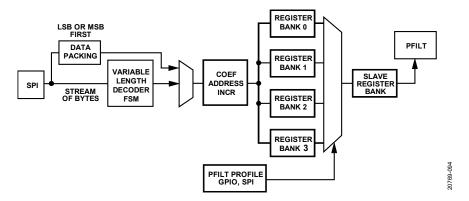

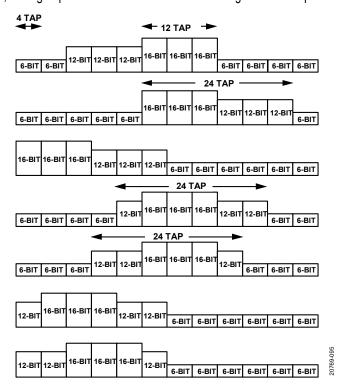

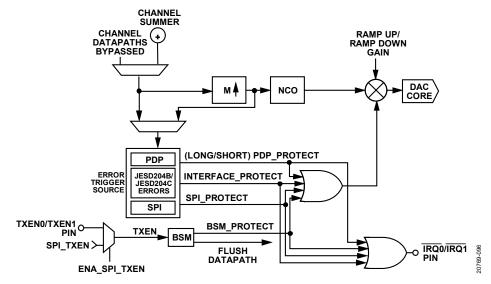

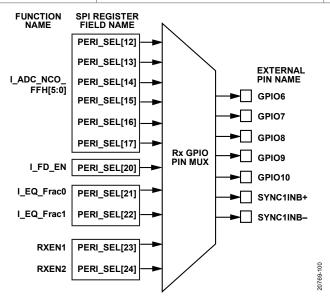

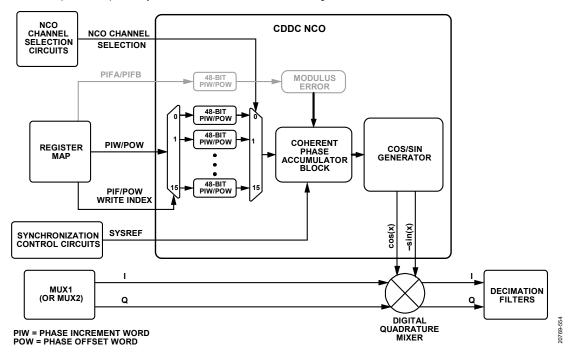

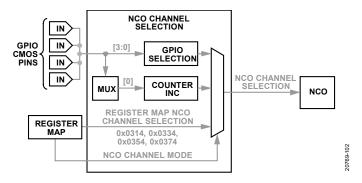

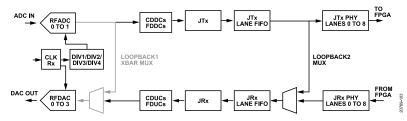

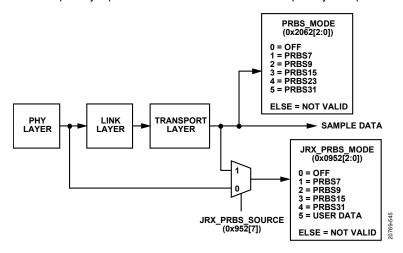

- ▶ JESD204B/C receiver and transmitter modes must be selected such that the corresponding lane rates remain equal or that the lane rate of the JESD204B/C transmitter is a power of 2 divisor of the lane rate of the JESD204B/C receiver. In the latter case, the bit repeat option of the JESD204B/C transmitter (JTX\_BR\_LOG2\_RATIO. Registers 0x0670 to Register 0x0677) must be enabled for every lane in use. (see the Configuring the JESD204B/C Transmitter Link section and JESD204B/C Transmitter Mode Tables section for details).