# ACT8934A

Rev 1, 22-Oct-12

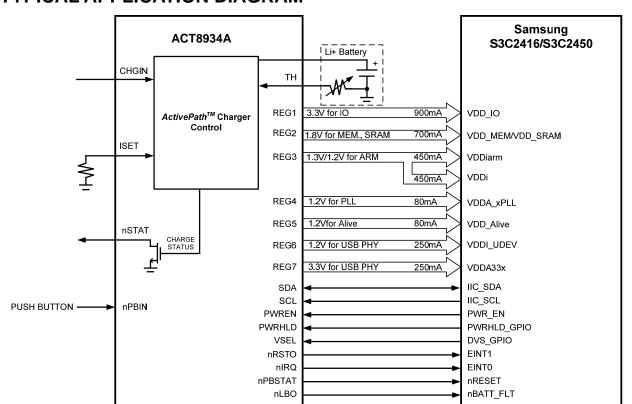

# Advanced PMU for Samsung S3C2416/S3C2450

# FEATURES

- Optimized for Samsung S3C2416/S3C2450

Processors

- Three Step-Down DC/DC Converters

- Four Low-Dropout Linear Regulators

- Integrated ActivePath<sup>™</sup> Charger

- I<sup>2</sup>C<sup>™</sup> Serial Interface

- Advanced Enable/Disable Sequencing Controller

- Minimal External Components

- Tiny 5×5mm TQFN55-40 Package

- 0.75mm Package Height

- Pb-Free and RoHS Compliant

# **GENERAL DESCRIPTION**

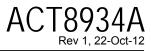

The ACT8934A is a complete, cost effective, highlyefficient *ActivePMU*<sup>TM</sup> power management solution, optimized for the unique power, voltagesequencing, and control requirements of the Samsung S3C2416/S3C2450 processors.

This device features three step-down DC/DC converters and four low-noise, low-dropout linear regulators, along with a complete battery charging solution featuring the advanced *ActivePath*<sup>TM</sup> system-power selection function.

The three DC/DC converters utilize a highefficiency, fixed-frequency (2MHz), current-mode PWM control architecture that requires a minimum number of external components. Two DC/DCs are capable of supplying up to 900mA of output current, while the third supports up to 700mA. All four lowdropout linear regulators are high-performance, low-noise regulators that supply up to 150mA, 150mA, 250mA, and 250mA, respectively.

The ACT8934A is available in a compact, Pb-Free and RoHS-compliant TQFN55-40 package.

# **TYPICAL APPLICATION DIAGRAM**

Innovative Power<sup>TM</sup> ActivePMU<sup>TM</sup> and ActivePath<sup>TM</sup> are trademarks of Active-Semi.  $I^2C^{TM}$  is a trademark of NXP.

TABLE OF CONTENTS

| General Information                                          | p. 0                                  | 1 |

|--------------------------------------------------------------|---------------------------------------|---|

| Functional Block Diagram                                     | p. 03                                 | 3 |

| Ordering Information                                         | p. 04                                 | 4 |

| Pin Configuration                                            |                                       | 4 |

| Pin Descriptions                                             | p. 0                                  | 5 |

| Absolute Maximum Ratings                                     | •                                     |   |

| I <sup>2</sup> C Interface Electrical Characteristics        |                                       |   |

| Global Register Map                                          |                                       |   |

| Register and Bit Descriptions                                |                                       |   |

| System Control Electrical Characteristics                    |                                       |   |

| Step-Down DC/DC Electrical Characteristics                   |                                       |   |

| Low-Noise LDO Electrical Characteristics                     |                                       |   |

| Active Path <sup>TM</sup> Charger Electrical Characteristics |                                       |   |

| Typical Performance Characteristics                          |                                       |   |

|                                                              | •                                     |   |

| System control information                                   |                                       |   |

| Interfacing with the Samsung S3C2416/S3C2450                 |                                       |   |

| Push-Button Control                                          |                                       |   |

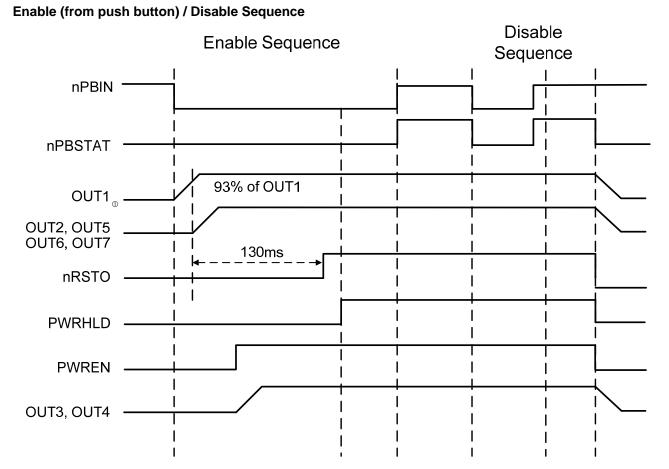

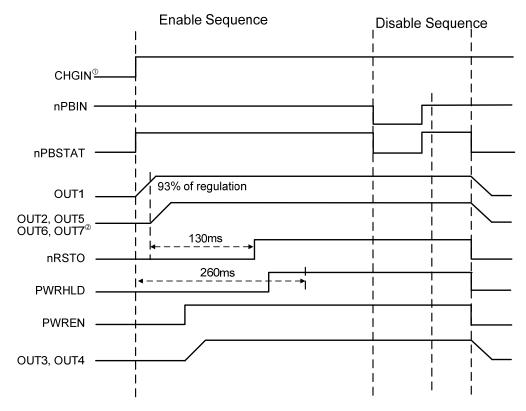

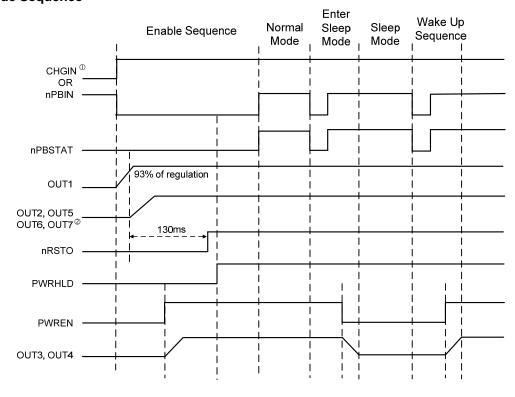

| Control Sequences.                                           | · · · · · · · · · · · · · · · · · · · |   |

|                                                              | · · · · · ·                           |   |

| Functional Description<br>I <sup>2</sup> C Interface         |                                       |   |

| Voltage Monitor and Interrupt                                |                                       |   |

| Thermal Shutdown                                             | n 3                                   | 3 |

|                                                              |                                       |   |

| Step-Down DC/DC Regulators<br>General Description            | •                                     |   |

| 100% Duty Cycle Operation                                    |                                       |   |

| Synchronous Rectification                                    |                                       |   |

| Soft-Start                                                   |                                       |   |

| Compensation                                                 |                                       |   |

| Configuration Options                                        |                                       |   |

| OK[] and Output Fault Interrupt                              |                                       |   |

| PCB Layout Considerations                                    | p. 3                                  | 5 |

| Low-Noise, Low-Dropout Linear Regulators                     | p. 3                                  | 6 |

| General Description                                          |                                       |   |

| Output Current Limit                                         |                                       |   |

| Compensation                                                 |                                       |   |

| Configuration Options                                        |                                       |   |

| OK[] and Output Fault Interrupt                              |                                       |   |

| PCB Layout Considerations                                    |                                       |   |

| ActivePath <sup>™</sup> Charger                              | p. 3                                  | 8 |

| General Description                                          |                                       |   |

| ActivePath Architecture                                      |                                       |   |

| System Configuration Optimization                            | •                                     |   |

| Input Protection                                             |                                       |   |

| Battery Management<br>Charge Current Programming             |                                       |   |

| Charger Input Interrupts                                     |                                       |   |

| Charge-Control State Machine                                 |                                       |   |

| State Machine Interrupts                                     |                                       |   |

| Thermal Regulation                                           |                                       |   |

| Charge Safety Timers                                         |                                       |   |

| Charger Timer Interrupts                                     |                                       |   |

| Charge Status Indicator                                      |                                       | 2 |

| Reverse-Current Protection                                   | •                                     |   |

| Battery Temperature Monitoring                               |                                       |   |

| Battery Temperature Interrupts                               |                                       |   |

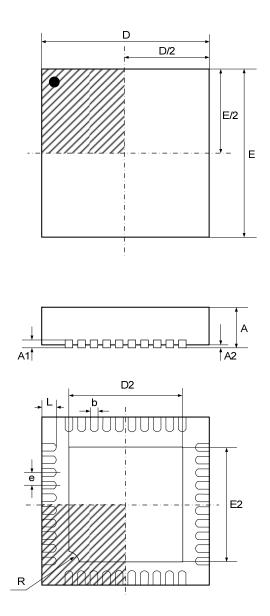

| TQFN55-40 Package Outline and Dimensions                     |                                       |   |

| Revision History                                             |                                       | 5 |

| Innovative Power <sup>™</sup> - 2 -                          | www.active-semi.com                   | m |

# FUNCTIONAL BLOCK DIAGRAM

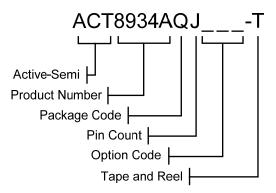

# **ORDERING INFORMATION**<sup>®®</sup>

| PART NUMBER®    | V <sub>OUT1</sub> /V <sub>STBY1</sub> ® | V <sub>out2</sub> /V <sub>stby2</sub> | V <sub>out3</sub> /V <sub>stby3</sub> | V <sub>OUT4</sub> | V <sub>OUT5</sub> | V <sub>OUT6</sub> | V <sub>out7</sub> | PACKAGE   | PINS | TEMPERATURE<br>RANGE |

|-----------------|-----------------------------------------|---------------------------------------|---------------------------------------|-------------------|-------------------|-------------------|-------------------|-----------|------|----------------------|

| ACT8934AQJ133-T | 3.3V/3.3V                               | 1.8V/1.8V                             | 1.3V/1.3V                             | 1.2V              | 1.2V              | 1.2V              | 3.3V              | TQFN55-40 | 40   | -40°C to +85°C       |

| ACT8934AQJ258-T | 3.3V/3.3V                               | 1.8V/1.8V                             | 1.25V/1.25V                           | 1.2V              | 1.2V              | 1.2V              | 3.3V              | TQFN55-40 | 40   | -40°C to +85°C       |

| ACT8934AQJ333-T | 3.3V/3.3V                               | 1.8V/1.8V                             | 1.3V/1.3V                             | 1.2V              | 1.2V              | 1.2V              | 3.3V              | TQFN55-40 | 40   | -40°C to +85°C       |

| ACT8934AQJ458-T | 3.3V/3.3V                               | 1.8V/1.8V                             | 1.25V/1.25V                           | 1.2V              | 1.2V              | 1.2V              | 3.3V              | TQFN55-40 | 40   | -40°C to +85°C       |

①: All Active-Semi components are RoHS Compliant and with Pb-free plating otherwise specified.

2: Standard product options are listed in this table. Contact factory for custom options. Minimum order quantity is 12,000 units.

3: Refer to Push-Button Control section for the power control sequences of each part number.

④: To select V<sub>STBYx</sub> as the output regulation voltage for REGx, drive VSEL to logic high. V<sub>STBYx</sub> can be set by software via I<sup>2</sup>C interface.

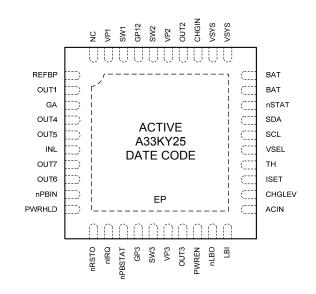

# **PIN CONFIGURATION**

TOP VIEW

#### Thin - QFN (TQFN55-40)

# **PIN DESCRIPTIONS**

| PIN | NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1   | REFBP   | Reference Bypass. Connect a $0.047\mu$ F ceramic capacitor from REFBP to GA. This pin is discharged to GA in shutdown.                                                                                                                                                                                      |  |  |  |  |  |

| 2   | OUT1    | Output Feedback Sense for REG1.                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 3   | GA      | Analog Ground. Connect GA directly to a quiet ground node. Connect GA, GP12 and GP3 together at a single point as close to the IC as possible.                                                                                                                                                              |  |  |  |  |  |

| 4   | OUT4    | REG4 output. Capable of delivering up to 150mA of output current. Connect a $1.5\mu$ F ceramic capacitor from OUT4 to GA. The output is discharged to GA with $1.5k\Omega$ resistor when disabled.                                                                                                          |  |  |  |  |  |

| 5   | OUT5    | REG5 output. Capable of delivering up to 150mA of output current. Connect a $1.5\mu$ F ceramic capacitor from OUT5 to GA. The output is discharged to GA with $1.5k\Omega$ resistor when disabled.                                                                                                          |  |  |  |  |  |

| 6   | INL     | Power Input for REG4, REG5, REG6, and REG7. Bypass to GA with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                                                                       |  |  |  |  |  |

| 7   | OUT7    | REG7 output. Capable of delivering up to 250mA of output current. Connect a 2.2 $\mu$ F ceramic capacitor from OUT7 to GA. The output is discharged to GA with 1.5 $k\Omega$ resistor when disabled.                                                                                                        |  |  |  |  |  |

| 8   | OUT6    | REG6 output. Capable of delivering up to 250mA of output current. Connect a 2.2 $\mu$ F ceramic capacitor from OUT6 to GA. The output is discharged to GA with 1.5 $k\Omega$ resistor when disabled.                                                                                                        |  |  |  |  |  |

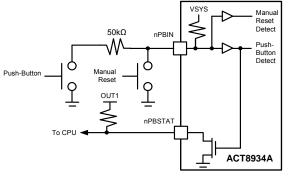

| 9   | nPBIN   | Master Enable Input. Drive nPBIN to GA through a 50k $\Omega$ resistor to enable the IC, drive nPBIN directly to GA to assert a manual reset condition. Refer to the <i>nPBIN Multi-function Input</i> section for more information. nPBIN is internally pulled up to VSYS through a 35k $\Omega$ resistor. |  |  |  |  |  |

| 10  | PWRHLD  | Power Hold Input. PWRHLD is internally pulled down to GA through a 500k $\Omega$ resistor. Refer to the <i>Control Sequences</i> section for more information.                                                                                                                                              |  |  |  |  |  |

| 11  | nRSTO   | Active Low Reset Output. See the <i>nRSTO Output</i> section for more information.                                                                                                                                                                                                                          |  |  |  |  |  |

| 12  | nIRQ    | Open-Drain Interrupt Output. nIRQ is asserted any time an unmasked fault condition exists or a charger interrupt occurs. See the <i>nIRQ Output</i> section for more information.                                                                                                                           |  |  |  |  |  |

| 13  | nPBSTAT | Active-Low Open-Drain Push-Button Status Output. nPBSTAT is asserted low whenever the nPBIN is pushed, and is high-Z otherwise. See the <i>nPBSTAT Output</i> section for more information.                                                                                                                 |  |  |  |  |  |

| 14  | GP3     | Power Ground for REG3. Connect GA, GP12, and GP3 together at a single point as close to the IC as possible.                                                                                                                                                                                                 |  |  |  |  |  |

| 15  | SW3     | Switching Node Output for REG3.                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 16  | VP3     | Power Input for REG3. Bypass to GP3 with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                                                                                            |  |  |  |  |  |

| 17  | OUT3    | Output Feedback Sense for REG3.                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 18  | PWREN   | Power Enable Input. Refer to the Control Sequences section for more information.                                                                                                                                                                                                                            |  |  |  |  |  |

| 19  | nLBO    | Low Battery Indicator Output. nLBO is asserted low whenever the voltage at LBI is lower than 1.2V, and is high-Z otherwise. See the <i>Precision Voltage Detector</i> section for more information.                                                                                                         |  |  |  |  |  |

| 20  | LBI     | Low Battery Input. The input voltage is compared to 1.2V and the output of this comparison drives nLBO. See the <i>Precision Voltage Detector</i> section for more information.                                                                                                                             |  |  |  |  |  |

| 21  | ACIN    | AC Input Supply Detection. See the Charge Current Programming section for more information.                                                                                                                                                                                                                 |  |  |  |  |  |

| 22  | CHGLEV  | Charge Current Selection Input. See the Charge Current Programming section for more information.                                                                                                                                                                                                            |  |  |  |  |  |

# PIN DESCRIPTIONS CONT'D

| PIN    | NAME  | DESCRIPTION                                                                                                                                                                                                                                   |

|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23     | ISET  | Charge Current Set. Program the charge current by connecting a resistor (R <sub>ISET</sub> ) between ISET and GA. See the <i>Charge Current Programming</i> section for more information.                                                     |

| 24     | ТН    | Temperature Sensing Input. Connect to battery thermistor. TH is pulled up with a 102µA (typ) current internally. See the <i>Battery Temperature Monitoring</i> section for more information.                                                  |

| 25     | VSEL  | Step-Down DC/DCs Output Voltage Selection. Drive to logic low to select default output voltage. Drive to logic high to select secondary output voltage. See the <i>Output Voltage Programming</i> section for more information.               |

| 26     | SCL   | Clock Input for I <sup>2</sup> C Serial Interface.                                                                                                                                                                                            |

| 27     | SDA   | Data Input for I <sup>2</sup> C Serial Interface. Data is read on the rising edge of SCL.                                                                                                                                                     |

| 28     | nSTAT | Active-Low Open-Drain Charger Status Output. nSTAT has a 8mA (typ) current limit, allowing it to directly drive an indicator LED without additional external components. See the <i>Charge Status Indicator</i> section for more information. |

| 29, 30 | BAT   | Battery Charger Output. Connect this pin directly to the battery anode (+ terminal)                                                                                                                                                           |

| 31, 32 | VSYS  | System Output Pin. Bypass to GA with a $10\mu F$ or larger ceramic capacitor.                                                                                                                                                                 |

| 33     | CHGIN | Power Input for the Battery Charger. Bypass CHGIN to GA with a capacitor placed as close to the IC as possible. The battery charger is automatically enabled when a valid voltage is present on CHGIN.                                        |

| 34     | OUT2  | Output Feedback Sense for REG2.                                                                                                                                                                                                               |

| 35     | VP2   | Power Input for REG2. Bypass to GP12 with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                             |

| 36     | SW2   | Switching Node Output for REG2.                                                                                                                                                                                                               |

| 37     | GP12  | Power Ground for REG1 and REG2. Connect GA, GP12 and GP3 together at a single point as close to the IC as possible.                                                                                                                           |

| 38     | SW1   | Switching Node Output for REG1.                                                                                                                                                                                                               |

| 39     | VP1   | Power Input for REG1. Bypass to GP12 with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                             |

| 40     | NC    | No Connect. Not internally connected.                                                                                                                                                                                                         |

| EP     | EP    | Exposed Pad. Must be soldered to ground on PCB.                                                                                                                                                                                               |

# **ABSOLUTE MAXIMUM RATINGS<sup>®</sup>**

| PARAMETER                                                                          | VALUE                            | UNIT |

|------------------------------------------------------------------------------------|----------------------------------|------|

| VP1, VP2 to GP12<br>VP3 to GP3                                                     | -0.3 to + 6                      | V    |

| BAT, VSYS, INL to GA                                                               | -0.3 to + 6                      | V    |

| CHGIN to GA                                                                        | -0.3 to + 14                     | V    |

| SW1, OUT1 to GP12                                                                  | -0.3 to (V <sub>VP1</sub> + 0.3) | V    |

| SW2, OUT2 to GP12                                                                  | -0.3 to (V <sub>VP2</sub> + 0.3) | V    |

| SW3, OUT3 to GP3                                                                   | -0.3 to (V <sub>VP3</sub> + 0.3) | V    |

| nIRQ, nLBO, nPBSTAT, nRSTO, nSTAT to GA                                            | -0.3 to + 6                      | V    |

| nPBIN, ACIN, CHGLEV, ISET, LBI, PWRHLD, PWREN, REFBP, SCL, SDA, TH, VSEL to GA     | -0.3 to (VSYS + 0.3)             | V    |

| OUT4, OUT5, OUT6, OUT7 to GA                                                       | -0.3 to (V <sub>INL</sub> + 0.3) | V    |

| GP12, GP3 to GA                                                                    | -0.3 to + 0.3                    | V    |

| Operating Ambient Temperature                                                      | -40 to 85                        | °C   |

| Maximum Junction Temperature                                                       | 125                              | °C   |

| Maximum Power Dissipation<br>TQFN55-40 (Thermal Resistance $\theta_{JA}$ = 30°C/W) | 2.7                              | W    |

| Storage Temperature                                                                | -65 to 150                       | °C   |

| Lead Temperature (Soldering, 10 sec)                                               | 300                              | °C   |

$\odot$ : Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

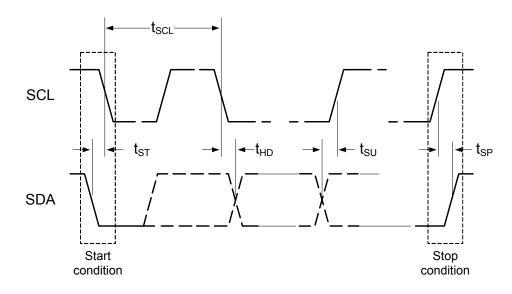

# I<sup>2</sup>C INTERFACE ELECTRICAL CHARACTERISTICS

(V\_{VSYS} = 3.6V, T\_A = 25°C, unless otherwise specified.)

| PARAMETER                            | TEST CONDITIONS                                  | MIN  | TYP | MAX  | UNIT |

|--------------------------------------|--------------------------------------------------|------|-----|------|------|

| SCL, SDA Input Low                   | $V_{VSYS}$ = 3.1V to 5.5V, $T_A$ = -40°C to 85°C |      |     | 0.35 | V    |

| SCL, SDA Input High                  | $V_{VSYS}$ = 3.1V to 5.5V, $T_A$ = -40°C to 85°C | 1.55 |     |      | V    |

| SDA Leakage Current                  |                                                  |      |     | 1    | μA   |

| SCL Leakage Current                  |                                                  |      |     | 2    | μA   |

| SDA Output Low                       | I <sub>OL</sub> = 5mA                            |      |     | 0.35 | V    |

| SCL Clock Period, t <sub>SCL</sub>   |                                                  | 1.5  |     |      | μs   |

| SDA Data Setup Time, t <sub>su</sub> |                                                  | 100  |     |      | ns   |

| SDA Data Hold Time, t <sub>HD</sub>  |                                                  | 300  |     |      | ns   |

| Start Setup Time, $t_{ST}$           | For Start Condition                              | 100  |     |      | ns   |

| Stop Setup Time, t <sub>SP</sub>     | For Stop Condition                               | 100  |     |      | ns   |

# Figure 1:

### I<sup>2</sup>C Compatible Serial Bus Timing

# **GLOBAL REGISTER MAP**

|                |                         |                      |          |          |            | Bľ         | rs         |            |           |           |

|----------------|-------------------------|----------------------|----------|----------|------------|------------|------------|------------|-----------|-----------|

| OUTPUT ADDRESS |                         |                      | D7       | D6       | D5         | D4         | D3         | D2         | D1        | D0        |

| SYS            | 0x00                    | NAME                 | TRST     | nSYSMODE | nSYSLEVMSK | nSYSSTAT   | SYSLEV[3]  | SYSLEV[2]  | SYSLEV[1] | SYSLEV[0] |

| 515            | 0000                    | DEFAULT®             | 0        | 1        | 0          | R          | 0          | 1          | 1         | 1         |

| eve            | 0.01                    | NAME                 | Reserved | Reserved | MSTROFF    | Reserved   | SCRATCH    | SCRATCH    | SCRATCH   | SCRATCH   |

| SYS            | 0x01                    | DEFAULT®             | 0        | 0        | 0          | 0          | 0          | 0          | 0         | 0         |

| REG1           | 0x20                    | NAME                 | Reserved | Reserved | VSET1[5]   | VSET1[4]   | VSET1[3]   | VSET1[2]   | VSET1[1]  | VSET1[0]  |

| REGI           | 0,20                    | DEFAULT <sup>®</sup> | 0        | 0        | 1          | 1          | 1          | 0          | 0         | 1         |

| REG1           | 0x21                    | NAME                 | Reserved | Reserved | VSET2[5]   | VSET2[4]   | VSET2[3]   | VSET2[2]   | VSET2[1]  | VSET2[0]  |

| REGI           | 0721                    | $DEFAULT^{\oplus}$   | 0        | 0        | 1          | 1          | 1          | 0          | 0         | 1         |

| REG1           | 0x22                    | NAME                 | ON       | PHASE    | MODE       | DELAY[2]   | DELAY[1]   | DELAY[0]   | nFLTMSK   | OK        |

| REGI           | 0x22                    | $DEFAULT^{\oplus}$   | 1        | 0        | 0          | 0          | 0          | 0          | 0         | R         |

| REG2           | 0x30                    | NAME                 | Reserved | Reserved | VSET1[5]   | VSET1[4]   | VSET1[3]   | VSET1[2]   | VSET1[1]  | VSET1[0]  |

| REGZ           | 0x30                    | $DEFAULT^{\oplus}$   | 0        | 0        | 1          | 0          | 0          | 1          | 0         | 0         |

| REG2           | 0x31                    | NAME                 | Reserved | Reserved | VSET2[5]   | VSET2[4]   | VSET2[3]   | VSET2[2]   | VSET2[1]  | VSET2[0]  |

| REGZ           | 0231                    | $DEFAULT^{\oplus}$   | 0        | 0        | 1          | 0          | 0          | 1          | 0         | 0         |

| REG2           | 0x32                    | NAME                 | ON       | PHASE    | MODE       | DELAY[2]   | DELAY[1]   | DELAY[0]   | nFLTMSK   | OK        |

| REGZ           | 0232                    | $DEFAULT^{\oplus}$   | 1        | 0        | 0          | 0          | 0          | 0          | 0         | R         |

| REG3           | 0x40                    | NAME                 | Reserved | Reserved | VSET1[5]   | VSET1[4]   | VSET1[3]   | VSET1[2]   | VSET1[1]  | VSET1[0]  |

| IXE 05         | 0,40                    | DEFAULT®             | 0        | 0        | 0          | 1          | 1          | 0          | 1         | 0         |

| REG3           | 0x41                    | NAME                 | Reserved | Reserved | VSET2[5]   | VSET2[4]   | VSET2[3]   | VSET2[2]   | VSET2[1]  | VSET2[0]  |

| IXE 05         | 0,41                    | $DEFAULT^{\oplus}$   | 0        | 0        | 0          | 1          | 1          | 0          | 1         | 0         |

| REG3           | 0x42                    | NAME                 | ON       | Reserved | MODE       | DELAY[2]   | DELAY[1]   | DELAY[0]   | nFLTMSK   | OK        |

| REG3           | 0,42                    | DEFAULT <sup>®</sup> | 0        | 0        | 0          | 0          | 0          | 0          | 0         | R         |

| REG4           | 0x50                    | NAME                 | Reserved | Reserved | VSET[5]    | VSET[4]    | VSET[3]    | VSET[2]    | VSET[1]   | VSET[0]   |

| NL04           | 0,00                    | DEFAULT®             | 0        | 0        | 0          | 1          | 1          | 0          | 0         | 0         |

| REG4           | 0x51                    | NAME                 | ON       | DIS      | LOWIQ      | DELAY[2]   | DELAY[1]   | DELAY[0]   | nFLTMSK   | OK        |

| NL04           | 0731                    | $DEFAULT^{\oplus}$   | 0        | 1        | 0          | 0          | 0          | 0          | 0         | R         |

| REG5           | 0x54                    | NAME                 | Reserved | Reserved | VSET[5]    | VSET[4]    | VSET[3]    | VSET[2]    | VSET[1]   | VSET[0]   |

| IXE05          | 0734                    | DEFAULT®             | 0        | 0        | 0          | 1          | 1          | 0          | 0         | 0         |

| REG5           | 0x55                    | NAME                 | ON       | DIS      | LOWIQ      | DELAY[2]   | DELAY[1]   | DELAY[0]   | nFLTMSK   | OK        |

| IXE 05         | 0,00                    | $DEFAULT^{\oplus}$   | 1        | 1        | 0          | 0          | 0          | 0          | 0         | R         |

| REG6           | 0x60                    | NAME                 | Reserved | Reserved | VSET[5]    | VSET[4]    | VSET[3]    | VSET[2]    | VSET[1]   | VSET[0]   |

| IXLO0          | 0,00                    | DEFAULT <sup>®</sup> | 0        | 0        | 0          | 1          | 1          | 0          | 0         | 0         |

| REG6           | 0x61                    | NAME                 | ON       | DIS      | LOWIQ      | DELAY[2]   | DELAY[1]   | DELAY[0]   | nFLTMSK   | OK        |

| NL00           | 0,01                    | DEFAULT®             | 0        | 1        | 0          | 0          | 0          | 0          | 0         | R         |

| REG7           | 0x64                    | NAME                 | Reserved | Reserved | VSET[5]    | VSET[4]    | VSET[3]    | VSET[2]    | VSET[1]   | VSET[0]   |

| NLO7           | 0704                    | $DEFAULT^{\oplus}$   | 0        | 0        | 1          | 1          | 1          | 0          | 0         | 1         |

| REG7           | 0x65                    | NAME                 | ON       | DIS      | LOWIQ      | DELAY[2]   | DELAY[1]   | DELAY[0]   | nFLTMSK   | OK        |

| INEO/          | 0,00                    | DEFAULT®             | 0        | 1        | 0          | 0          | 0          | 0          | 0         | R         |

| APCH           | 0x70                    | NAME                 | Reserved | Reserved | Reserved   | Reserved   | Reserved   | Reserved   | Reserved  | Reserved  |

|                | 0,110                   | DEFAULT®             | 0        | 1        | 0          | 1          | 0          | 0          | 0         | 0         |

| APCH           | 0x71                    | NAME                 | SUSCHG   | Reserved | TOTTIMO[1] | TOTTIMO[0] | PRETIMO[1] | PRETIMO[0] | OVPSET[1] | OVPSET[0] |

| / 011          |                         | DEFAULT              | 0        | 0        | 1          | 0          | 1          | 0          | 0         | 0         |

| APCH           | 0x78                    | NAME                 | TIMRSTAT | TEMPSTAT | INSTAT     | CHGSTAT    | TIMRDAT    | TEMPDAT    | INDAT     | CHGDAT    |

|                | 5410                    | DEFAULT®             | 0        | 0        | 0          | 0          | R          | R          | R         | R         |

| APCH           | 0x79                    | NAME                 | TIMRTOT  | TEMPIN   | INCON      | CHGEOCIN   | TIMRPRE    | TEMPOUT    | INDIS     | CHGEOCOUT |

| / ОП           | UNI U                   | DEFAULT®             | 0        | 0        | 0          | 0          | 0          | 0          | 0         | 0         |

| APCH           | 0x7A                    | NAME                 | Reserved | Reserved | CSTATE[0]  | CSTATE[1]  | Reserved   | Reserved   | ACINSTAT  | Reserved  |

|                | <i>S</i> , <i>i i i</i> | $DEFAULT^{\oplus}$   | 0        | 0        | R          | R          | R          | R          | R         | R         |

1): Default values of ACT8934AQJ133-T.

2: All bits are automatically cleared to default values when the input power is removed or falls below the system UVLO.

# **REGISTER AND BIT DESCRIPTIONS**

Table 1:

#### Global Register Map

| OUTPUT | ADDRESS | BIT   | NAME       | ACCESS | DESCRIPTION                                                                                                                                                                                                                                 |

|--------|---------|-------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS    | 0x00    | [7]   | TRST       | R/W    | Reset Timer Setting. Defines the reset time-out threshold. Reset time-out is 65ms when value is 1, reset time-out is 130ms when value is 0. See <i>nRSTO Output</i> section for more information.                                           |

| SYS    | 0x00    | [6]   | nSYSMODE   | R/W    | SYSLEV Mode Select. Defines the response to the SYSLEV voltage detector, 1: Generate an interrupt when VSYS falls below the programmed SYSLEV threshold, 0: automatic shutdown when $V_{VSYS}$ falls below the programmed SYSLEV threshold. |

| SYS    | 0x00    | [5]   | nSYSLEVMSK | R/W    | System Voltage Level Interrupt Mask. SYSLEV interrupt is masked by default, set to 1 to unmask this interrupt. See the <i>Programmable System Voltage Monitor</i> section for more information                                              |

| SYS    | 0x00    | [4]   | nSYSSTAT   | R      | System Voltage Status. Value is 1 when $V_{VSYS}$ is lower than the SYSLEV voltage threshold, value is 0 when $V_{VSYS}$ is higher than the system voltage detection threshold.                                                             |

| SYS    | 0x00    | [3:0] | SYSLEV     | R/W    | System Voltage Detect Threshold. Defines the SYSLEV voltage threshold. See the <i>Programmable System Voltage Monitor</i> section for more information.                                                                                     |

| SYS    | 0x01    | [7:6] | -          | R/W    | Reserved.                                                                                                                                                                                                                                   |

| SYS    | 0x01    | [5]   | MSTROFF    | R/W    | Master Off Control. Set bit to 1 to turn off REG1, REG2 and REG5. The bit will be automatically cleared to 0 when nPBIN is asserted or a valid CHGIN voltage is detected (for ACT8934AQJ2XX only).                                          |

| SYS    | 0x01    | [4]   | -          | R/W    | Reserved.                                                                                                                                                                                                                                   |

| SYS    | 0x01    | [3:0] | SCRATCH    | R/W    | Scratchpad Bits. Non-functional bits, maybe be used by user to store system status information. Volatile bits, which are cleared when system voltage falls below UVLO threshold.                                                            |

| REG1   | 0x20    | [7:6] | -          | R      | Reserved.                                                                                                                                                                                                                                   |

| REG1   | 0x20    | [5:0] | VSET1      | R/W    | Primary Output Voltage Selection. Valid when VSEL is driven low. See the <i>Output Voltage Programming</i> section for more information.                                                                                                    |

| REG1   | 0x21    | [7:6] | -          | R      | Reserved.                                                                                                                                                                                                                                   |

| REG1   | 0x21    | [5:0] | VSET2      | R/W    | Secondary Output Voltage Selection. Valid when VSEL is driven high. See the <i>Output Voltage Programming</i> section for more information.                                                                                                 |

| REG1   | 0x22    | [7]   | ON         | R/W    | Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit to 0 to disable the regulator.                                                                                                                                        |

| REG1   | 0x22    | [6]   | PHASE      | R/W    | Regulator Phase Control. Set bit to 1 for the regulator to operate 180° out of phase with the oscillator, clear bit to 0 for the regulator to operate in phase with the oscillator.                                                         |

| REG1   | 0x22    | [5]   | MODE       | R/W    | Regulator Mode Select. Set bit to 1 for fixed-frequency PWM under all load conditions, clear bit to 0 to transit to power-savings mode under light-load conditions.                                                                         |

| REG1   | 0x22    | [4:2] | DELAY      | R/W    | Regulator Turn-On Delay Control. See the REG1, REG2, REG3<br>Turn-on Delay section for more information.                                                                                                                                    |

| REG1   | 0x22    | [1]   | nFLTMSK    | R/W    | Regulator Fault Mask Control. Set bit to 1 enable fault-interrupts, clear bit to 0 to disable fault-interrupts.                                                                                                                             |

| REG1   | 0x22    | [0]   | ОК         | R      | Regulator Power-OK Status. Value is 1 when output voltage exceeds the power-OK threshold, value is 0 otherwise.                                                                                                                             |

| REG2   | 0x30    | [7:6] | -          | R      | Reserved.                                                                                                                                                                                                                                   |

| REG2   | 0x30    | [5:0] | VSET1      | R/W    | Primary Output Voltage Selection. Valid when VSEL is driven low.<br>See the <i>Output Voltage Programming</i> section for more information.                                                                                                 |

| REG2   | 0x31    | [7:6] | -          | R      | Reserved.                                                                                                                                                                                                                                   |

| OUTPUT | ADDRESS | BIT   | NAME    | ACCESS | DESCRIPTION                                                                                                                                                                                                                    |

|--------|---------|-------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REG2   | 0x31    | [5:0] | VSET2   | R/W    | Secondary Output Voltage Selection. Valid when VSEL is driven high. See the <i>Output Voltage Programming</i> section for more information.                                                                                    |

| REG2   | 0x32    | [7]   | ON      | R/W    | Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit to 0 to disable the regulator.                                                                                                                           |

| REG2   | 0x32    | [6]   | PHASE   | R/W    | Regulator Phase Control. Set bit to 1 for the regulator to operate 180° out of phase with the oscillator, clear bit to 0 for the regulator to operate in phase with the oscillator.                                            |

| REG2   | 0x32    | [5]   | MODE    | R/W    | Regulator Mode Select. Set bit to 1 for fixed-frequency PWM under all load conditions, clear bit to 0 to transit to power-savings mode under light-load conditions.                                                            |

| REG2   | 0x32    | [4:2] | DELAY   | R/W    | Regulator Turn-On Delay Control. See the <i>REG1, REG2, REG3 Turn-on Delay</i> section for more information.                                                                                                                   |

| REG2   | 0x32    | [1]   | nFLTMSK | R/W    | Regulator Fault Mask Control. Set bit to 1 enable fault-<br>interrupts, clear bit to 0 to disable fault-interrupts.                                                                                                            |

| REG2   | 0x32    | [0]   | ОК      | R      | Regulator Power-OK Status. Value is 1 when output voltage exceeds the power-OK threshold, value is 0 otherwise.                                                                                                                |

| REG3   | 0x40    | [7:6] | -       | R      | Reserved.                                                                                                                                                                                                                      |

| REG3   | 0x40    | [5:0] | VSET1   | R/W    | Primary Output Voltage Selection. Valid when VSEL is driven low. See the <i>Output Voltage Programming</i> section for more information.                                                                                       |

| REG3   | 0x41    | [7:6] | -       | R      | Reserved.                                                                                                                                                                                                                      |

| REG3   | 0x41    | [5:0] | VSET2   | R/W    | Secondary Output Voltage Selection. Valid when VSEL is driven high. See the <i>Output Voltage Programming</i> section for more information.                                                                                    |

| REG3   | 0x42    | [7]   | ON      | R/W    | Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit to 0 to disable the regulator.                                                                                                                           |

| REG3   | 0x42    | [6]   | -       | R/W    | Reserved.                                                                                                                                                                                                                      |

| REG3   | 0x42    | [5]   | MODE    | R/W    | Regulator Mode Select. Set bit to 1 for fixed-frequency PWM under all load conditions, clear bit to 0 to transit to power-savings mode under light-load conditions.                                                            |

| REG3   | 0x42    | [4:2] | DELAY   | R/W    | Regulator Turn-On Delay Control. See the <i>REG1, REG2, REG3 Turn-on Delay</i> section for more information.                                                                                                                   |

| REG3   | 0x42    | [1]   | nFLTMSK | R/W    | Regulator Fault Mask Control. Set bit to 1 enable fault-<br>interrupts, clear bit to 0 to disable fault-interrupts.                                                                                                            |

| REG3   | 0x42    | [0]   | OK      | R      | Regulator Power-OK Status. Value is 1 when output voltage exceeds the power-OK threshold, value is 0 otherwise.                                                                                                                |

| REG4   | 0x50    | [7:6] | -       | R      | Reserved.                                                                                                                                                                                                                      |

| REG4   | 0x50    | [5:0] | VSET    | R/W    | Output Voltage Selection. See the <i>Output Voltage</i><br><i>Programming</i> section for more information.                                                                                                                    |

| REG4   | 0x51    | [7]   | ON      | R/W    | Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit to 0 to disable the regulator.                                                                                                                           |

| REG4   | 0x51    | [6]   | DIS     | R/W    | Output Discharge Control. When activated, LDO output is discharged to GA through $1.5k\Omega$ resistor when in shutdown. Set bit to 1 to enable output voltage discharge in shutdown, clear bit to 0 to disable this function. |

| REG4   | 0x51    | [5]   | LOWIQ   | R/W    | LDO Low-IQ Mode Control. Set bit to 1 for low-power operating mode, clear bit to 0 for normal mode.                                                                                                                            |

| REG4   | 0x51    | [4:2] | DELAY   | R/W    | Regulator Turn-On Delay Control. See the <i>REG4, REG5, REG6, REG7 Turn-on Delay</i> section for more information.                                                                                                             |

| REG4   | 0x51    | [1]   | nFLTMSK | R/W    | Regulator Fault Mask Control. Set bit to 1 enable fault-<br>interrupts, clear bit to 0 to disable fault-interrupts.                                                                                                            |

| OUTPUT       | ADDRESS      | BIT   | NAME    | ACCESS | DESCRIPTION                                                                                                                                                                                                                    |

|--------------|--------------|-------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |              |       |         |        | Regulator Power-OK Status. Value is 1 when output voltage                                                                                                                                                                      |

| REG4<br>REG5 | 0x51<br>0x54 | [0]   | ОК      | R<br>R | exceeds the power-OK threshold, value is 0 otherwise.                                                                                                                                                                          |

| REGO         | 0X04         | [7:6] | -       | ĸ      | Output Voltage Selection. See the <i>Output Voltage</i>                                                                                                                                                                        |

| REG5         | 0x54         | [5:0] | VSET    | R/W    | Programming section for more information.                                                                                                                                                                                      |

| REG5         | 0x55         | [7]   | ON      | R/W    | Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit to 0 to disable the regulator.                                                                                                                           |

| REG5         | 0x55         | [6]   | DIS     | R/W    | Output Discharge Control. When activated, LDO output is discharged to GA through $1.5k\Omega$ resistor when in shutdown. Set bit to 1 to enable output voltage discharge in shutdown, clear bit to 0 to disable this function. |

| REG5         | 0x55         | [5]   | LOWIQ   | R/W    | LDO Low-IQ Mode Control. Set bit to 1 for low-power operating mode, clear bit to 0 for normal mode.                                                                                                                            |

| REG5         | 0x55         | [4:2] | DELAY   | R/W    | Regulator Turn-On Delay Control. See the REG4, REG5, REG6, REG7 Turn-on Delay section for more information.                                                                                                                    |

| REG5         | 0x55         | [1]   | nFLTMSK | R/W    | Regulator Fault Mask Control. Set bit to 1 enable fault-<br>interrupts, clear bit to 0 to disable fault-interrupts.                                                                                                            |

| REG5         | 0x55         | [0]   | ОК      | R      | Regulator Power-OK Status. Value is 1 when output voltage exceeds the power-OK threshold, value is 0 otherwise.                                                                                                                |

| REG6         | 0x60         | [7:6] | -       | R      | Reserved.                                                                                                                                                                                                                      |

| REG6         | 0x60         | [5:0] | VSET    | R/W    | Output Voltage Selection. See the <i>Output Voltage</i><br><i>Programming</i> section for more information.                                                                                                                    |

| REG6         | 0x61         | [7]   | ON      | R/W    | Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit to 0 to disable the regulator.                                                                                                                           |

| REG6         | 0x61         | [6]   | DIS     | R/W    | Output Discharge Control. When activated, LDO output is discharged to GA through $1.5k\Omega$ resistor when in shutdown. Set bit to 1 to enable output voltage discharge in shutdown, clear bit to 0 to disable this function. |

| REG6         | 0x61         | [5]   | LOWIQ   | R/W    | LDO Low-IQ Mode Control. Set bit to 1 for low-power operating mode, clear bit to 0 for normal mode.                                                                                                                            |

| REG6         | 0x61         | [4:2] | DELAY   | R/W    | Regulator Turn-On Delay Control. See the <i>REG4, REG5, REG6, REG7 Turn-on Delay</i> section for more information.                                                                                                             |

| REG6         | 0x61         | [1]   | nFLTMSK | R/W    | Regulator Fault Mask Control. Set bit to 1 enable fault-<br>interrupts, clear bit to 0 to disable fault-interrupts.                                                                                                            |

| REG6         | 0x61         | [0]   | ОК      | R      | Regulator Power-OK Status. Value is 1 when output voltage exceeds the power-OK threshold, value is 0 otherwise.                                                                                                                |

| REG7         | 0x64         | [7:6] | -       | R      | Reserved.                                                                                                                                                                                                                      |

| REG7         | 0x64         | [5:0] | VSET    | R/W    | Output Voltage Selection. See the <i>Output Voltage</i><br><i>Programming</i> section for more information.                                                                                                                    |

| REG7         | 0x65         | [7]   | ON      | R/W    | Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit to 0 to disable the regulator.                                                                                                                           |

| REG7         | 0x65         | [6]   | DIS     | R/W    | Output Discharge Control. When activated, LDO output is discharged to GA through $1.5k\Omega$ resistor when in shutdown. Set bit to 1 to enable output voltage discharge in shutdown, clear bit to 0 to disable this function. |

| REG7         | 0x65         | [5]   | LOWIQ   | R/W    | LDO Low-IQ Mode Control. Set bit to 1 for low-power operating mode, clear bit to 0 for normal mode.                                                                                                                            |

| REG7         | 0x65         | [4:2] | DELAY   | R/W    | Regulator Turn-On Delay Control. See the REG4, REG5, REG6, REG7 Turn-on Delay section for more information.                                                                                                                    |

| REG7         | 0x65         | [1]   | nFLTMSK | R/W    | Regulator Fault Mask Control. Set bit to 1 enable fault-<br>interrupts, clear bit to 0 to disable fault-interrupts.                                                                                                            |

| REG7         | 0x65         | [0]   | ОК      | R      | Regulator Power-OK Status. Value is 1 when output voltage exceeds the power-OK threshold, value is 0 otherwise.                                                                                                                |

| OUTPUT | ADDRESS | BIT   | NAME      | ACCESS | DESCRIPTION                                                                                                                                                                                                                                                                                                 |

|--------|---------|-------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APCH   | 0x70    | [7:0] | -         | R      | Reserved.                                                                                                                                                                                                                                                                                                   |

| APCH   | 0x71    | [7]   | SUSCHG    | R/W    | Charge Suspend Control Input. Set bit to 1 to suspend charging, clear bit to 0 to allow charging to resume.                                                                                                                                                                                                 |

| APCH   | 0x71    | [6]   | -         | R/W    | Reserved.                                                                                                                                                                                                                                                                                                   |

| APCH   | 0x71    | [5:4] | ΤΟΤΤΙΜΟ   | R/W    | Total Charge Time-out Selection. See the <i>Charge Safety Timers</i> section for more information.                                                                                                                                                                                                          |

| APCH   | 0x71    | [3:2] | PRETIMO   | R/W    | Precondition Charge Time-out Selection. See the <i>Charge Safety Timers</i> section for more information.                                                                                                                                                                                                   |

| APCH   | 0x71    | [1:0] | OVPSET    | R/W    | Input Over-Voltage Protection Threshold Selection. See the<br>Input Over-Voltage Protection section for more information.                                                                                                                                                                                   |

| APCH   | 0x78    | [7]   | TIMRSTAT® | R/W    | Charge Time-out Interrupt Status. Set this bit with<br>TIMRPRE[] and/or TIMRTOT[] to 1 to generate an interrupt<br>when charge safety timers expire, read this bit to get charge<br>time-out interrupt status. See the <i>Charge Safety Timers</i><br>section for more information.                         |

| APCH   | 0x78    | [6]   | TEMPSTAT® | R/W    | Battery Temperature Interrupt Status. Set this bit with TEMPIN[] and/or TEMPOUT[] to 1 to generate an interrupt when a battery temperature event occurs, read this bit to get the battery temperature interrupt status. See the <i>Battery Temperature Monitoring</i> section for more information.         |

| APCH   | 0x78    | [5]   | INSTAT    | R/W    | Input Voltage Interrupt Status. Set this bit with INCON[] and/<br>or INDIS[] to generate an interrupt when UVLO or OVP<br>condition occurs, read this bit to get the input voltage<br>interrupt status. See the <i>Charge Current Programming</i><br>section for more information.                          |

| APCH   | 0x78    | [4]   | CHGSTAT®  | R/W    | Charge State Interrupt Status. Set this bit with<br>CHGEOCIN[] and/or CHGEOCOUT[] to 1 to generate an<br>interrupt when the state machine gets in or out of EOC state,<br>read this bit to get the charger state interrupt status. See the<br><i>State Machine Interrupts</i> section for more information. |

| APCH   | 0x78    | [3]   |           | R      | Charge Timer Status. Value is 1 when precondition time-out or total charge time-out occurs. Value is 0 in other case.                                                                                                                                                                                       |

| APCH   | 0x78    | [2]   | TEMPDAT®  | R      | Temperature Status. Value is 0 when battery temperature is outside of valid range. Value is 1 when battery temperature is inside of valid range.                                                                                                                                                            |

| APCH   | 0x78    | [1]   | INDAT     | R      | Input Voltage Status. Value is 1 when a valid input at CHGIN is present. Value is 0 when a valid input at CHGIN is not present.                                                                                                                                                                             |

| APCH   | 0x78    | [0]   | CHGDAT®   | R      | Charge State Machine Status. Value is 1 indicates the charger state machine is in EOC state, value is 0 indicates the charger state machine is in other states.                                                                                                                                             |

| APCH   | 0x79    | [7]   | TIMRTOT   | R/W    | Total Charge Time-out Interrupt control. Set both this bit and TIMRSTAT[] to 1 to generate an interrupt when a total charge time-out occurs. See the <i>Charge Safety Timers</i> section for more information.                                                                                              |

| APCH   | 0x79    | [6]   | TEMPIN    | R/W    | Battery Temperature Interrupt Control. Set both this bit and TEMPSTAT[] to 1 to generate an interrupt when the battery temperature goes into the valid range. See the <i>Battery Temperature Monitoring</i> section for more information.                                                                   |

| APCH   | 0x79    | [5]   | INCON     | R/W    | Input Voltage Interrupt Control. Set both this bit and<br>INSTAT[] to 1 to generate an interrupt when CHGIN input<br>voltage goes into the valid range. See the <i>Charge Current</i><br><i>Programming</i> section for more information.                                                                   |

0: Valid only when CHGIN UVLO Threshold<br/><br/>V\_{CHGIN}<br/>CHGIN OVP Threshold.

| OUTPUT | ADDRESS | BIT   | NAME      | ACCESS | DESCRIPTION                                                                                                                                                                                                                                 |

|--------|---------|-------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APCH   | 0x79    | [4]   | CHGEOCIN  | R/W    | Charge State Interrupt Control. Set both this bit and CHGSTAT[] to 1 to generate an interrupt when the state machine goes into the EOC state. See the <i>State Machine Interrupts</i> section for more information.                         |

| APCH   | 0x79    | [3]   | TIMRPRE   | R/W    | PRECHARGE Time-out Interrupt control. Set both this bit<br>and TIMRSTAT[] to 1 to generate an interrupt when a<br>PRECHARGE time-out occurs. See the <i>Charge Safety</i><br><i>Timers</i> section for more information.                    |

| APCH   | 0x79    | [2]   | TEMPOUT   | R/W    | Battery Temperature Interrupt Control. Set both this bit and TEMPSTAT[] to 1 to generate an interrupt when the battery temperature goes out of the valid range. See the <i>Battery Temperature Monitoring</i> section for more information. |

| APCH   | 0x79    | [1]   | INDIS     | R/W    | Input Voltage Interrupt Control. Set both this bit and<br>INSTAT[] to 1 to generate an interrupt when CHGIN input<br>voltage goes out of the valid range. See the <i>Charge Current</i><br><i>Programming</i> section for more information. |

| APCH   | 0x79    | [0]   | CHGEOCOUT | R/W    | Charge State Interrupt Control. Set both this bit and CHGSTAT[] to 1 to generate an interrupt when the state machines jumps out of the EOC state. See the <i>State Machine Interrupts</i> section for more information.                     |

| APCH   | 0x7A    | [7:6] | -         | R      | Reserved.                                                                                                                                                                                                                                   |

| APCH   | 0x7A    | [5:4] | CSTATE    | R      | Charge State. Values indicate the current charging state.<br>See the State Machine Interrupts section for more<br>information.                                                                                                              |

| APCH   | 0x7A    | [3:2] | -         | R      | Reserved.                                                                                                                                                                                                                                   |

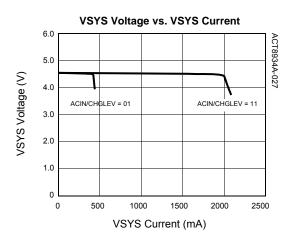

| APCH   | 0x7A    | [1]   | ACINSTAT  | R      | ACIN Status. Indicates the state of the ACIN input, typically<br>in order to identify the type of input supply connected. Value<br>is 1 when ACIN is above the 1.2V precision threshold, value<br>is 0 when ACIN is below this threshold.   |

| APCH   | 0x7A    | [0]   | -         | R      | Reserved.                                                                                                                                                                                                                                   |

# SYSTEM CONTROL ELECTRICAL CHARACTERISTICS

( $V_{VSYS}$  = 3.6V,  $T_A$  = 25°C, unless otherwise specified.)

| PARAMETER                             | TEST CONDITIONS                                                    | MIN  | TYP              | MAX  | UNIT |

|---------------------------------------|--------------------------------------------------------------------|------|------------------|------|------|

| Input Voltage Range                   |                                                                    | 2.7  |                  | 5.5  | V    |

| UVLO Threshold Voltage                | V <sub>VSYS</sub> Rising                                           | 2.2  | 2.45             | 2.65 | V    |

| UVLO Hysteresis                       | V <sub>VSYS</sub> Falling                                          |      | 200              |      | mV   |

|                                       | REG1, REG2 and REG5 Enabled. REG3, REG4, REG6 and REG7 Disabled    |      | 250              |      |      |

| Supply Current                        | REG1, REG2, REG3, REG4 and REG5<br>Enabled. REG6 and REG7 Disabled |      | 350              |      | μA   |

|                                       | REG1, REG2, REG3, REG4,REG5, REG6, REG7 Enabled                    |      | 420              |      |      |

| Shutdown Supply Current               | All Regulators Disabled                                            |      | 8                | 18   | μA   |

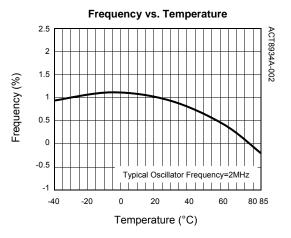

| Oscillator Frequency                  |                                                                    | 1.8  | 2                | 2.2  | MHz  |

| Logic High Input Voltage <sup>®</sup> |                                                                    | 1.4  |                  |      | V    |

| Logic Low Input Voltage               |                                                                    |      |                  | 0.4  | V    |

| Leakage Current                       | $V_{nIRQ} = V_{nRSTO} = 4.2V$                                      |      |                  | 1    | μA   |

| LBI Threshold Voltage                 | V <sub>BAT</sub> Falling                                           | 1.03 | 1.2              | 1.31 | V    |

| LBI Hysteresis Threshold              | V <sub>BAT</sub> Rising                                            |      | 200              |      | mV   |

| Low Level Output Voltage <sup>©</sup> | I <sub>SINK</sub> = 5mA                                            |      |                  | 0.35 | V    |

| nRSTO Delay                           |                                                                    |      | 130 <sup>®</sup> |      | ms   |

| PWRHLD Pull Down Resistor             |                                                                    |      | 500              |      | kΩ   |

| Thermal Shutdown Temperature          | Temperature rising                                                 |      | 160              |      | °C   |

| Thermal Shutdown Hysteresis           |                                                                    |      | 20               |      | °C   |

①: PWRHLD, PWREN, VSEL are logic inputs.

②: nLBO, nPBSTAT, nIRQ, nRSTO are open drain outputs.

③: Typical value shown. Actual value may vary from (T-1ms) x 88% to T x 112%, where T = 130ms.

# STEP-DOWN DC/DC ELECTRICAL CHARACTERISTICS

( $V_{VP1}$  =  $V_{VP2}$  =  $V_{VP3}$  = 3.6V,  $T_A$  = 25°C, unless otherwise specified.)

| PARAMETER                | CONDITIONS                                            | MIN | ТҮР                           | MAX | UNIT              |

|--------------------------|-------------------------------------------------------|-----|-------------------------------|-----|-------------------|

| Operating Voltage Range  |                                                       | 2.7 |                               | 5.5 | V                 |

| UVLO Threshold           | Input Voltage Rising                                  | 2.5 | 2.6                           | 2.7 | V                 |

| UVLO Hysteresis          | Input Voltage Falling                                 |     | 100                           |     | mV                |

| Quiescent Supply Current | Regulator Enabled                                     |     | 65                            | 90  | μA                |

| Shutdown Current         | $V_{VP}$ = 5.5V, Regulator Disabled                   |     | 0                             | 1   | μA                |

|                          | V <sub>OUT</sub> ≥ 1.2V, I <sub>OUT</sub> = 10mA      | -1% | $V_{\text{NOM}}^{\mathbb{O}}$ | 1%  |                   |

| Output Voltage Accuracy  | V <sub>OUT</sub> < 1.2V, I <sub>OUT</sub> = 10mA      | -2% | $V_{\text{NOM}}^{\mathbb{O}}$ | 2%  | V                 |

| Line Regulation          | $V_{VP} = Max(V_{NOM}^{\circ} + 1, 3.2V)$ to 5.5V     |     | 0.15                          |     | %/V               |

| Load Regulation          | I <sub>OUT</sub> = 10mA to IMAX <sup>©</sup>          |     | 0.0017                        |     | %/mA              |

| Power Good Threshold     | V <sub>OUT</sub> Rising                               |     | 93                            |     | %V <sub>NOM</sub> |

| Power Good Hysteresis    | V <sub>OUT</sub> Falling                              |     | 2                             |     | %V <sub>NOM</sub> |

| Os sillatas Essanas      | $V_{OUT} \ge 20\%$ of $V_{NOM}$                       | 1.8 | 2                             | 2.2 | MHz               |

| Oscillator Frequency     | V <sub>OUT</sub> = 0V                                 |     | 500                           |     | kHz               |

| Soft-Start Period        |                                                       |     | 400                           |     | μs                |

| Minimum On-Time          |                                                       |     | 75                            |     | ns                |

| REG1                     | ·                                                     |     |                               |     |                   |

| Maximum Output Current   |                                                       | 0.9 |                               |     | А                 |

| Current Limit            |                                                       | 1.2 | 1.4                           | 1.7 | А                 |

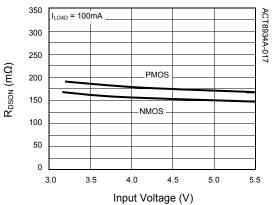

| PMOS On-Resistance       | I <sub>SW1</sub> = -100mA                             |     | 0.18                          |     | Ω                 |

| NMOS On-Resistance       | I <sub>SW1</sub> = 100mA                              |     | 0.16                          |     | Ω                 |

| SW1 Leakage Current      | V <sub>VP1</sub> = 5.5V, V <sub>SW1</sub> = 0 or 5.5V |     | 0                             | 1   | μA                |

| REG2                     | ·                                                     |     |                               |     |                   |

| Maximum Output Current   |                                                       | 0.7 |                               |     | А                 |

| Current Limit            |                                                       | 0.9 | 1.1                           | 1.3 | А                 |

| PMOS On-Resistance       | I <sub>SW2</sub> = -100mA                             |     | 0.21                          |     | Ω                 |

| NMOS On-Resistance       | I <sub>SW2</sub> = 100mA                              |     | 0.16                          |     | Ω                 |

| SW2 Leakage Current      | V <sub>VP2</sub> = 5.5V, V <sub>SW2</sub> = 0 or 5.5V |     | 0                             | 1   | μA                |

| REG3                     | ·                                                     |     |                               |     |                   |

| Maximum Output Current   |                                                       | 0.9 |                               |     | А                 |

| Current Limit            |                                                       | 1.2 | 1.4                           | 1.7 | А                 |

| PMOS On-Resistance       | I <sub>SW3</sub> = -100mA                             |     | 0.18                          |     | Ω                 |

| NMOS On-Resistance       | I <sub>SW3</sub> = 100mA                              |     | 0.16                          |     | Ω                 |

| SW3 Leakage Current      | V <sub>VP3</sub> = 5.5V, V <sub>SW3</sub> = 0 or 5.5V |     | 0                             | 1   | μA                |

$\bigcirc$ : V<sub>NOM</sub> refers to the nominal output voltage level for V<sub>OUT</sub> as defined by the *Ordering Information* section.

2: IMAX Maximum Output Current.

# LOW-NOISE LDO ELECTRICAL CHARACTERISTICS

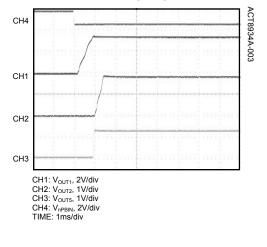

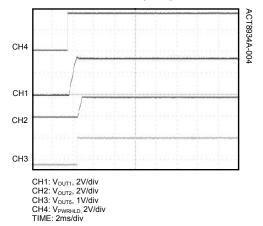

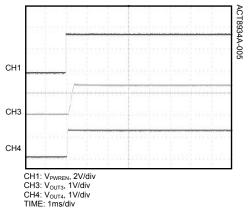

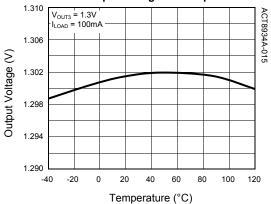

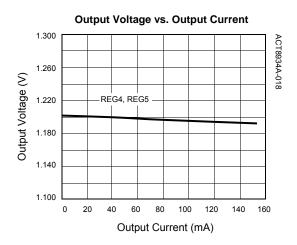

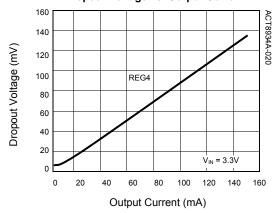

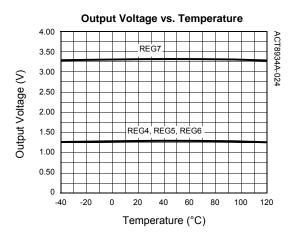

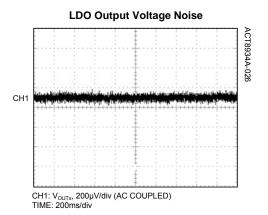

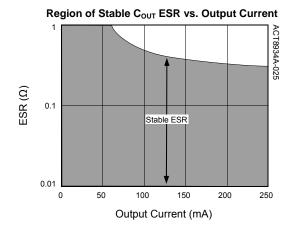

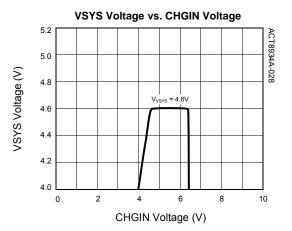

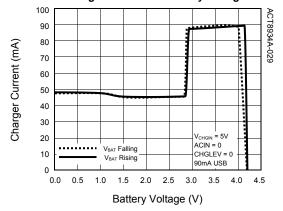

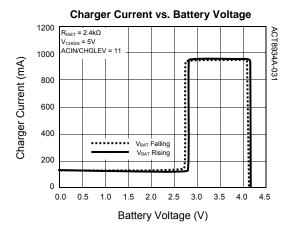

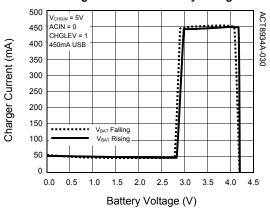

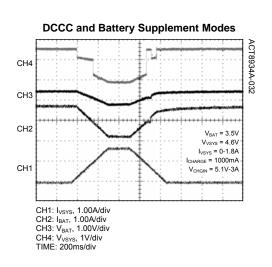

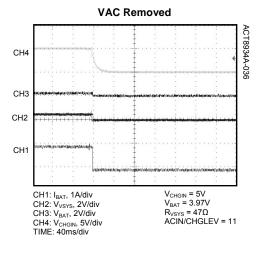

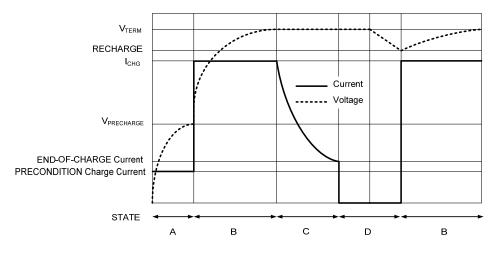

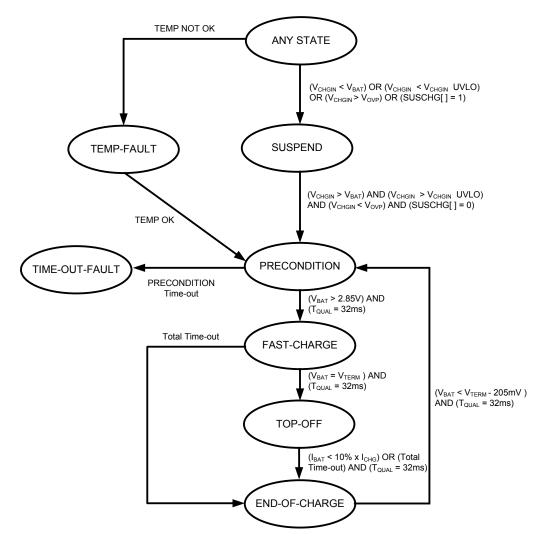

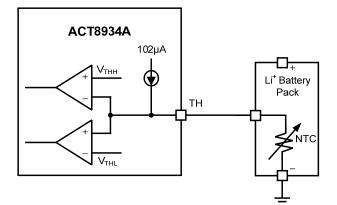

$(V_{INL} = 3.6V, C_{OUT4} = C_{OUT5} = 1.5\mu F, C_{OUT6} = C_{OUT7} = 2.2\mu F, LOWIQ[] = [0], T_A = 25^{\circ}C, unless otherwise specified.)$